Cadence Allegro Sigrity 16.62 | 2.8 Gb

Cadence Design Systems, Inc. released an updated version Cadence Sigrity 6.62, with technologies provide the signal integrity and power analysis solutions needed for system-level verification and interface compliance.

Increases in IC speed, faster data transmission rates, smaller geometries, and an emphasis on optimization have made power and signal integrity issues tightly connected. To address these issues, designers need advanced power integrity and power-aware signal integrity tools. This level of technology allows designers to see the complete picture and achieve signoff-level verification through their analysis. Mistakes are not an option on projects this advanced, that's why designers choose proven Sigrity solutions, from Cadence.

By adopting Sigrity solutions, designers can perform three major tasks of the design verification process:

- Analyze the complete power delivery system across chips, packages, and boards.

- Perform system-level signal integrity (SI) analysis, including simultaneous switching noise analysis of high-speed signal transmissions.

- Utilize the advanced physical design tools for single and multi-chip packages, state-of-the-art 3D packages, and systems-in-package (SiPs).

What’s New in 16.62

ASIS 16.62 introduces three new products to the Allegro Sigrity Product Line:

- Allegro Sigrity PI Base

The Allegro Sigrity PI Base is a complement to the Allegro Sigrity SI Base (PA5700) in that it utilizes the Allegro canvas for viewing and casual editing of Allegro PCB, Package, or SiP files. PI Base provides first order Power Integrity checks to be performed. The tool is meant to be used either by designers who need to seek guidance during the layout process, or by Power Integrity experts, who need a quick answer, and understand the confidence level that can be applied with the first-order analysis.

- Allegro Sigrity Signoff and Optimization Option

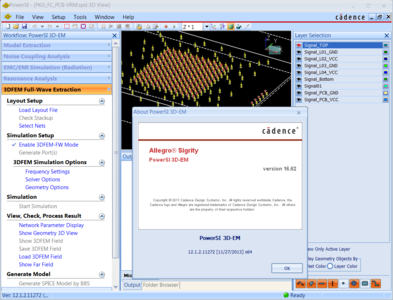

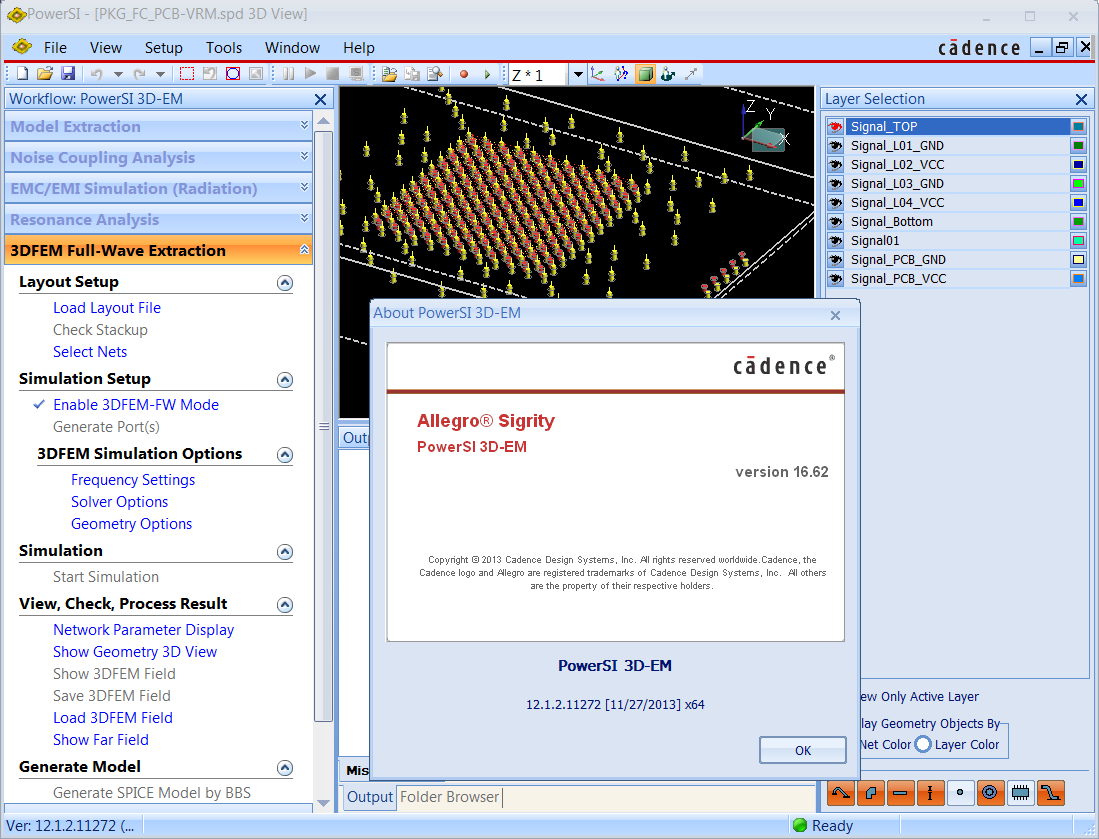

The Allegro Sigrity Power Integrity Signoff and Optimization Option integrates with PI Base to provide expert-level power integrity analysis on top of an editing canvas that allows for the design to be changed and reanalyzed in an integrated fashion. This Option includes the ability to run all of these Sigrity tools (one at a time) either directly from the PI Base (PA5800) or as a point tool: PowerDC, OptimizePI, PowerSI, 3D-EM, CAD Translators

- IO-SSO Analysis Suite

The IO-SSO Analysis Suite is a specific group of model creation and analysis tools that provides the ability to accurately simulate a group of parallel bus nets that are switching simultaneously. For example, a DDR3 data bus could have as many as 64 simultaneous switching signals. The noise on the power and ground planes, known as simultaneous switching noise (SSN), must be accurately characterized to understand if the data will always be reliable. This suite of tools provides all the functionality required for modeling chip, package, and PCB from die to die. The simulation tool provided understands modern memory interface protocols (such as DDR3/DDR4) and points out violations to the electrical specification for those standard protocols. This Suite includes the ability to run all of these Sigrity tools (one at a time) as a point tool: T2B, XcitePI Extraction, XtractIM, PowerSI, Broadband SPICE, SystemSI – PBA, CAD Translators

DATE: 12-19-2013 HOTFIX VERSION: 002

=============================================================================================================

CCRID PRODUCT PRODUCTLEVEL2 TITLE

==============================================================================================================

1202290 SPEED2000 ENG_SPDSIM Fixed Ў°Bad Trace File errorЎ± in FCC display

1207563 SPEED2000 ENG_SPDGEN Fixed an issue that coupled nets and differential impedance is not reported In Trace Impedance/Coupling Checks

1211328 SPEED2000 GUI_SPDGEN Fixed a bug in assigning capacitor model process

1209588 SPEED2000 GUI_SPDSIM Fixed a bug that show an Inadequate Class-A line under Periodical signal radiation mode

1209950 SPEED2000 ENG_SPDSIM Fixed a crash problem which occurs for S-parameter with only one frequency point

1205951 POWERSI ENG PowerSI hangs up at Preprocessing

1196744 POWERSI GUI Merging issue

1211736 POWERSI ENG PowerSI simulation stucks at "generating trace circuits

1209935 POWERSI ENG PowerSI crashes due to ports defined on the die side

1209458 POWERSI ENG PowerSI - Simulation error at frequency 5.623 KHz

T2B Fine tuned I-V curve voltage range for ISSO_*

T2B Allow user set UIC option

T2B Fixed a bug on waveform resampling when windowing

1210685 ASI_PI GUI User can't edit padstack in PowerDC-lite

1207843 ASI_PI SPDIF PI Base: "Split vias into several 2-layer vias" option is checked automatically

1205263 ASI_PI SPDIF PI Base: Cannot find target file in translation process

1198829 XTRACTIM ENG Unreasonable change of results when turning on "coplanar traces coupling with field domain"

1217734 POWERDC ENG_ELECTRICAL Enable both "Treat pad as shape" and "Circuit Pin Size" would use up computer memory and crash computer

1186581 POWERDC ENG_THERMAL PowerDC thermal results are near absolute zero

1203499 POWERDC ENG_ELECTRICAL Wrong results when adding VRM sense line

1213576 POWERDC GUI_ELECTRICAL IR Drop Simulated value changes Worst to Avg delta V in block diagram report

1201173 POWERDC ENG_THERMAL PowerDC crashed when add exact mesh areas in attached case

1205755 POWERDC GUI_ELECTRICAL PowerDC TCL does not record deleting an interconnect

1208115 TRANSLATOR PADS2SPD PADS2SPD crashes on ill-defined padstacks

=============================================================================================================

CCRID PRODUCT PRODUCTLEVEL2 TITLE

==============================================================================================================

1202290 SPEED2000 ENG_SPDSIM Fixed Ў°Bad Trace File errorЎ± in FCC display

1207563 SPEED2000 ENG_SPDGEN Fixed an issue that coupled nets and differential impedance is not reported In Trace Impedance/Coupling Checks

1211328 SPEED2000 GUI_SPDGEN Fixed a bug in assigning capacitor model process

1209588 SPEED2000 GUI_SPDSIM Fixed a bug that show an Inadequate Class-A line under Periodical signal radiation mode

1209950 SPEED2000 ENG_SPDSIM Fixed a crash problem which occurs for S-parameter with only one frequency point

1205951 POWERSI ENG PowerSI hangs up at Preprocessing

1196744 POWERSI GUI Merging issue

1211736 POWERSI ENG PowerSI simulation stucks at "generating trace circuits

1209935 POWERSI ENG PowerSI crashes due to ports defined on the die side

1209458 POWERSI ENG PowerSI - Simulation error at frequency 5.623 KHz

T2B Fine tuned I-V curve voltage range for ISSO_*

T2B Allow user set UIC option

T2B Fixed a bug on waveform resampling when windowing

1210685 ASI_PI GUI User can't edit padstack in PowerDC-lite

1207843 ASI_PI SPDIF PI Base: "Split vias into several 2-layer vias" option is checked automatically

1205263 ASI_PI SPDIF PI Base: Cannot find target file in translation process

1198829 XTRACTIM ENG Unreasonable change of results when turning on "coplanar traces coupling with field domain"

1217734 POWERDC ENG_ELECTRICAL Enable both "Treat pad as shape" and "Circuit Pin Size" would use up computer memory and crash computer

1186581 POWERDC ENG_THERMAL PowerDC thermal results are near absolute zero

1203499 POWERDC ENG_ELECTRICAL Wrong results when adding VRM sense line

1213576 POWERDC GUI_ELECTRICAL IR Drop Simulated value changes Worst to Avg delta V in block diagram report

1201173 POWERDC ENG_THERMAL PowerDC crashed when add exact mesh areas in attached case

1205755 POWERDC GUI_ELECTRICAL PowerDC TCL does not record deleting an interconnect

1208115 TRANSLATOR PADS2SPD PADS2SPD crashes on ill-defined padstacks

About Cadence Design Systems, Inc.

Cadence enables global electronic design innovation and plays an essential role in the creation of today's integrated circuits and electronics. Customers use Cadence software, hardware, IP, and services to design and verify advanced semiconductors, consumer electronics, networking and telecommunications equipment, and computer systems. The company is headquartered in San Jose, Calif., with sales offices, design centers, and research facilities around the world to serve the global electronics industry.

About Sigrity

Sigrity develops and globally supports advanced software analysis solutions to ensure power integrity and signal integrity in chips, packages and printed circuit boards; and physical design tools for single die and SiP implementations. Over 250 companies utilize Sigrity products as part of industry standard design flows and with layout tools from Cadence, Mentor Graphics, Zuken and other EDA suppliers. Sigrity solutions help companies overcome design challenges to reduce costly respins and get to market faster.

Over 60% of Sigrity's 100+ employees are in research and development positions creating breakthrough solutions targeting real-world challenges.

visit my blog

Name: Cadence Allegro Sigrity

Version: 16.62.002

Home: www.cadence.com

Interface: english

OS: Windows Seven / 8

System Requirements: Preinstall Cadence SPB 16.60.016 or above

Size: 2.8 Gb

Help for Recovery Volumes (.rev): www.winrar.com/Help/

All parts on filepost.com, keep2share.cc, rapidgator.com, luckyshare.net interchanged. It is added by 5% of the overall size of the archive of information for the restoration and the volume for the restoration

No mirrors please

No mirrors please