Cadence Sigrity 2019 HF005 Linux | 15.4 Gb

Cadence Design Systems, Inc., a leader in global electronic design innovation, is pleased to announce the availability of Sigrity 2019 HF005 (19.00.005) is a supplier of software for IC package physical design and for analyzing power integrity and signal integrity.

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––-

CCRID Product Title

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––-

2290067 ASI_SI SPDIF does not correctly translate the latest deferred mode SiP files with degassing holes

2422661 ASI_SI Mirrored rounded/chamfered rectangle pad turns to a rectangular pad on the bottom layer

2435057 ASI_SI PowerDC exits unexpectedly while importing a 34-layer BRD file; SPDLinks generates the spd file

2350431 OPTIMIZEPI Error code 3221226356 is being generated by OptimizePI

2410051 OPTIMIZEPI OptimizePI report and impedance plot are different in Sigrity 2018 and Sigrity 2019 releases

2361261 POWERDC Probe voltage at sense point differs from sense voltage in VRM setup

2406153 POWERDC An error message is generated while assigning nodes to VRM positive/negative pins

2423548 POWERDC High current density issue occurs around vias

2357124 SIGRITY_SUITE Clarity translation causes the antipad to appear as a hole or void

2361745 SIGRITY_SUITE PowerSI cannot save the padstack parameters in the .spd file

2348411 XTRACTIM Cap results are missing when using the 'sigrity::apply PerpinCombineCaps {1}' TCL command

2348941 XTRACTIM The -bind argument of the 'add Layer' TCL command does not work correctly

2364498 XTRACTIM XtractIM does not solve EPA by nets and pins in batch mode

CCRID Product Title

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––-

2290067 ASI_SI SPDIF does not correctly translate the latest deferred mode SiP files with degassing holes

2422661 ASI_SI Mirrored rounded/chamfered rectangle pad turns to a rectangular pad on the bottom layer

2435057 ASI_SI PowerDC exits unexpectedly while importing a 34-layer BRD file; SPDLinks generates the spd file

2350431 OPTIMIZEPI Error code 3221226356 is being generated by OptimizePI

2410051 OPTIMIZEPI OptimizePI report and impedance plot are different in Sigrity 2018 and Sigrity 2019 releases

2361261 POWERDC Probe voltage at sense point differs from sense voltage in VRM setup

2406153 POWERDC An error message is generated while assigning nodes to VRM positive/negative pins

2423548 POWERDC High current density issue occurs around vias

2357124 SIGRITY_SUITE Clarity translation causes the antipad to appear as a hole or void

2361745 SIGRITY_SUITE PowerSI cannot save the padstack parameters in the .spd file

2348411 XTRACTIM Cap results are missing when using the 'sigrity::apply PerpinCombineCaps {1}' TCL command

2348941 XTRACTIM The -bind argument of the 'add Layer' TCL command does not work correctly

2364498 XTRACTIM XtractIM does not solve EPA by nets and pins in batch mode

Cadence Sigrity provides a rich set of gigabit signal and power network analysis technologies, including a unique power-aware signal integrity analysis capability for system, printed circuit board (PCB), and IC package designs. The combination of Sigrity analysis technologies with Cadence Allegro and OrCAD design tools will provide a comprehensive front-to-back integrated flow to enable system and semiconductor companies to deliver high-performance devices employing gigabit interface protocols such as DDR and PCI Express. The integrated solution will particularly benefit customers delivering electronic systems in high-growth markets such as mobile multimedia devices and cloud computing infrastructure.

Cadence Sigrity: How to Avoid Power Delivery Problems in your PCBs

Ensure uniform current density in your design and put a stop to the additional time and money spent on troubleshooting hard to find power delivery network issues in the lab with Allegro In-Design Analysis powered by Sigrity.

Cadence is a pivotal leader in electronic systems design, building upon more than 30 years of computational software expertise. The company applies its underlying Intelligent System Design strategy to deliver software, hardware and IP that turn design concepts into reality. Cadence customers are the world’s most innovative companies, delivering extraordinary electronic products from chips to boards to complete systems for the most dynamic market applications, including hyperscale computing, 5G communications, automotive, mobile, aerospace, consumer, industrial and healthcare. For eight years in a row, Fortune magazine has named Cadence one of the 100 Best Companies to Work.

Owner: Cadence Design Systems

Product Name: Sigrity

Version: 2019 HF005 (19.00.005)

Supported Architectures: x86_64

Website Home Page : www.cadence.com

Languages Supported: english

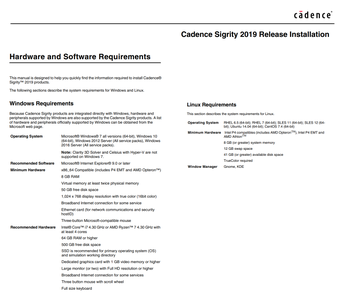

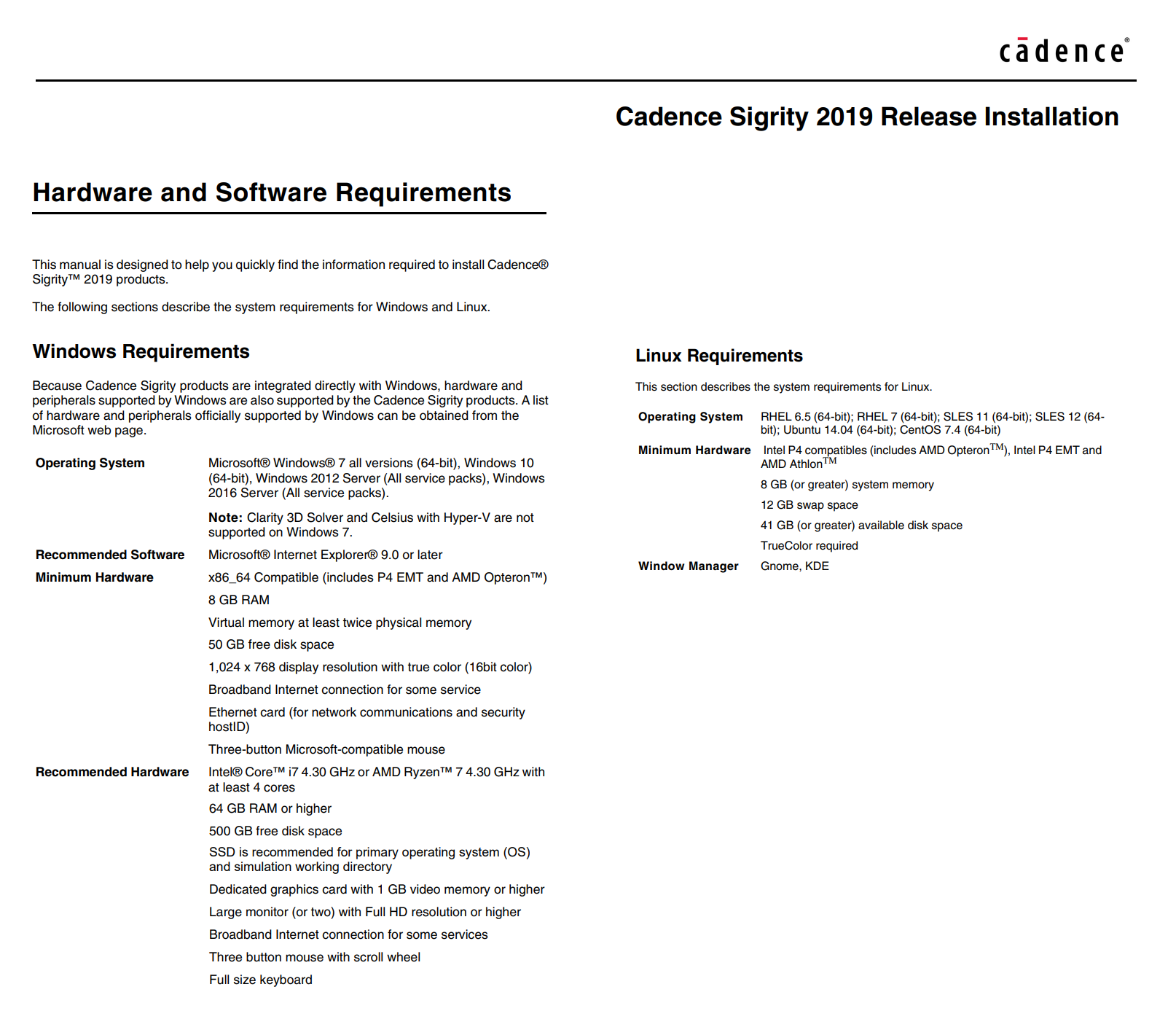

System Requirements: Linux *

Size: 15.4 Gb

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please