Cadence Sigrity and Systems Analysis 2022.1 HF004 | 6.6 Gb

Cadence Design Systems, Inc., a leader in global electronic design innovation, is pleased to announce the availability of Sigrity and Systems Analysis 2022.1 HF004 (22.10.400) is a supplier of software for IC package physical design and for analyzing power integrity and signal integrity.

Sigrity and Systems Analysis 2022.1 HF004 (22.10.400) Release notes - Date: 12-21-2022

–––––––––––––––––––––––––––––––––––––––––––-

CCRID Product Title

–––––––––––––––––––––––––––––––––––––––––––-

2726999 BROADBAND_SPICE S-parameter model checker: Passivity and causality report from any file

2718214 CELSIUS Mapping relationship issue occurs in the vertical .cfd file

2647312 CLARITY The airbox is different when using parametric import and non-parametric import in Clarity 3D Workbench

2653811 CLARITY Standard volume/surface seeding has no impact on mesh

2686605 CLARITY Clarity 3D Layout gets stuck in the AFS stage

2704441 CLARITY Clarity AFS0 is not efficient

2712819 CLARITY Optimality simulation stopped with an error for a 16 parameters case

2722868 CLARITY Clarity 3D Workbench quasi static solver succeeds in 3D inductance extraction but fails in sweeping mode

2731236 CLARITY S-parameter results are not correct for one signal net

2733867 CLARITY Parametric import in Clarity 3D Workbench does not preserve metal shapes

2734558 CLARITY Low frequency sweep is failing in Clarity

2741029 CLARITY Unnecessary license checkouts cause LMESH to fail on AWS using HF3

2729682 OPTIMIZEPI The EMI Optimization option remains disabled despite complete setup

2722499 POWERDC Applying the PowerTree topology in PowerDC does not complete the PowerTree application wizard

2728437 POWERDC Using the Tcl command DisplaNodesOnCircuitNodePads causes the GUI to exit unexpectedly

2728449 POWERDC The Tcl command DisplaNodesOnCircuitNodePads shows nodes inside vias

2709420 POWERSI Frequency sampling is incorrect from the DCfitted_customized model

2722007 POWERSI Capacitor model assignment error occurs in PowerSI

2723559 POWERSI PowerSI exits unexpectedly during shape processing

2734811 POWERSI DC_Fitted snp output file is missing in PDN Extraction using PowerSI

2693519 SIGRITY_SUITE Fanout routing moves to other layer when swept in Clarity 3D Layout HSSO flow

2706495 SIGRITY_SUITE XtractIM produces different mapping file starting from Sigrity2022.1 HF2

2727959 SIGRITY_SUITE Pad Stack window in PowerSI does not display correctly

2730550 SIGRITY_SUITE The port generation flow for multiterminal circuits in Clarity 3D Layout does not generate the S-parameter results

2730949 SIGRITY_SUITE Failed to check port connection error occurs in Clarity 3D Layout when the Cut & Stitch method is used

2737253 SPEED2000 SPEEDEM failed to read IBIS model

2682592 TRANSLATOR Pads are missing after translation

2741685 TRANSLATOR Change in padstack names when importing .tgz file into PowerSI

CCRID Product Title

–––––––––––––––––––––––––––––––––––––––––––-

2726999 BROADBAND_SPICE S-parameter model checker: Passivity and causality report from any file

2718214 CELSIUS Mapping relationship issue occurs in the vertical .cfd file

2647312 CLARITY The airbox is different when using parametric import and non-parametric import in Clarity 3D Workbench

2653811 CLARITY Standard volume/surface seeding has no impact on mesh

2686605 CLARITY Clarity 3D Layout gets stuck in the AFS stage

2704441 CLARITY Clarity AFS0 is not efficient

2712819 CLARITY Optimality simulation stopped with an error for a 16 parameters case

2722868 CLARITY Clarity 3D Workbench quasi static solver succeeds in 3D inductance extraction but fails in sweeping mode

2731236 CLARITY S-parameter results are not correct for one signal net

2733867 CLARITY Parametric import in Clarity 3D Workbench does not preserve metal shapes

2734558 CLARITY Low frequency sweep is failing in Clarity

2741029 CLARITY Unnecessary license checkouts cause LMESH to fail on AWS using HF3

2729682 OPTIMIZEPI The EMI Optimization option remains disabled despite complete setup

2722499 POWERDC Applying the PowerTree topology in PowerDC does not complete the PowerTree application wizard

2728437 POWERDC Using the Tcl command DisplaNodesOnCircuitNodePads causes the GUI to exit unexpectedly

2728449 POWERDC The Tcl command DisplaNodesOnCircuitNodePads shows nodes inside vias

2709420 POWERSI Frequency sampling is incorrect from the DCfitted_customized model

2722007 POWERSI Capacitor model assignment error occurs in PowerSI

2723559 POWERSI PowerSI exits unexpectedly during shape processing

2734811 POWERSI DC_Fitted snp output file is missing in PDN Extraction using PowerSI

2693519 SIGRITY_SUITE Fanout routing moves to other layer when swept in Clarity 3D Layout HSSO flow

2706495 SIGRITY_SUITE XtractIM produces different mapping file starting from Sigrity2022.1 HF2

2727959 SIGRITY_SUITE Pad Stack window in PowerSI does not display correctly

2730550 SIGRITY_SUITE The port generation flow for multiterminal circuits in Clarity 3D Layout does not generate the S-parameter results

2730949 SIGRITY_SUITE Failed to check port connection error occurs in Clarity 3D Layout when the Cut & Stitch method is used

2737253 SPEED2000 SPEEDEM failed to read IBIS model

2682592 TRANSLATOR Pads are missing after translation

2741685 TRANSLATOR Change in padstack names when importing .tgz file into PowerSI

Cadence Sigrity provides a rich set of gigabit signal and power network analysis technologies, including a unique power-aware signal integrity analysis capability for system, printed circuit board (PCB), and IC package designs. The combination of Sigrity analysis technologies with Cadence Allegro and OrCAD design tools will provide a comprehensive front-to-back integrated flow to enable system and semiconductor companies to deliver high-performance devices employing gigabit interface protocols such as DDR and PCI Express. The integrated solution will particularly benefit customers delivering electronic systems in high-growth markets such as mobile multimedia devices and cloud computing infrastructure.

Cadence Sigrity accurate signal integrity analysis for PCB

Here we see Cadence Sigrity in action. A thorough sign off tool dealing with signal integrity and power integrity at the PCB and IC Package level.

Cadence enables global electronic design innovation and plays an essential role in the creation of today’s integrated circuits and electronics. Customers use Cadence software, hardware, IP and services to design and verify advanced semiconductors, consumer electronics, networking and telecommunications equipment, and computer systems. The company is headquartered in San Jose, Calif., with sales offices, design centers and research facilities around the world to serve the global electronics industry.

Product: Cadence Sigrity and Systems Analysis

Version: 2022.1 HF004 (22.10.400) Hotfix Only

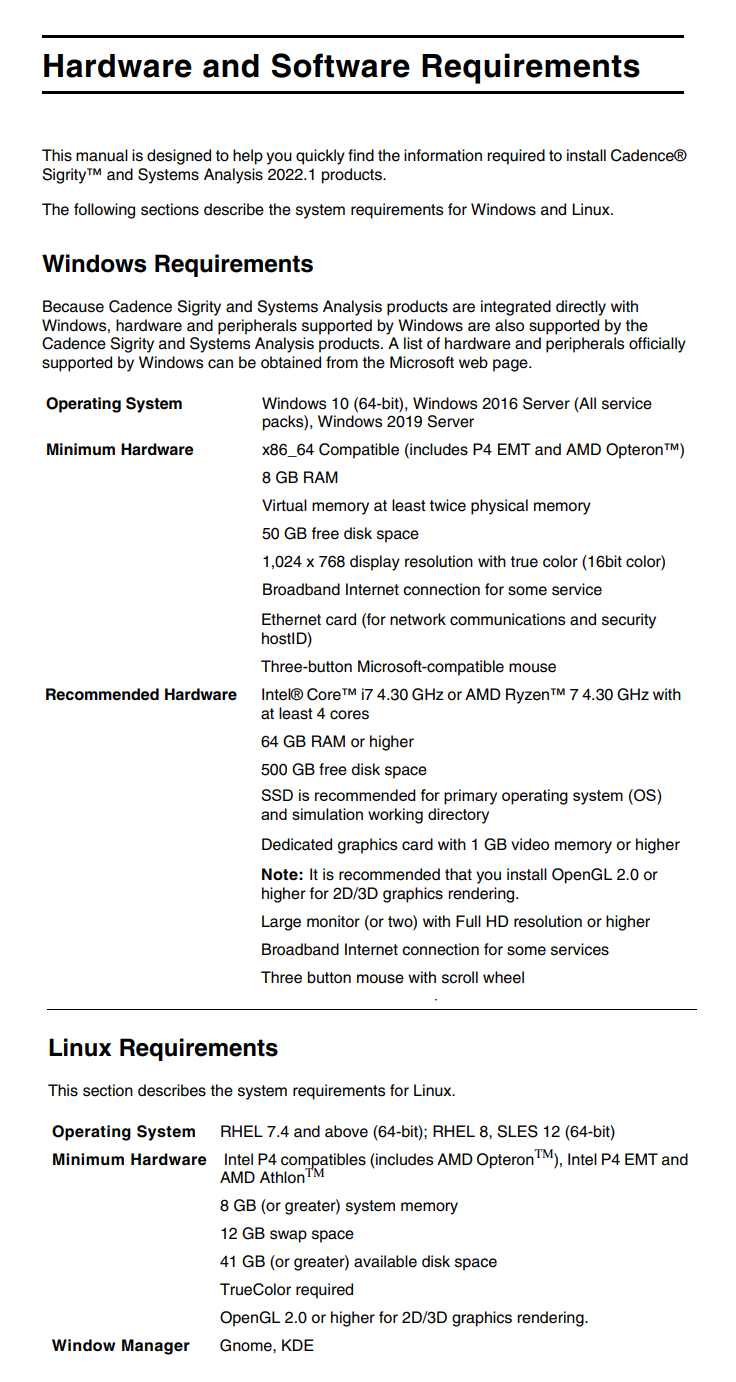

Supported Architectures: x64

Website Home Page : www.cadence.com

Languages Supported: english

System Requirements: Windows *

Software Prerequisites: Cadence Sigrity and Systems Analysis 2022.0 and above (link bellow)

Size: 6.6 Gb

Cadence Sigrity and Systems Analysis 2022.1 HF002

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please