Siemens Questa Advanced Simulator 2024.1 | 1.2 Gb

Siemens Digital Industries Software introduced Questa Advanced Simulator (SIM) 2024.1 is the core simulation and debug engine of the Questa verification solution; the comprehensive advanced verification platform capable of reducing the risk of validating complex FPGA and SoC designs.

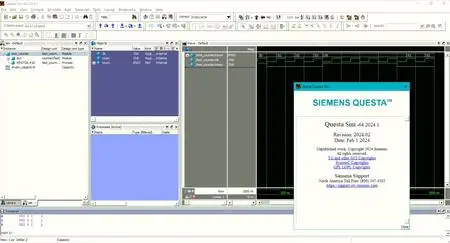

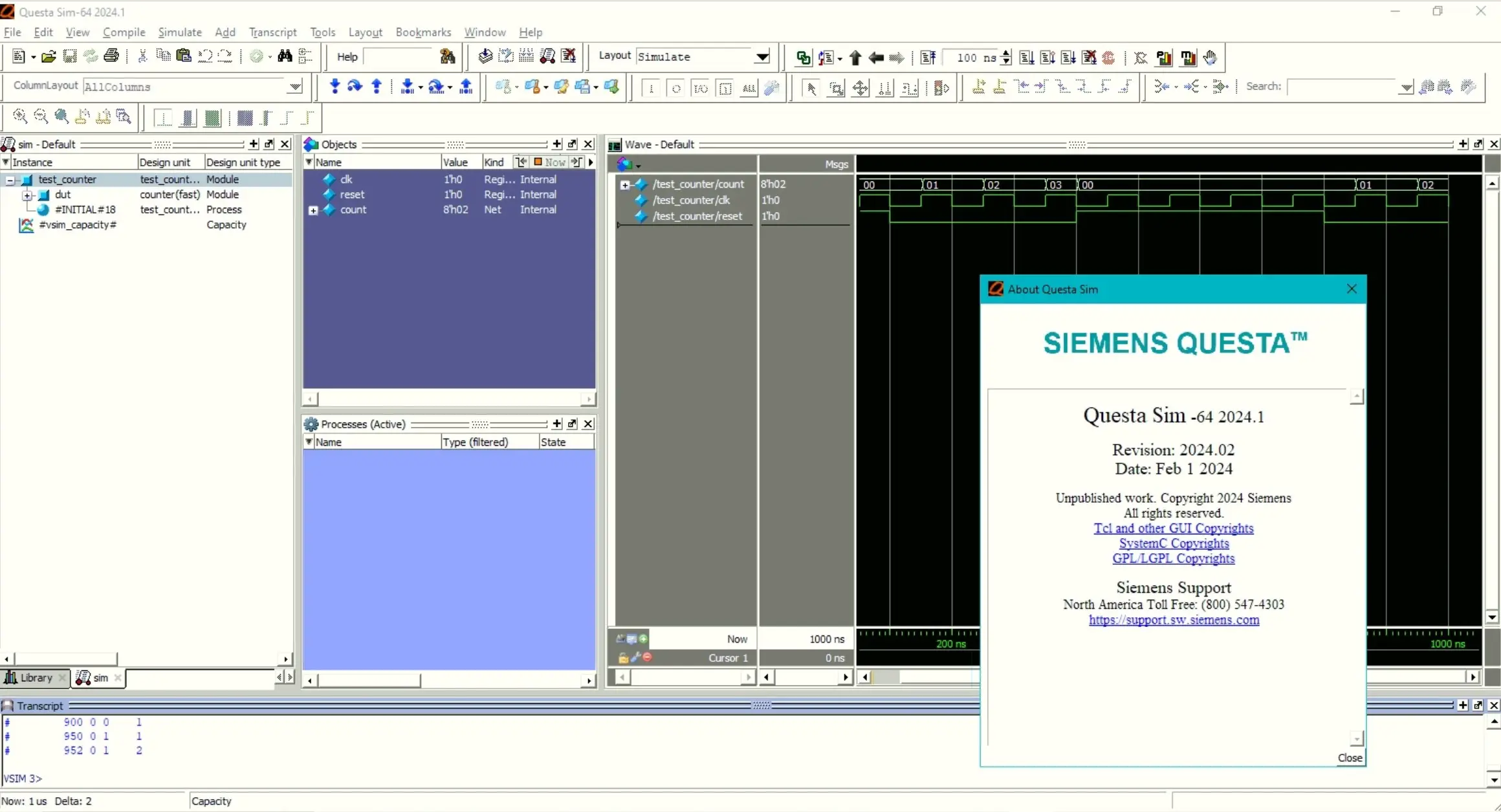

Release Notes for Questa Sim 2024.1 - Date: Feb 01 2024

Release Announcements in 2024.1

- Starting 2024.1, windows 11 is fully supported, in addition to windows 10. However, in 2025.1 release, windows 10 support will be dropped.

General Defects Repaired in 2024.1

- QSIM-81937 - (source) fixed the issue of vopt crash while adding a covergroup to a checker.

- QSIM-79644 - (source, results)

Changed PDI FSDB dumping so that modports and wreals are NOT logged by default. This make the default PDI FSDB logging compatible with Novas -pli based logging.

Now in order to log wreals with PDI FSDB logging, use the +fsdb+wreal[=on|off] vsim command line switch or the +wreal option for the fsdbDumpvars or fsdbDumpMDA commands.

Now in order to log modports with PDI FSDB logging, use the +fsdb+modport[=on|off] vsim command line switch or the +modport option for the fsdbDumpvars or fsdbDumpMDA commands.

Note these are all non-standard options that are NOT supported by Novas.

- QSIM-85893 - Unconnected ports due to empty explicit named port connection ( eg: .portname() ) will be reported with a warning in vopt, when command line switch -warn_explicit_empty_named_port_conn used.

User Interface Defects Repaired in 2024.1

- VISU-37936 - (source, results) The dialog box raised when a source file is modified while opened in the source window would consume 100% of the CPU if it was not responded to for an extended period of time.

- VISU-40187 - Fixed an issue where internal Power Aware files were listed in the results of the Search Files window

- VISU-37316 - Fixed an issue where the Signal Clipboard was missing part of the signal hierarchy path when a signal was added to the clipboard.

- QSIM-81740 - (source) The deprecated vsim SystemVerilog constrained random extension "geninitialseedfix" (-svrandext=geninitialseedfix) has been removed.

SystemVerilog Defects Repaired in 2024.1

- QSIM-82637 - vsim would sometimes crash during elaboration due to specialized classes with virtual interface fields.

- QSIM-73007 - (results) In some rare cases, a randomize() call via super.randomize() or class_name::randomize() would register the constraint(s) of a derived class instead of the specified class, resulting in incorrect randomize() behavior. This issue has been fixed.

- QSIM-83008 - (results) In some rare cases, randomize() would generate a solution that contradicts one or more !inside constraints. This issue has been fixed.

- QSIM-82862 - (results) In some rare cases involving multiple 'dist' constraints on a common LHS, randomize() would generate a solution that contradicts one or more of the specified 'dist' constraints.This issue has been fixed.

- QSIM-73006 - Previous versions of Questa did not support a call to randomize() via class_name::randomize() with arguments. This issue has been fixed (arguments are now supported for these types of randomize() calls).

- QSIM-83015 - (results) In some rare cases, randomize() would generate an invalid solution for a scenario involving an iterative constraint on a non-random dynamic array or queue. This issue has been fixed.

- QSIM-83738 - (results) Two identical randomize() calls (having the same random variables and constraints) involving one or more 'soft' constraints, with the same starting randstate, would sometimes generate different solutions (even when -svrandext=strictstab is enabled). This issue has been fixed.

- QSIM-82643 - (results) In some cases, a randomize() call involving a random dynamic array/queue and a "unique" constraint on the same array/queue would spuriously fail due to a constraint contradiction if the solver evaluates the size of the dynamic array/queue to a value that causes the "unique" constraint to become unsatisfiable. This issue has been fixed.

- QSIM-84661 - In some cases, randomize() would report a spurious (vsim-7067) error (Index out of bounds) for a constraint involving a multi-dimensional random dynamic array. This issue has been fixed.

- QSIM-84883 - Significantly improved the performance (>10x) for randomize() calls involving large numbers of 'soft' constraints and 'disable soft' constraints.

- QSIM-84864 - In some rare cases, randomize() would trigger an internal error (slvComputation.c). This issue has been fixed.

- [nodvtid] - In some rare cases, randomize() would generate an invalid solution (a solution that contradicts one or more constraints) related to in-line constraints referring to class handle(s) in the local scope. This issue has been fixed.

- QSIM-84642 - Calling std::randomize() with a hierarchical reference to a SystemC variable would not update the value of the variable with the solution generated during the randomize() call. This issue has been fixed.

- QSIM-84618 - In some rare cases, randomize() would trigger an internal error (slvSolverContext.c) when evaluating in-line constraints referring to class handle(s) in the local scope. This issue has been fixed.

- QSIM-82437 - (results) In some rare cases, randomize() would produce different results between a checkpointed simulation and a non-checkpointed simulation – even when the -svrandext=+strictstab extension is enabled. This issue has been fixed.

- QSIM-84223 - In some rare cases, randomize() would spuriously fail (no solutions / constraint contradiction) for scenarios involving random dynamic arrays that are resized during randomize(). This issue has been fixed.

- QSIM-84218 - In some rare cases, randomize() would perform slowly and/or timeout for a scenario that performed well in Questa versions 2022.1 and earlier. This issue has been fixed.

- QSIM-85114 - Significantly improved the performance of randomize() calls involving large numbers (thousands) of 'soft' constraints for a wide variety of scenarios.

- QSIM-85925 - In some rare cases, randomize() would spuriously fail (no solutions / constraint contradiction) when evaluating a 'unique' constraint with constant 4-state operands. This issue has been fixed.

- QSIM-87029 - (results) In some cases when randomize() fails (i.e. due to a constraint contradiction), the value of some random variables will be incorrectly updated to values that differ from those prior to randomization. This issue has been fixed.

- QSIM-86814 - (results) In some rare cases, randomize() would generate a solution that violates one or more conditional (predicated) constraints. This issue has been fixed.

- QSIM-86636 - Fixed a performance issue for some randomize() calls involving iterative equality constraints and large random unpacked arrays.

- QSIM-86505 - (results) When vlog/vopt -svext=pathseed is enabled (enable unique seeding of module instances based on hierarchical path name) instances of a module containing a continuous assignment involving $urandom (on the RHS of the assignment) would incorrectly be seeded with the same seed. This issue has been fixed.

- QSIM-86269 - (results) In some rare cases, randomize() would generate an invalid solution due to the incorrect evaluation of a constraint involving a random variable having "rand_mode" set to 0 whos value changes within the context of a pre_randomize() function. This issue has been fixed.

- QSIM-85847 - In some cases, randomize() would cause a crash during simulation if qwavedb logging is enabled and the solver is evaluating a random associative array having 'string' type indices. This issue has been fixed.

- QSIM-85726 - In some rare cases, randomize() would crash when evaluating a scenario involving a 'dist' constraint when -solvefaildebug=2 is enabled. This issue has been fixed.

- QSIM-87637 - In some cases, randomize() would cause a crash when evaluating an ill-formed constraint "x < y < z" where "x", "y" and "z" are real-type random variables. This issue has been fixed.

VHDL Defects Repaired in 2024.1

- QSIM-82053 - When a generic is of null array type and is mapped to an empty string literal in certain situations, a vsim crash is obtained. This has been fixed.

- QSIM-82072 - Tick_HIGH attribute when used on empty string, used to give error in simulation. This has been fixed.

- QSIM-81354 - Tick_Subtype attribute when used on more than one dimension, used to give error or wrong_value in simulation in some versions of Questa. This has been fixed.

- QSIM-82040 - Protected type array variable whose index expression depends on non protected type constant record member, used to get created with incorrect size. This has been fixed.

- QSIM-82247 - For some specific cases where functions and procedures have the same function arguments, vcom used to throw an error. This has been fixed.

- QSIM-84383 - If a during optimize, we compute a variable of type std.textio.line and then index or slice that variable, incorrect data will be generated. This can result in incorrect constants being generated at elaboration time. More often than not will will be a some number of NULL characters followed by random characters. If a string containing NULL characters is send to the transcript, like the in a report statement. The string will be pre-maturely terminated at the first NULL. The fix is to generate the correct value for the slice and index in such cases.

- QSIM-82837 - (results) Long compile and vopt times could occur if to many statements occurred on the same line of the file or if the large number of statememts were encrypted. Note that default label generation has changed slightly to be more consistent. All default labels on the same line will be unique. The scope the label was created in is no longer important.

- QSIM-84450 - A variable assigned to from within a loop could be ignored if the assign is done using an aggregate as the target.

- QSIM-84301 - Variable assignments within loops could be ignored if the variable is assign to through an aggregate.

[nodvtid] - When FSM detection is enable the tool would crash if a process had subprogram calls to a subprogram instance. The fix is to not allow processes with subprogram instance calls to be a FSM.

[nodvtid] - In some cases when assigning to a slice of a signal that is a NULL array, an error would be reported incorrectly. The message would say the whole signal, not the slice, is not the same length as the NULL array being assigned to it.

- QSIM-85055 - Vcom would crash when autoorder is being used if an entity that doesn't currently exist in a library is reference in a configuration specification and the entity has been made directly visible by a use statement. Example:

library lib1;

use lib1.entity1;

architecture rtl of some_entity is

component c is end component;

for all:c use entity entity1;

- QSIM-85121 - Aliases to external names in subprograms may have incorrect signal attributes like last_value.

- QSIM-85149 - If a hierarchical reference is used in a port connection and the reference is to a signal that is an alias of an alias or an alias to a port that has been collapsed due to optimization. The reference would fail to find the object and report an error.

- QSIM-85747 - Using 'element on a array type with more than one dimension would result in an incorrect result.

- QSIM-85768 - When using auto order. If an entity name reference in a direct instantiation matches the name of another identifier, an incorrect error will be reported. This can occur at the direct instantiation or some other location where the matching identifier is used.

[nodvtid] - If a design unit contains a large number of expression that consist of real literals and implicit operations like -3.0 or 3.0/1.0, vcom performance would be very slow. This slow down has been resolved.

- QSIM-85958 - The -g/-G options when specifying more that just the generic name does not propagate to changes in port width in all cases.

- QSIM-86167 - Calls to an protected method could crash if an argument to the method is also a protected type method call and that call is not the form protected_object.portected_method( …)

- QSIM-87189 - In VHDL 2008, when using the value <> for the default value of an interface subprogram, we could fail to find an actual subprogram if the formal for the interface subprogram was not all lower case.

- QSIM-87124 - Vopt could generate bad machine code for package references resulting in a crash during elaboration in vsim.

- QSIM-84038 - In some cases, logging a n-dimensional array of std_logic would cause a crash if length of a dimension was 1 and the total number of scalar elements at that dimension was 1.

- QSIM-81420 - VSIM was crashing while trying to use type/subtype or generic procedure from package instance in certain situations. This has been fixed now.

- QSIM-84543 - Null range in record signals wasn't handled properly. This has been fixed.

Mixed Language Defects Repaired in 2024.1

- QSIM-84122 - When Verilog configurations are used on a VHDL design unit. It can cause a default binding to report an error about missing generics or ports on the entity selected. This error was incorrect and misleading because the generics or ports of the component and default entity were legal. This problem has been fixed and the error message about default binding failure has been enhance to include the actual entity selected and the reason why.

- QSIM-86090 - Forcing a slice of a hierarchical reference that resolves to a VHDL signal had no effect. The force is now correctly applied.

- QSIM-86866 - (results) When using the -mixedsvvh option for packages, real constants were limited to 6 digits after the decimal point. As a results the values of in the other language could be different from the original language. Fix preserves at least 7 digits of accuracy but the values can still differ slightly. This fix requires that the original package either be recompiled or refresh for the change to take effect. Just re-running vopt will have no effect.

- QSIM-86856 - In some cases where VHDL instantiates a System Verilog module either vcom or vopt would generate the error 1136 "Unknown identifier <library name>" if a port or generic was a struct defined originally in a System Verilog package or unit scope. This has been resolved and should not longer occur.

Power Aware Defects Repaired in 2024.1

- QSIM-81341 - Added support for writing out Power State Analysis Report into CSV File, that shows all the Power State Tables fully expanded and hierarchically composed under the vopt option -pa_genrpt=csv_pst

- QSIM-82734 - Added verror for vopt warning "vopt-9555".

- QSIM-84633 - In vsim, user can identify if its a low-power simulation using tcl proc "GetPAMode"

Below example demonstrates how user can use "GetPAMode" in .do file in vism:

if {[GetPAMode]} {

echo "This is A PA simulation"

}

QSIM-85484 - Questa PA will produce a suppressible error, if a power domain is specified in -elements list of UPF command set_design_attributes for an attribute for which power domain is not supported. Error will be reported as:

** Error (suppressible): top.upf(62): UPF: (vopt-9579) Power Domain 'top_domain' in -elements list of set_design_attributes command is currently not supported.

QSIM-85485 - In case of potential conflict between UPF Power Switch ack port driver and RTL, tool will detect the conflict and resolve it during simulation. The resolution is if RTL driver is present after resolution, it will be given preference otherwise UPF ack port driver will be used. This is supported under vopt option -pa_enable=[+]ackportdriver. Under this option, in case of potential conflict, a warning (vopt-9578) will be generated:

** Warning: top.sv(49): (vopt-9578) Ack port ack_p(/tb/instop/multi) has a potential conflict with RTL driver. Conflict will be resolved during simulation.

By default, this option is disabled.

- QSIM-85180 - (results) Source nets of resolved supply nets, which are themselves resolved, will no longer be included in the driving resolved bus.

- QSIM-85115 - Support added for skipping generate block scopes during relative path traversal with the set_scope UPF command. Attempting to access generate block scopes using set_scope command will now result in a vopt-9647 error. These changes will be enabled under the vopt option -pa_upfextensions=genscope

- QSIM-85763 - Behavior of tcl/upf puts command with -nonewline option is now fixed.

- QSIM-85545 - vopt-9022 (output port has no drivers) warning will not be reported for output ports driven via resolved bus.

- QSIM-82306 - Added support for usage of retention supply for source sink analysis if use_retention_as_primary is provided in set_retention command. This will be enabled under vopt option "-pa_enable=[+]retsupplyassrcsink". By default, the option is disabled.

Qwave logging Defects Repaired in 2024.1

- VISU-36540 - In vsim batch mode, users who invoked do scripts with "add wave -group" calls experienced failures in generating the qwavedb file. This issue was fixed and now the -group option is silently ignored, matching Questa's behavior.

- QSIM-81937 - (source) fixed the issue of vopt crash while adding a covergroup to a checker.

- QSIM-79644 - (source, results)

Changed PDI FSDB dumping so that modports and wreals are NOT logged by default. This make the default PDI FSDB logging compatible with Novas -pli based logging.

Now in order to log wreals with PDI FSDB logging, use the +fsdb+wreal[=on|off] vsim command line switch or the +wreal option for the fsdbDumpvars or fsdbDumpMDA commands.

Now in order to log modports with PDI FSDB logging, use the +fsdb+modport[=on|off] vsim command line switch or the +modport option for the fsdbDumpvars or fsdbDumpMDA commands.

Note these are all non-standard options that are NOT supported by Novas.

- QSIM-85893 - Unconnected ports due to empty explicit named port connection ( eg: .portname() ) will be reported with a warning in vopt, when command line switch -warn_explicit_empty_named_port_conn used.

User Interface Defects Repaired in 2024.1

- VISU-37936 - (source, results) The dialog box raised when a source file is modified while opened in the source window would consume 100% of the CPU if it was not responded to for an extended period of time.

- VISU-40187 - Fixed an issue where internal Power Aware files were listed in the results of the Search Files window

- VISU-37316 - Fixed an issue where the Signal Clipboard was missing part of the signal hierarchy path when a signal was added to the clipboard.

- QSIM-81740 - (source) The deprecated vsim SystemVerilog constrained random extension "geninitialseedfix" (-svrandext=geninitialseedfix) has been removed.

SystemVerilog Defects Repaired in 2024.1

- QSIM-82637 - vsim would sometimes crash during elaboration due to specialized classes with virtual interface fields.

- QSIM-73007 - (results) In some rare cases, a randomize() call via super.randomize() or class_name::randomize() would register the constraint(s) of a derived class instead of the specified class, resulting in incorrect randomize() behavior. This issue has been fixed.

- QSIM-83008 - (results) In some rare cases, randomize() would generate a solution that contradicts one or more !inside constraints. This issue has been fixed.

- QSIM-82862 - (results) In some rare cases involving multiple 'dist' constraints on a common LHS, randomize() would generate a solution that contradicts one or more of the specified 'dist' constraints.This issue has been fixed.

- QSIM-73006 - Previous versions of Questa did not support a call to randomize() via class_name::randomize() with arguments. This issue has been fixed (arguments are now supported for these types of randomize() calls).

- QSIM-83015 - (results) In some rare cases, randomize() would generate an invalid solution for a scenario involving an iterative constraint on a non-random dynamic array or queue. This issue has been fixed.

- QSIM-83738 - (results) Two identical randomize() calls (having the same random variables and constraints) involving one or more 'soft' constraints, with the same starting randstate, would sometimes generate different solutions (even when -svrandext=strictstab is enabled). This issue has been fixed.

- QSIM-82643 - (results) In some cases, a randomize() call involving a random dynamic array/queue and a "unique" constraint on the same array/queue would spuriously fail due to a constraint contradiction if the solver evaluates the size of the dynamic array/queue to a value that causes the "unique" constraint to become unsatisfiable. This issue has been fixed.

- QSIM-84661 - In some cases, randomize() would report a spurious (vsim-7067) error (Index out of bounds) for a constraint involving a multi-dimensional random dynamic array. This issue has been fixed.

- QSIM-84883 - Significantly improved the performance (>10x) for randomize() calls involving large numbers of 'soft' constraints and 'disable soft' constraints.

- QSIM-84864 - In some rare cases, randomize() would trigger an internal error (slvComputation.c). This issue has been fixed.

- [nodvtid] - In some rare cases, randomize() would generate an invalid solution (a solution that contradicts one or more constraints) related to in-line constraints referring to class handle(s) in the local scope. This issue has been fixed.

- QSIM-84642 - Calling std::randomize() with a hierarchical reference to a SystemC variable would not update the value of the variable with the solution generated during the randomize() call. This issue has been fixed.

- QSIM-84618 - In some rare cases, randomize() would trigger an internal error (slvSolverContext.c) when evaluating in-line constraints referring to class handle(s) in the local scope. This issue has been fixed.

- QSIM-82437 - (results) In some rare cases, randomize() would produce different results between a checkpointed simulation and a non-checkpointed simulation – even when the -svrandext=+strictstab extension is enabled. This issue has been fixed.

- QSIM-84223 - In some rare cases, randomize() would spuriously fail (no solutions / constraint contradiction) for scenarios involving random dynamic arrays that are resized during randomize(). This issue has been fixed.

- QSIM-84218 - In some rare cases, randomize() would perform slowly and/or timeout for a scenario that performed well in Questa versions 2022.1 and earlier. This issue has been fixed.

- QSIM-85114 - Significantly improved the performance of randomize() calls involving large numbers (thousands) of 'soft' constraints for a wide variety of scenarios.

- QSIM-85925 - In some rare cases, randomize() would spuriously fail (no solutions / constraint contradiction) when evaluating a 'unique' constraint with constant 4-state operands. This issue has been fixed.

- QSIM-87029 - (results) In some cases when randomize() fails (i.e. due to a constraint contradiction), the value of some random variables will be incorrectly updated to values that differ from those prior to randomization. This issue has been fixed.

- QSIM-86814 - (results) In some rare cases, randomize() would generate a solution that violates one or more conditional (predicated) constraints. This issue has been fixed.

- QSIM-86636 - Fixed a performance issue for some randomize() calls involving iterative equality constraints and large random unpacked arrays.

- QSIM-86505 - (results) When vlog/vopt -svext=pathseed is enabled (enable unique seeding of module instances based on hierarchical path name) instances of a module containing a continuous assignment involving $urandom (on the RHS of the assignment) would incorrectly be seeded with the same seed. This issue has been fixed.

- QSIM-86269 - (results) In some rare cases, randomize() would generate an invalid solution due to the incorrect evaluation of a constraint involving a random variable having "rand_mode" set to 0 whos value changes within the context of a pre_randomize() function. This issue has been fixed.

- QSIM-85847 - In some cases, randomize() would cause a crash during simulation if qwavedb logging is enabled and the solver is evaluating a random associative array having 'string' type indices. This issue has been fixed.

- QSIM-85726 - In some rare cases, randomize() would crash when evaluating a scenario involving a 'dist' constraint when -solvefaildebug=2 is enabled. This issue has been fixed.

- QSIM-87637 - In some cases, randomize() would cause a crash when evaluating an ill-formed constraint "x < y < z" where "x", "y" and "z" are real-type random variables. This issue has been fixed.

VHDL Defects Repaired in 2024.1

- QSIM-82053 - When a generic is of null array type and is mapped to an empty string literal in certain situations, a vsim crash is obtained. This has been fixed.

- QSIM-82072 - Tick_HIGH attribute when used on empty string, used to give error in simulation. This has been fixed.

- QSIM-81354 - Tick_Subtype attribute when used on more than one dimension, used to give error or wrong_value in simulation in some versions of Questa. This has been fixed.

- QSIM-82040 - Protected type array variable whose index expression depends on non protected type constant record member, used to get created with incorrect size. This has been fixed.

- QSIM-82247 - For some specific cases where functions and procedures have the same function arguments, vcom used to throw an error. This has been fixed.

- QSIM-84383 - If a during optimize, we compute a variable of type std.textio.line and then index or slice that variable, incorrect data will be generated. This can result in incorrect constants being generated at elaboration time. More often than not will will be a some number of NULL characters followed by random characters. If a string containing NULL characters is send to the transcript, like the in a report statement. The string will be pre-maturely terminated at the first NULL. The fix is to generate the correct value for the slice and index in such cases.

- QSIM-82837 - (results) Long compile and vopt times could occur if to many statements occurred on the same line of the file or if the large number of statememts were encrypted. Note that default label generation has changed slightly to be more consistent. All default labels on the same line will be unique. The scope the label was created in is no longer important.

- QSIM-84450 - A variable assigned to from within a loop could be ignored if the assign is done using an aggregate as the target.

- QSIM-84301 - Variable assignments within loops could be ignored if the variable is assign to through an aggregate.

[nodvtid] - When FSM detection is enable the tool would crash if a process had subprogram calls to a subprogram instance. The fix is to not allow processes with subprogram instance calls to be a FSM.

[nodvtid] - In some cases when assigning to a slice of a signal that is a NULL array, an error would be reported incorrectly. The message would say the whole signal, not the slice, is not the same length as the NULL array being assigned to it.

- QSIM-85055 - Vcom would crash when autoorder is being used if an entity that doesn't currently exist in a library is reference in a configuration specification and the entity has been made directly visible by a use statement. Example:

library lib1;

use lib1.entity1;

architecture rtl of some_entity is

component c is end component;

for all:c use entity entity1;

- QSIM-85121 - Aliases to external names in subprograms may have incorrect signal attributes like last_value.

- QSIM-85149 - If a hierarchical reference is used in a port connection and the reference is to a signal that is an alias of an alias or an alias to a port that has been collapsed due to optimization. The reference would fail to find the object and report an error.

- QSIM-85747 - Using 'element on a array type with more than one dimension would result in an incorrect result.

- QSIM-85768 - When using auto order. If an entity name reference in a direct instantiation matches the name of another identifier, an incorrect error will be reported. This can occur at the direct instantiation or some other location where the matching identifier is used.

[nodvtid] - If a design unit contains a large number of expression that consist of real literals and implicit operations like -3.0 or 3.0/1.0, vcom performance would be very slow. This slow down has been resolved.

- QSIM-85958 - The -g/-G options when specifying more that just the generic name does not propagate to changes in port width in all cases.

- QSIM-86167 - Calls to an protected method could crash if an argument to the method is also a protected type method call and that call is not the form protected_object.portected_method( …)

- QSIM-87189 - In VHDL 2008, when using the value <> for the default value of an interface subprogram, we could fail to find an actual subprogram if the formal for the interface subprogram was not all lower case.

- QSIM-87124 - Vopt could generate bad machine code for package references resulting in a crash during elaboration in vsim.

- QSIM-84038 - In some cases, logging a n-dimensional array of std_logic would cause a crash if length of a dimension was 1 and the total number of scalar elements at that dimension was 1.

- QSIM-81420 - VSIM was crashing while trying to use type/subtype or generic procedure from package instance in certain situations. This has been fixed now.

- QSIM-84543 - Null range in record signals wasn't handled properly. This has been fixed.

Mixed Language Defects Repaired in 2024.1

- QSIM-84122 - When Verilog configurations are used on a VHDL design unit. It can cause a default binding to report an error about missing generics or ports on the entity selected. This error was incorrect and misleading because the generics or ports of the component and default entity were legal. This problem has been fixed and the error message about default binding failure has been enhance to include the actual entity selected and the reason why.

- QSIM-86090 - Forcing a slice of a hierarchical reference that resolves to a VHDL signal had no effect. The force is now correctly applied.

- QSIM-86866 - (results) When using the -mixedsvvh option for packages, real constants were limited to 6 digits after the decimal point. As a results the values of in the other language could be different from the original language. Fix preserves at least 7 digits of accuracy but the values can still differ slightly. This fix requires that the original package either be recompiled or refresh for the change to take effect. Just re-running vopt will have no effect.

- QSIM-86856 - In some cases where VHDL instantiates a System Verilog module either vcom or vopt would generate the error 1136 "Unknown identifier <library name>" if a port or generic was a struct defined originally in a System Verilog package or unit scope. This has been resolved and should not longer occur.

Power Aware Defects Repaired in 2024.1

- QSIM-81341 - Added support for writing out Power State Analysis Report into CSV File, that shows all the Power State Tables fully expanded and hierarchically composed under the vopt option -pa_genrpt=csv_pst

- QSIM-82734 - Added verror for vopt warning "vopt-9555".

- QSIM-84633 - In vsim, user can identify if its a low-power simulation using tcl proc "GetPAMode"

Below example demonstrates how user can use "GetPAMode" in .do file in vism:

if {[GetPAMode]} {

echo "This is A PA simulation"

}

QSIM-85484 - Questa PA will produce a suppressible error, if a power domain is specified in -elements list of UPF command set_design_attributes for an attribute for which power domain is not supported. Error will be reported as:

** Error (suppressible): top.upf(62): UPF: (vopt-9579) Power Domain 'top_domain' in -elements list of set_design_attributes command is currently not supported.

QSIM-85485 - In case of potential conflict between UPF Power Switch ack port driver and RTL, tool will detect the conflict and resolve it during simulation. The resolution is if RTL driver is present after resolution, it will be given preference otherwise UPF ack port driver will be used. This is supported under vopt option -pa_enable=[+]ackportdriver. Under this option, in case of potential conflict, a warning (vopt-9578) will be generated:

** Warning: top.sv(49): (vopt-9578) Ack port ack_p(/tb/instop/multi) has a potential conflict with RTL driver. Conflict will be resolved during simulation.

By default, this option is disabled.

- QSIM-85180 - (results) Source nets of resolved supply nets, which are themselves resolved, will no longer be included in the driving resolved bus.

- QSIM-85115 - Support added for skipping generate block scopes during relative path traversal with the set_scope UPF command. Attempting to access generate block scopes using set_scope command will now result in a vopt-9647 error. These changes will be enabled under the vopt option -pa_upfextensions=genscope

- QSIM-85763 - Behavior of tcl/upf puts command with -nonewline option is now fixed.

- QSIM-85545 - vopt-9022 (output port has no drivers) warning will not be reported for output ports driven via resolved bus.

- QSIM-82306 - Added support for usage of retention supply for source sink analysis if use_retention_as_primary is provided in set_retention command. This will be enabled under vopt option "-pa_enable=[+]retsupplyassrcsink". By default, the option is disabled.

Qwave logging Defects Repaired in 2024.1

- VISU-36540 - In vsim batch mode, users who invoked do scripts with "add wave -group" calls experienced failures in generating the qwavedb file. This issue was fixed and now the -group option is silently ignored, matching Questa's behavior.

User Interface Enhancements in 2024.1

- VISU-29478 - Entering CTRL+F in the Design Window now causes focus to be set to the design search text entry box at the top of the window.

- QSIM-87291 - The modelsim.ini variable "SolveFailDebugTimeout" (vsim section) has been removed. Use "SolveTimeout" instead.

- QSIM-85757 - In order to reduce the proliferation of redundant SystemVerilog extensions, the following vlog/vopt -svext extensions have been deprecated:

acsace - Allow constraint_set as contraint_expression in constraints in constraint block item.

ifslvbefr - Allow solve/before constraint under a constant if condition.

softimp - Allow implication constraint to be declared as 'soft'.

softunique - Allow 'unique' constraint to be declared as 'soft'.

stdrandarg - Allow std::randomize() arguments to be hierarchical references and indexed expressions.

These extensions only serve to change the behavior or warning/error messages related to non-LRM compliant constructs.

The effect of these extensions can be reproduced with the regular message-related command line options (e.g. -warning, -error, -suppress).

SystemVerilog Enhancements in 2024.1

[nodvtid] - Error message 13276, illegal field select, has been enhanced to display column information for where the error occurs.

- QSIM-82940 - Non-LRM compliant 'soft' implication constraints are now supported via the compile-time (vlog/vopt) SystemVerilog extension 'softimp'.

When "vlog -svext=softimp" is enabled:

any occurrence of a 'soft' implication constraint will be interpreted as described by the Description section (below)

'soft' implication constraints involving unsupported constructs will cause an informative error message to be reported

When "vlog -svext=softimp" is disabled:

any occurrence of a 'soft' implication constraint will cause an informative error message to be reported

This extension will be DISABLED by default.

Specifying "vlog -pedanticerrors" will also disable the "softimp" extension (even if enabled via -svext=+softimp).

Description

A 'soft' implication constraint is a non-LRM compliant construct that can be declared as follows:

soft if (cond) {

a;

b;

c;

}

Note that implication constraints can be written using implication style syntax:

soft (cond) -> {

a;

b;

c;

}

The 'soft' implication constraints (above) will be interpreted as follows:

soft (cond) -> (a && b && c);

The SystemVerilog extension will support the following types of implied constraints:

expressions

'dist'

'unique'

nested implied constraints

The following kinds of constructs will not be supported by 'soft' implication constraints:

implied solve/before constraint

implied 'disable soft' constraint

implied iterative constraint

implied 'soft' constraint ('soft' will be ignored, will generate warning)

implication constraint with 'else' clause

- QSIM-69839 - Enhanced support for randomize() scenarios involving random dynamic arrays with complex dependencies between the size of the array and the element(s) of the array has been implemented, such that the constraints involving the elements of the dynamic array can be simultaneously evaluated with the size of the dynamic array for the following constructs:

iterative constraints on the dynamic array

array reduction methods on the dynamic array

This enhanced support is NOT enabled by default, but can be enabled via the vsim command line option "-svrandext=+dynext".

NOTE: When -svrandext=dynext is enabled, the -svrandext=prerandfirst extension will also automatically be enabled. It is not legal to enable -svrandext=dynext and disable -svrandext=prerandfirst.

Limitations:

the enhanced flow supports dynamic arrays with a maximum size <= 64

the enhanced flow does not support multi-dimensional dynamic arrays

- QSIM-85243 - (results) The vsim SystemVerilog constrained-random language extension "prerandfirst" (-svrandext=prerandfirst) is now enabled by default. This extension changes the behavior of randomize() calls such that pre_randomize() functions of class instances referenced by random dynamic array/queue fields are executed before registering/evaluating the constraints in the parent class. This extension only affects randomize() calls involving random dynamic arrays (or queues) of class handles.

- QSIM-82333 - Extended -svrandext=dynext support for randomize() scenarios involving random dynamic arrays with complex dependencies between the size of the array and the element(s) of the array has been implemented, such that the constraints involving the elements of the dynamic array can be simultaneously evaluated with the size of the dynamic array for the following constructs:

constraint w/ random index expression

- QSIM-74277 - The behavior of the vsim "-solvetimeout <time>" command line option has changed. Previously, this command line option specified the maximum amount of CPU time a single randset had to solve before triggering a timeout during a randomize() call. The new behavior is such that the timeout <time> applies to the entire randomize() call - i.e. a randomize() call has <time> seconds to solve all of its random variables (i.e. all randsets) before triggering a timeout. The default value of the timeout has been updated to 1000 seconds (the previous default was 500 seconds).

Power Aware Enhancements in 2024.1

- QSIM-82524 - Added support for generating Power State Table Analysis Report into CSV File (report.pst.csv), with no hierarchically expanded objects/columns. This will be enabled under the vopt option -pa_genrpt=csv_pst_opt

- QSIM-82649 - Added support for reduction function (in VHDL) & unary reduction operators (in VHDL 2008) for CDFG & DFA Cone Analysis for flip-flop/latch (sequential block) detection.

- QSIM-85756 - Added support for handling -elements and -models in set_design_attributes command for attributes qpa_inactive_reset_duration and qpa_active_reset_duration.

- QSIM-84220 - Find object returns modports in case of -ports. To disable search of interface declaration in find object use option -pa_disable=intffindobj

- QSIM-85693 - Questa-PA now support search of escape name without use of "\" and " " characters.

- QSIM-85420 - Wildcard to match Enum inside structure in supported.

- QSIM-82635 - Questa PA support expansion of wildcard inside the structure under an option -pa_upfextensions=structwildcard

- QSIM-81860 - Questa PA prints hierarchical path with genblock labels separated by '.' delimiter under option -pa_enable=dotasgenblkdelimiter.

- QSIM-85664 - Questa find object now support the matching of "?" character to field separator "." under option -pa_upfextension=structwildcard

- VISU-29478 - Entering CTRL+F in the Design Window now causes focus to be set to the design search text entry box at the top of the window.

- QSIM-87291 - The modelsim.ini variable "SolveFailDebugTimeout" (vsim section) has been removed. Use "SolveTimeout" instead.

- QSIM-85757 - In order to reduce the proliferation of redundant SystemVerilog extensions, the following vlog/vopt -svext extensions have been deprecated:

acsace - Allow constraint_set as contraint_expression in constraints in constraint block item.

ifslvbefr - Allow solve/before constraint under a constant if condition.

softimp - Allow implication constraint to be declared as 'soft'.

softunique - Allow 'unique' constraint to be declared as 'soft'.

stdrandarg - Allow std::randomize() arguments to be hierarchical references and indexed expressions.

These extensions only serve to change the behavior or warning/error messages related to non-LRM compliant constructs.

The effect of these extensions can be reproduced with the regular message-related command line options (e.g. -warning, -error, -suppress).

SystemVerilog Enhancements in 2024.1

[nodvtid] - Error message 13276, illegal field select, has been enhanced to display column information for where the error occurs.

- QSIM-82940 - Non-LRM compliant 'soft' implication constraints are now supported via the compile-time (vlog/vopt) SystemVerilog extension 'softimp'.

When "vlog -svext=softimp" is enabled:

any occurrence of a 'soft' implication constraint will be interpreted as described by the Description section (below)

'soft' implication constraints involving unsupported constructs will cause an informative error message to be reported

When "vlog -svext=softimp" is disabled:

any occurrence of a 'soft' implication constraint will cause an informative error message to be reported

This extension will be DISABLED by default.

Specifying "vlog -pedanticerrors" will also disable the "softimp" extension (even if enabled via -svext=+softimp).

Description

A 'soft' implication constraint is a non-LRM compliant construct that can be declared as follows:

soft if (cond) {

a;

b;

c;

}

Note that implication constraints can be written using implication style syntax:

soft (cond) -> {

a;

b;

c;

}

The 'soft' implication constraints (above) will be interpreted as follows:

soft (cond) -> (a && b && c);

The SystemVerilog extension will support the following types of implied constraints:

expressions

'dist'

'unique'

nested implied constraints

The following kinds of constructs will not be supported by 'soft' implication constraints:

implied solve/before constraint

implied 'disable soft' constraint

implied iterative constraint

implied 'soft' constraint ('soft' will be ignored, will generate warning)

implication constraint with 'else' clause

- QSIM-69839 - Enhanced support for randomize() scenarios involving random dynamic arrays with complex dependencies between the size of the array and the element(s) of the array has been implemented, such that the constraints involving the elements of the dynamic array can be simultaneously evaluated with the size of the dynamic array for the following constructs:

iterative constraints on the dynamic array

array reduction methods on the dynamic array

This enhanced support is NOT enabled by default, but can be enabled via the vsim command line option "-svrandext=+dynext".

NOTE: When -svrandext=dynext is enabled, the -svrandext=prerandfirst extension will also automatically be enabled. It is not legal to enable -svrandext=dynext and disable -svrandext=prerandfirst.

Limitations:

the enhanced flow supports dynamic arrays with a maximum size <= 64

the enhanced flow does not support multi-dimensional dynamic arrays

- QSIM-85243 - (results) The vsim SystemVerilog constrained-random language extension "prerandfirst" (-svrandext=prerandfirst) is now enabled by default. This extension changes the behavior of randomize() calls such that pre_randomize() functions of class instances referenced by random dynamic array/queue fields are executed before registering/evaluating the constraints in the parent class. This extension only affects randomize() calls involving random dynamic arrays (or queues) of class handles.

- QSIM-82333 - Extended -svrandext=dynext support for randomize() scenarios involving random dynamic arrays with complex dependencies between the size of the array and the element(s) of the array has been implemented, such that the constraints involving the elements of the dynamic array can be simultaneously evaluated with the size of the dynamic array for the following constructs:

constraint w/ random index expression

- QSIM-74277 - The behavior of the vsim "-solvetimeout <time>" command line option has changed. Previously, this command line option specified the maximum amount of CPU time a single randset had to solve before triggering a timeout during a randomize() call. The new behavior is such that the timeout <time> applies to the entire randomize() call - i.e. a randomize() call has <time> seconds to solve all of its random variables (i.e. all randsets) before triggering a timeout. The default value of the timeout has been updated to 1000 seconds (the previous default was 500 seconds).

Power Aware Enhancements in 2024.1

- QSIM-82524 - Added support for generating Power State Table Analysis Report into CSV File (report.pst.csv), with no hierarchically expanded objects/columns. This will be enabled under the vopt option -pa_genrpt=csv_pst_opt

- QSIM-82649 - Added support for reduction function (in VHDL) & unary reduction operators (in VHDL 2008) for CDFG & DFA Cone Analysis for flip-flop/latch (sequential block) detection.

- QSIM-85756 - Added support for handling -elements and -models in set_design_attributes command for attributes qpa_inactive_reset_duration and qpa_active_reset_duration.

- QSIM-84220 - Find object returns modports in case of -ports. To disable search of interface declaration in find object use option -pa_disable=intffindobj

- QSIM-85693 - Questa-PA now support search of escape name without use of "\" and " " characters.

- QSIM-85420 - Wildcard to match Enum inside structure in supported.

- QSIM-82635 - Questa PA support expansion of wildcard inside the structure under an option -pa_upfextensions=structwildcard

- QSIM-81860 - Questa PA prints hierarchical path with genblock labels separated by '.' delimiter under option -pa_enable=dotasgenblkdelimiter.

- QSIM-85664 - Questa find object now support the matching of "?" character to field separator "." under option -pa_upfextension=structwildcard

Questa Design Solutions is an automated and integrated suite of verification tools for designers to improve initial RTL quality. Design Solutions analyzes code at the design stage to detect bugs early, to improve efficiency, enhance development predictability and ease pressure on schedules.

The Questa Advanced Simulator is the core simulation and debug engine of the Questa Verification Solution; the comprehensive advanced verification platform capable of reducing the risk of validating complex FPGA and SoC designs. Questa achieves industry-leading performance and capacity through very aggressive, global compile and simulation optimisation algorithms for SystemVerilog and VHDL.

Modelsim/QuestaSim Simulator Walk Through (Tutorial For Beginners) Part-1

Modelsim/QuestaSim Simulator Walk Through (Tutorial For Beginners) Part-2

Siemens Digital Industries Software is driving transformation to enable a digital enterprise where engineering, manufacturing and electronics design meet tomorrow. The Xcelerator portfolio helps companies of all sizes create and leverage digital twins that provide organizations with new insights, opportunities and levels of automation to drive innovation.

Owner: Siemens Digital Industries

Product Name: Questa Advanced Simulator (SIM)

Version: 2024.1

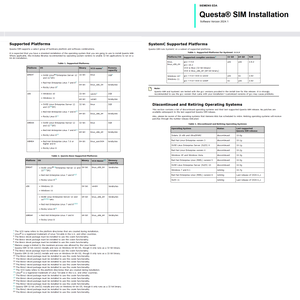

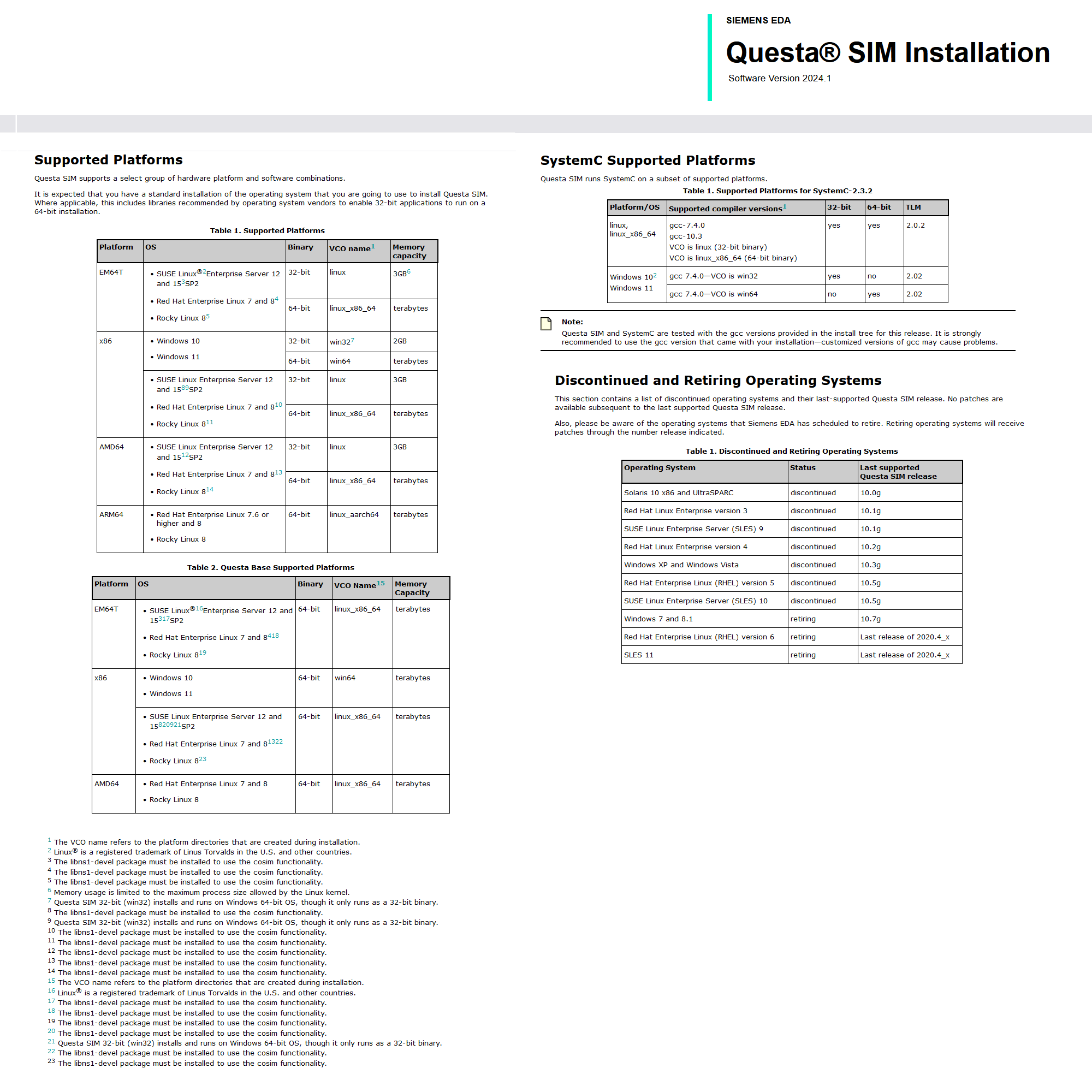

Supported Architectures: x64

Website Home Page : https://eda.sw.siemens.com/

Languages Supported: english

System Requirements: Windows *

Size: 1.2 Gb

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please