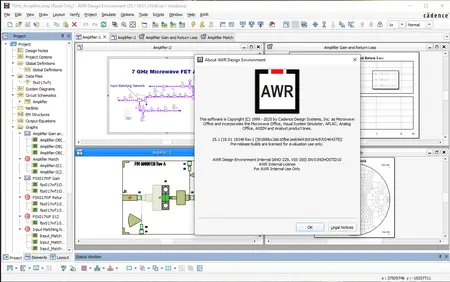

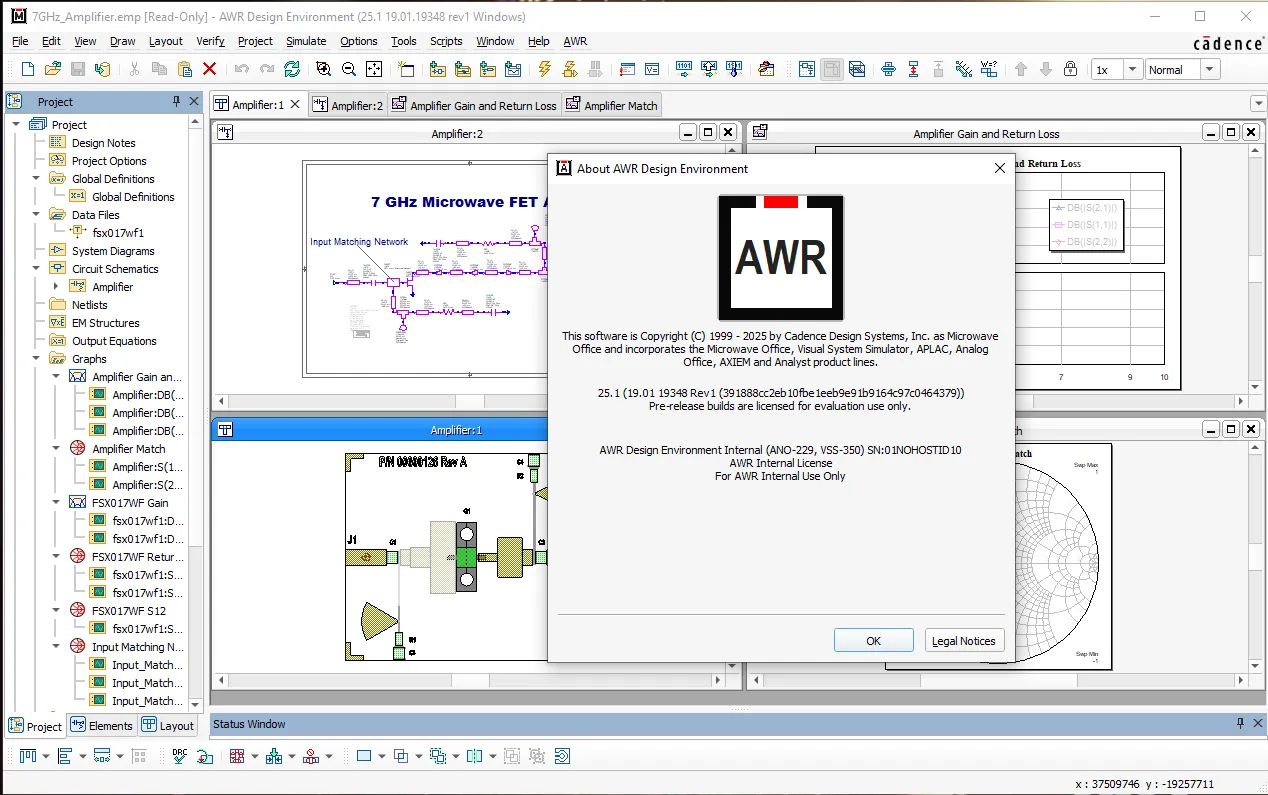

AWR Design Environment 25.10.010 | 978.0 mb

Cadence has released AWR Design Environment 25.1 ISR1. This platform provides RF/microwave engineers with integrated high-frequency circuit (Microwave Office), system (VSS), and EM (AXIEM/Analyst) simulation technologies and design automation to develop physically-realizable electronics ready for manufacturing.

What's New Organization

The Cadence AWR Design Environment V25.1 What's New document is organized into several sections:

- AWR Design Environment Features - Common improvements to all products.

- Microwave Office Features - Cadence Microwave Office design-specific software improvements.

- Visual System Simulator (VSS) Features - Cadence Visual System Simulator (VSS) communications and radar systems design-specific software improvements.

- Virtuoso Studio RF Features - Virtuoso Studio RF-specific software improvements.

- Known Issues - Known issues in the current version.

- Migration Issues - Migration issues from previous versions to the current version.

- Version 25.1 ISR Updates - Updates for minor versions.

Major Features Overview

Limited Release Features

- The current release includes select "Limited Release" features. Cadence is releasing these features during development to request customer feedback on the feature's ability to solve a full range of engineering problems. To use these features please contact your local Cadence Sales representative for documentation and any necessary license(s). Cadence strongly encourages you to provide feedback to help determine that these features solve the intended engineering problems.

AWR Design Environment

- UI Themes: Customize the workspace with light or dark mode themes.

- High DPI Monitor Support: Sharper rendering of text and icons on 4K+ monitors.

- Python Support: Run Python scripts from within the AWR Design Environment platform.

- Updated Utilities: Cross-platform support for utilities under the Scripts menu.

- Options Grid Filtering: Find options faster using the Search bar.

- Customize Dialog Box Filtering: Find commands faster using the command category drop-down list.

- Measurement Dialog Box Improvements: Save mouse clicks with new buttons.

- Enhanced Status Window: Find operational messages faster using the Search bar.

Microwave Office

- Optimizer Improvements: New screener method that is suitable for designs with many variables.

- Layout Pin Names: A new pin connectivity model that supports greater complexity and is compatible with the Virtuoso® Studio model.

- Design Rule Check (DRC) Enhancements: A new DRC Errors window.

- Power Amp Design Flow in the AWR Design Environment: A power amplifier design application note.

- Create New Process Tool for Creation of PCB PDKs: A RAK describing how to create a PDK intended for PCB designs.

- Differential Filter Design: Application note on designing differential filters highlighting the MMCONV block and Common Mode Rejection Ratio.

Virtuoso Studio RF

- Virtuoso Design Link: Instantiate Cadence Virtuoso Studio designs into Virtuoso Studio RF software for advanced RF analysis.

- Silicon RF/mmWave IP Creation: Create Silicon IP utilizing Virtuoso PDKs in Virtuoso Studio RF software, and share the schematic and layout with Virtuoso Studio software.

- Spectre Interface: Easily set up Spectre Circuit Simulator simulation within Virtuoso Studio RF software.

- Pegasus/PVS Interface: Run Pegasus/Physical Verification System (PVS) DRC and review errors with an updated error viewer.

- EM Intergrations: Run EM and thermal simulations directly from the Virtuoso Studio RF environment.

Visual System Simulator (VSS)

- Distributed VSS Sweeps: Reduce RFI, RFB, and Time Domain simulation times with parallel simulations.

- Phased Locked Loop Design: Design and analyze a PLL using behavioral models.

- RF Communication Design: Set up RFB and RFI sims for cascaded Budget Analysis.

The Cadence AWR Design Environment V25.1 What's New document is organized into several sections:

- AWR Design Environment Features - Common improvements to all products.

- Microwave Office Features - Cadence Microwave Office design-specific software improvements.

- Visual System Simulator (VSS) Features - Cadence Visual System Simulator (VSS) communications and radar systems design-specific software improvements.

- Virtuoso Studio RF Features - Virtuoso Studio RF-specific software improvements.

- Known Issues - Known issues in the current version.

- Migration Issues - Migration issues from previous versions to the current version.

- Version 25.1 ISR Updates - Updates for minor versions.

Major Features Overview

Limited Release Features

- The current release includes select "Limited Release" features. Cadence is releasing these features during development to request customer feedback on the feature's ability to solve a full range of engineering problems. To use these features please contact your local Cadence Sales representative for documentation and any necessary license(s). Cadence strongly encourages you to provide feedback to help determine that these features solve the intended engineering problems.

AWR Design Environment

- UI Themes: Customize the workspace with light or dark mode themes.

- High DPI Monitor Support: Sharper rendering of text and icons on 4K+ monitors.

- Python Support: Run Python scripts from within the AWR Design Environment platform.

- Updated Utilities: Cross-platform support for utilities under the Scripts menu.

- Options Grid Filtering: Find options faster using the Search bar.

- Customize Dialog Box Filtering: Find commands faster using the command category drop-down list.

- Measurement Dialog Box Improvements: Save mouse clicks with new buttons.

- Enhanced Status Window: Find operational messages faster using the Search bar.

Microwave Office

- Optimizer Improvements: New screener method that is suitable for designs with many variables.

- Layout Pin Names: A new pin connectivity model that supports greater complexity and is compatible with the Virtuoso® Studio model.

- Design Rule Check (DRC) Enhancements: A new DRC Errors window.

- Power Amp Design Flow in the AWR Design Environment: A power amplifier design application note.

- Create New Process Tool for Creation of PCB PDKs: A RAK describing how to create a PDK intended for PCB designs.

- Differential Filter Design: Application note on designing differential filters highlighting the MMCONV block and Common Mode Rejection Ratio.

Virtuoso Studio RF

- Virtuoso Design Link: Instantiate Cadence Virtuoso Studio designs into Virtuoso Studio RF software for advanced RF analysis.

- Silicon RF/mmWave IP Creation: Create Silicon IP utilizing Virtuoso PDKs in Virtuoso Studio RF software, and share the schematic and layout with Virtuoso Studio software.

- Spectre Interface: Easily set up Spectre Circuit Simulator simulation within Virtuoso Studio RF software.

- Pegasus/PVS Interface: Run Pegasus/Physical Verification System (PVS) DRC and review errors with an updated error viewer.

- EM Intergrations: Run EM and thermal simulations directly from the Virtuoso Studio RF environment.

Visual System Simulator (VSS)

- Distributed VSS Sweeps: Reduce RFI, RFB, and Time Domain simulation times with parallel simulations.

- Phased Locked Loop Design: Design and analyze a PLL using behavioral models.

- RF Communication Design: Set up RFB and RFI sims for cascaded Budget Analysis.

What's New in AWR Design Environment - Product Version 25.1 ISR1, August 2025

The Cadence AWR Design Environment platform version 25.1 ISR1 software includes the following new features, enhancements, and user interface changes.

The Cadence AWR Design Environment platform version 25.1 ISR1 software includes the following new features, enhancements, and user interface changes.

New Utilities

- The follow utilities are available under the Scripts menu:

- AMP_F File Generation: Creates a data file formatted for use with the AMP_F VSS amplifier element.

- Occupied Bandwidth: Measures the Occupied BW of a digitally modulated signal, which is a common digital modulation metric.

- Spur Finder: Identifies spurs in a spectrum.

Data Files

- The error message issued when attempting to parse a data file containing an invalid character now includes the line number where the error occurs, along with the column number and invalid character.

- Design Management/Version Control

- Restored the missing icons from LPFs under version control.

- A "VC" node now displays under the Circuit Symbols node in the Project Browser when connected to a source repository. Listed under the VC node are the symbol files in the repository, and listed under the file nodes are the symbols in the files.

- The Rename and Delete commands are now disabled for unlocked symbol files.

Extraction

- Schematic subcircuits are now extracted correctly in the z dimension when schematic Layout option Flipped Z is selected and an Offset is specified.

Layout

- Fixed issues with layout Boolean operations that include shapes with cutouts.

- iNets now add vias when routed onto a layout pin.

- Fixed a 3D schematic layout issue where the drawing layers could display in the wrong order in the z dimension.

- 3D Clip Area now works correctly with GPU acceleration enabled.

- DXF import now supports HATCH entities and native arcs.

Layout - EM

- Fixed an issue where if there were multiple ports that shared the same port numbers, a port could shift locations and overlap another port with the same number in a high hierarchy level when the EM structure was used as a subcircuit in several levels of hierarchy.

- Fixed an issue that could cause a blank EM structure 3D view to display.

- Fixed a crash that occurred when adding cutplanes in the 3D EM Layout View when GPU acceleration was disabled.

- Shapes now retain the Net Name specified on the shape Properties dialog box Net Properties tab.

Models - System

- The column header of the data file generated by the FILE_SNK block is now correctly formatted when Write columns header as comment is selected.

- Fixed an issue with MIXER_B calculation of output center frequency when LO input frequency is switched.

- Fixed loading issues of models with vector parameters such as RFSW_1nST from an xml component library.

Optimization

- The AWR Design Environment software no longer freezes when trying to float the Optimizer dialog box while optimizing.

- The AWR Design Environment software no longer freezes when right-clicking on the title bar of a floating Optimizer dialog box while optimizing.

Simulation - EMX

- Added a new iNet Area Pin port type on the EXTRACT block for EMX extraction.

- 3D-view EM currents annotation arrows on non-orthogonal segments now point in the correct direction.

Simulation - Systems

- Improved responsiveness of the Simulation window when running long RFI and RFB simulations.

- Results of a distributed swept simulation utilizing a SWPVAR_DIST block along with other non-distributed swept parameters now plot correctly.

- RF Budget noise calculation was incorrectly setting the thermal noise floor to be the total noise floor when the phase noise level at a given offset was lower than the thermal noise floor. This issue is fixed and RF Budget simulations now calculate the total noise floor correctly as the sum of both phase and thermal noise.

User Interface

- Default document names and file paths no longer contain a whitespace on Linux.

- When the Tuner slider is selected, scrolling the mouse wheel now moves the slider in increments corresponding to the Step Size.

- Updated the font and background colors used in the Simulation window for improved distinction between job Type and State.

- An error message is now issued on Linux when attempting to save a project when there is insufficient disk space.

- Wizards now display with the correct names in the Add Existing Item dialog box for User Folders.

- Duplicating or copying a modified schematic to the clipboard no longer removes the modified icon overlay.

- The F3 key now works correctly to Find Next when searching in the Status window when the Design Notes window is also open.

- Changes to a document or Project Options RF Frequencies tab Data Entry Units are now correctly retained after closing the dialog box.

- Restored element description tooltips in the Element Browser when the description is longer than the display frame.

- Duplicate EM subcircuits no longer display in the Project Browser after renaming an EM subcircuit.-

- When choosing New Circuit Symbol File, the unnecessary New Circuit Symbol dialog box no longer displays.

- Right-clicking on an LPF in the Layout Manager and choosing Edit as Text now opens the text editor when the Layout Manager is set to Auto-hide.

- In the Add/Modify Measurement dialog box, the Measurement Component parameter for nonlinear measurements no longer resets when changing simulators.

- Fixed an occasional crash when closing the Tuner window.

- Fixed a crash that could occur after editing rich text boxes.

Wizard - Create New Process

- The Create Process Wizard (choose Tools - Create New Process) now correctly generates a PDK on Linux.

Wizard - IFF

- The IFF Import Wizard is now available on Linux.

Wizard - PCB Import

- Allegro .brd and .mcm board files newer than Allegro version 22.1 now import without error. Support of .brd and .mcm import requires that Allegro be installed on the machine (Windows) or the network (Linux).

The Cadence AWR Design Environment platform electronic design automation (EDA) software suite provides RF/microwave engineers with access to innovative high-frequency circuit, system, and electromagnetic (EM) analysis technologies. Today’s microwave and RF engineers use this powerful, open platform to design wireless products ranging from base stations to cellphones to satellite communications. The AWR Design Environment software advantages are straightforward: an intuitive use model that delivers an exceptional user experience (UX), robust simulation technologies that deliver both speed and accuracy, and an open design flow supporting data to/from third-party tools.

Getting Started and Impedance Matching with AWR

This video gives an introduction to AWR Design Environment in a step-by-step fashion. By the end of the video, you will be able to create schematics and graphs, analyze ideal and realistic transmission line circuits, and perform impedance matching using the tuning tool.

Cadence is a pivotal leader in electronic systems design, building upon more than 30 years of computational software expertise. The company applies its underlying Intelligent System Design strategy to deliver software, hardware and IP that turn design concepts into reality. Cadence customers are the world’s most innovative companies, delivering extraordinary electronic products from chips to boards to complete systems for the most dynamic market applications, including hyperscale computing, 5G communications, automotive, mobile, aerospace, consumer, industrial and healthcare. For nine years in a row, Fortune magazine has named Cadence one of the 100 Best Companies to Work For.

Owner: Cadence

Product Name: AWR Design Environment

Version: 25.1 ISR1 (19.01.19348)

Supported Architectures: x64

Website Home Page : www.awr.com

Languages Supported: english

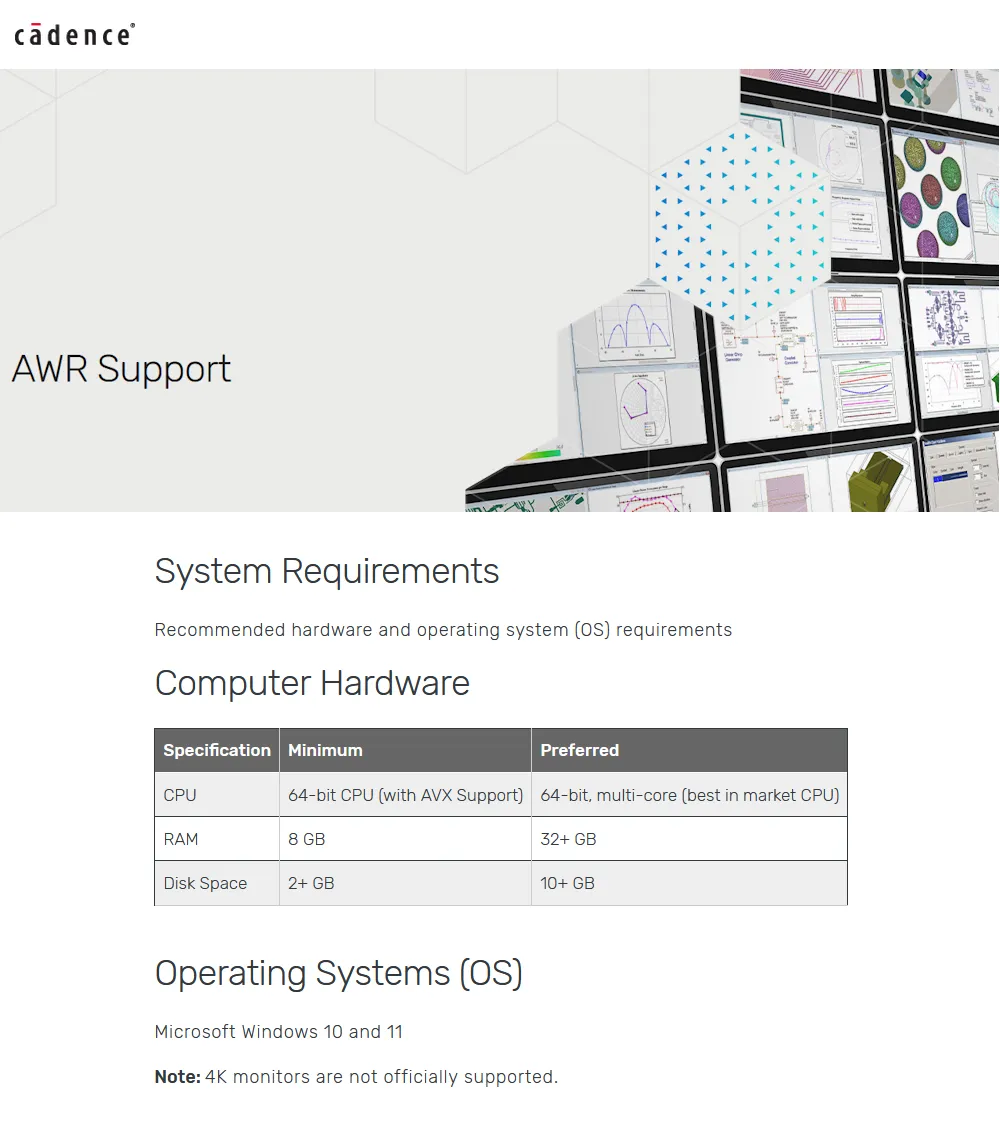

System Requirements: Windows *

Size: 978.0 mb

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please