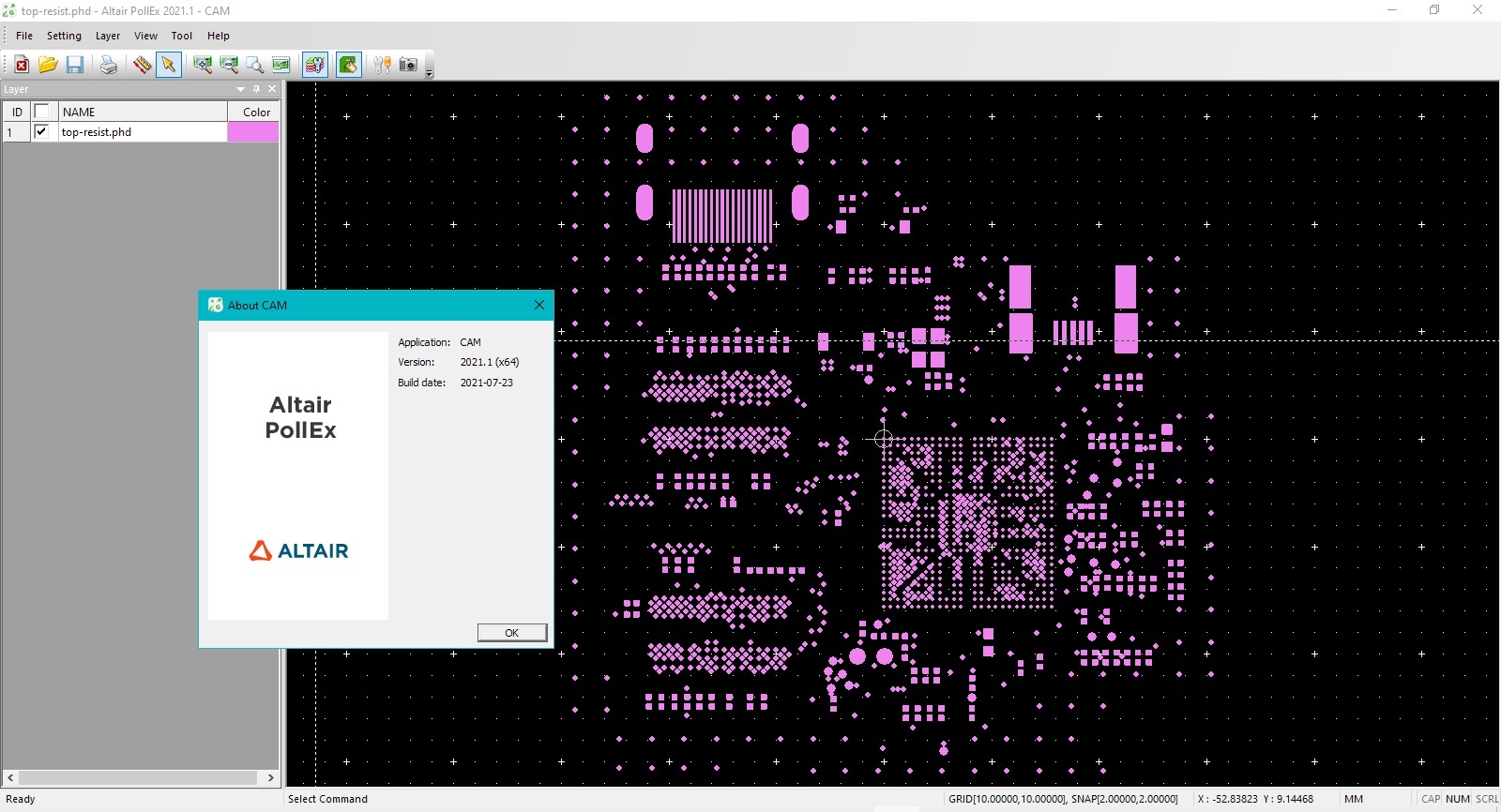

Altair PollEx 2021.1.0 | 1.2 Gb

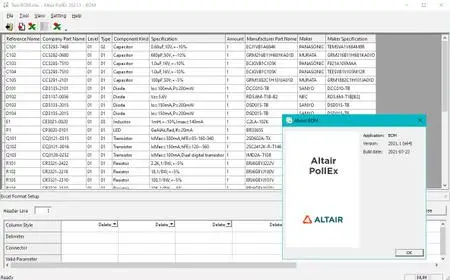

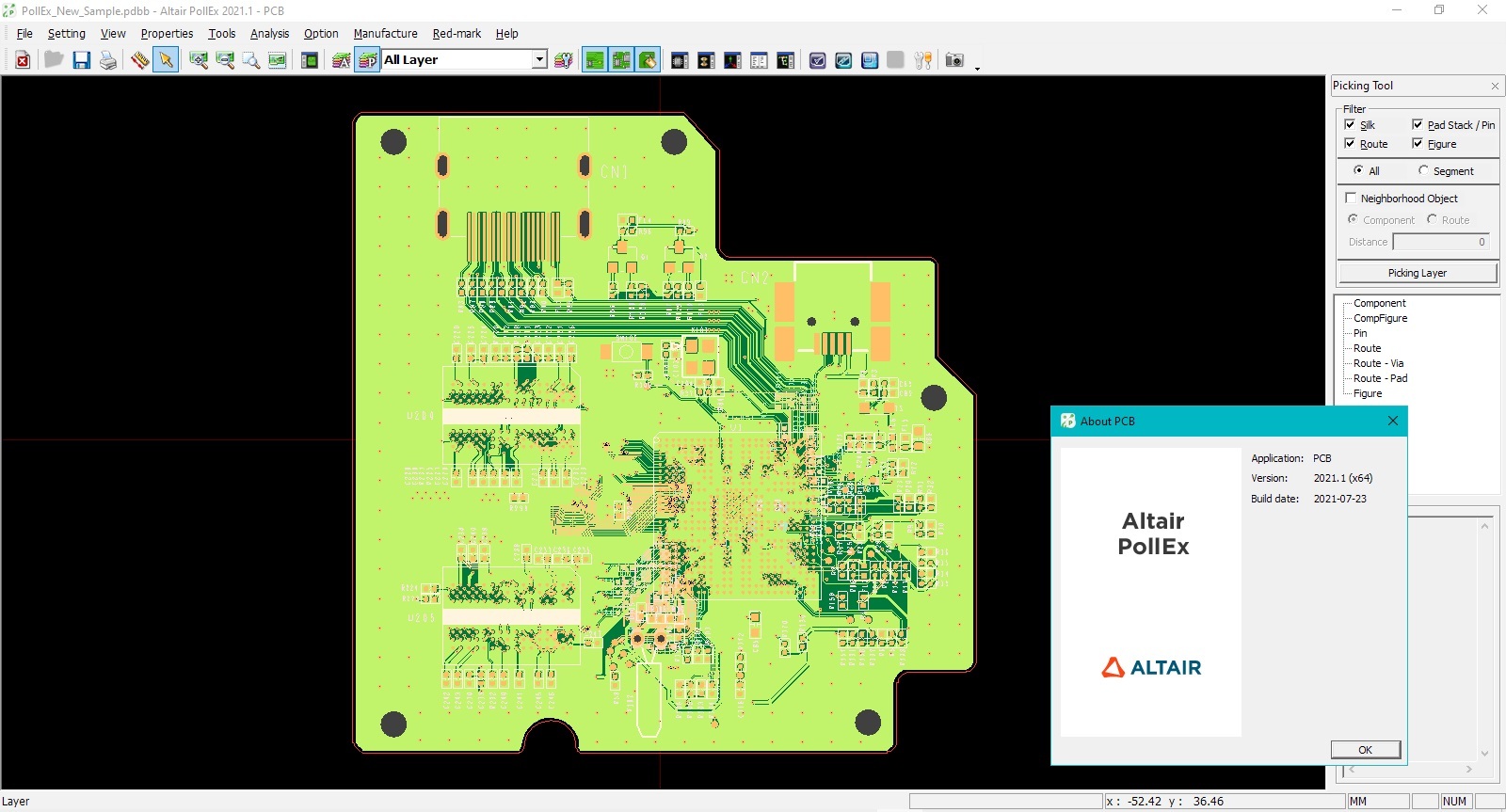

The Altair development team is pleased to announce the availability of PollEx 2021.1.0 is a PCB-level Electronic Design Automation (EDA) software suite covering design review, analysis and manufacturing.

Release Notes: PollEx 2021.1

PollEx 2021.1 is available with a long list of new features, corrections, and improvements. If older version of PollEx installed on a machine, it should be deleted first and installed the PollEx 2021.1. This chapter covers the following:

SALIENT FEATURES

Adding and modifying new license features

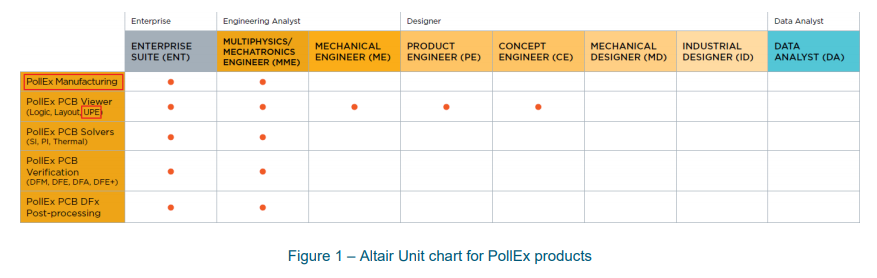

• New license feature code: PollExMFG is added for the PollEx manufacturing options which will draw the same 30 AUs.

• Changed license feature code: PollEx UPE application is available in PollExBasic feature which will draw 10 AUs from 30AUs.

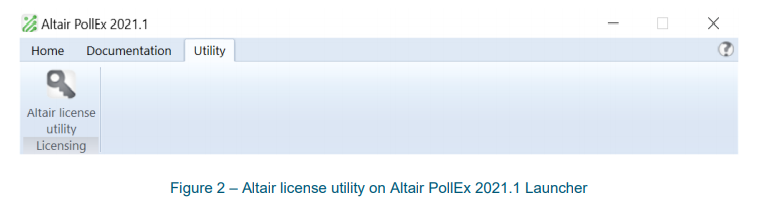

Adding Altair License Utility

• Altair License Utility is added in PollEx 2021.1 launcher.

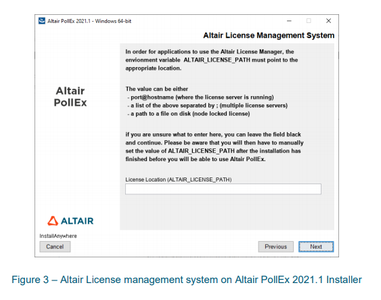

Adding Altair License Management System setup panel

• The environment variable setting panel is added during install. This panel is only displayed if the environment variable has not been set.

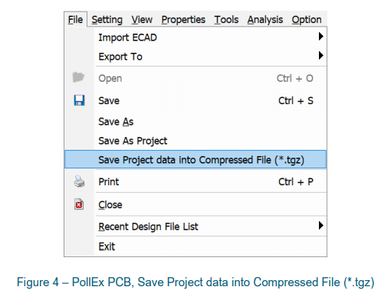

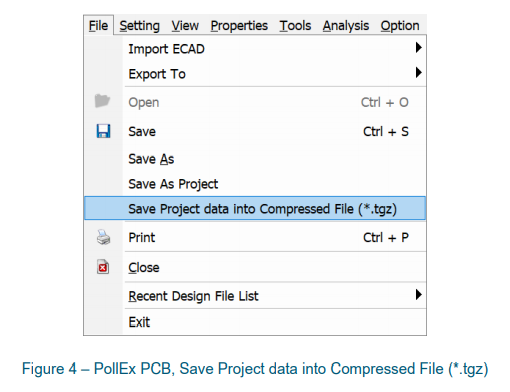

Adding design data saving option in PollEx PCB

• Added a feature to save design data in a project directory with a compressed file (*.tgz) to share relevant data conveniently.

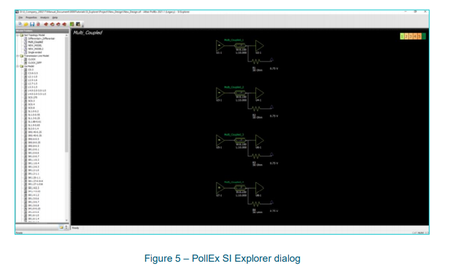

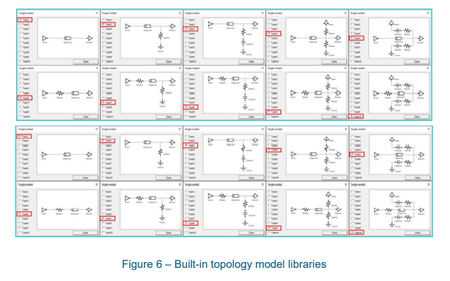

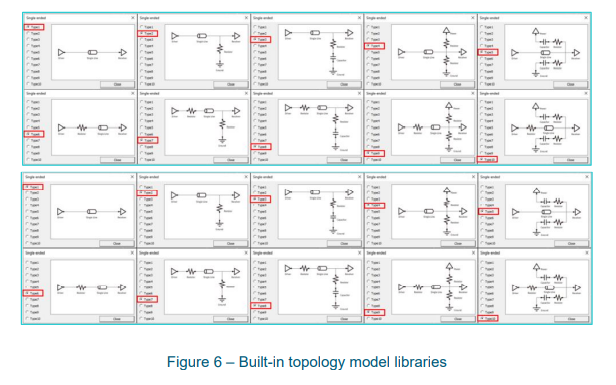

Added SI Explorer

• Added a feature to support pre-layout analysis SI Explorer menu. A feature to perform pre-layout analysis was added. PollEx SI Explorer menu allows to validate the design decisions throughout the design process including the selection of parts, add materials, construct board layer stack-up and create the net topology.

• Upon executing PollEx SI Explorer, the SI Explorer dialog comes up. You can start pre-layout signal integrity analysis from the scratch.

. Create layer stackup

. Create VIA model

. Create Transmission Line Model

. Create Net topology (Single-ended, Differential, Multi-coupled)

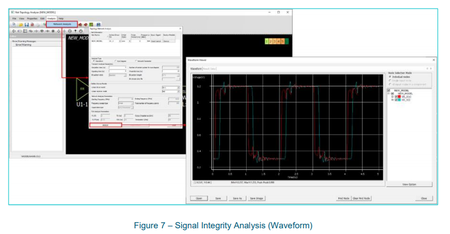

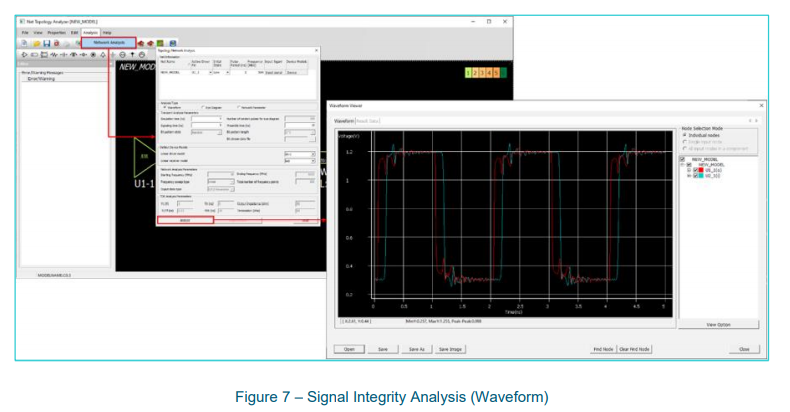

• Perform Signal Integrity Analysis (Waveform, Eye-diagram, Network Parameter)

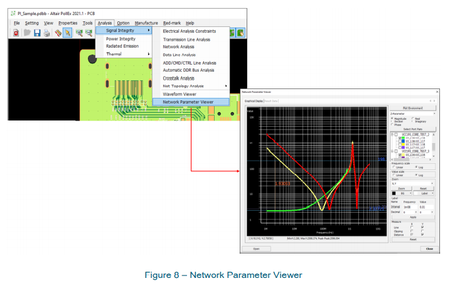

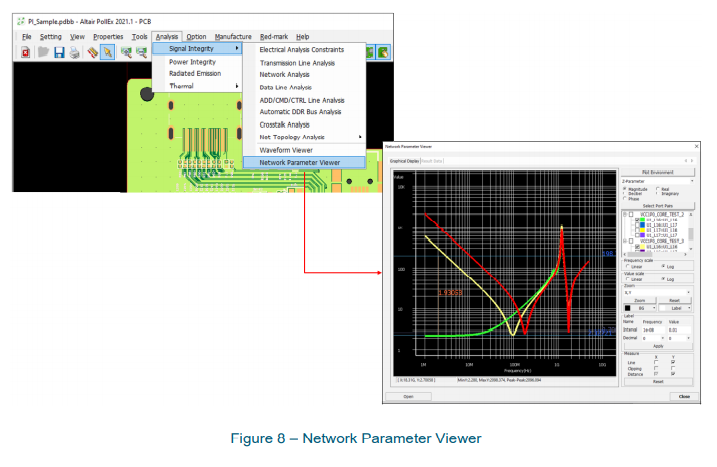

Adding a feature to display S/Y/Z parameters

• Adding a feature to display S / Y / Z parameter in Network Parameter viewer, PollEx SI. By using this function, it is possible to compare and measure by opening the S / Y / Z parameters extracted from various conditions

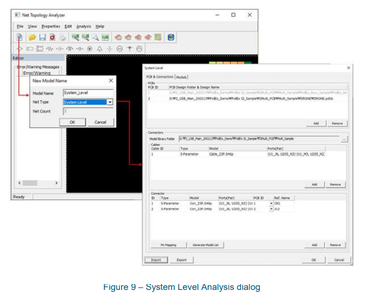

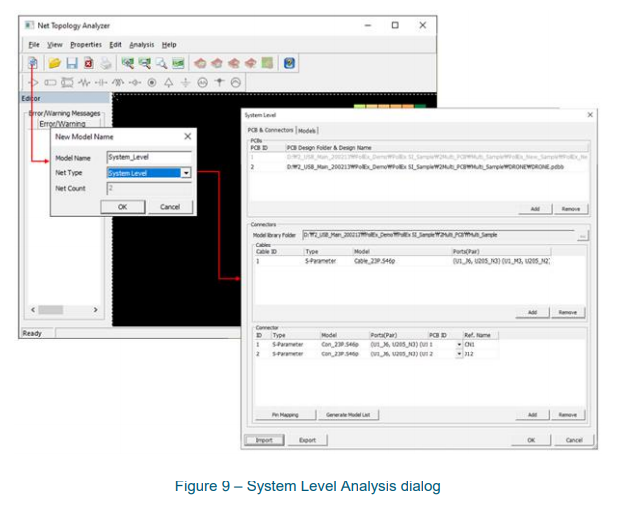

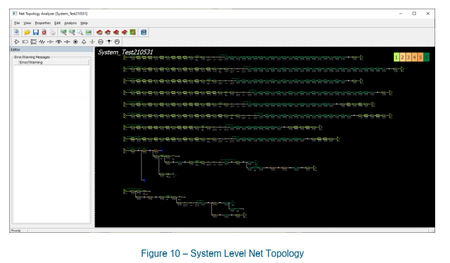

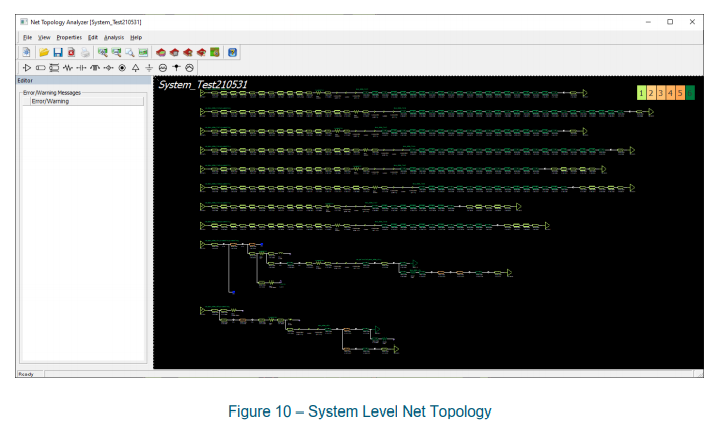

Adding an automation feature to support Multi-PCB structure

• Added a feature to generate system-level net topology automatically. By using this function, multi-level topology configuration and analysis between PCBs with different stackup is possible.

• Note: In version V2021.1, only single net (Single-ended, Differential Pair) analysis is possible. The analyze function of multiple net topologies will be released in V2021.2 version.

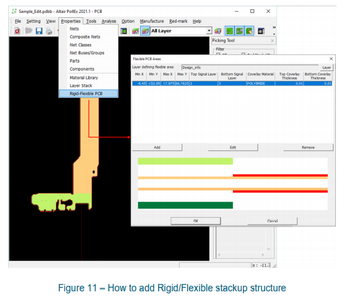

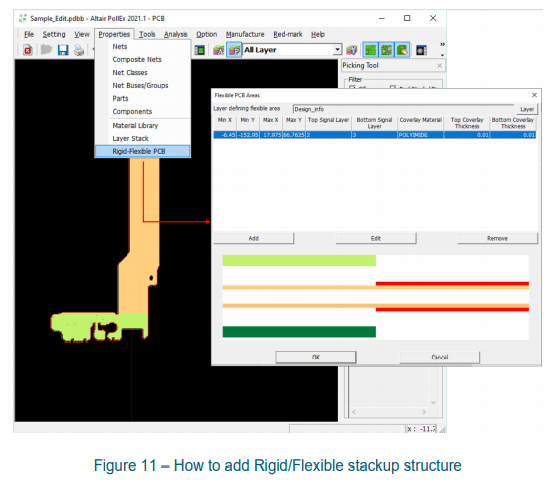

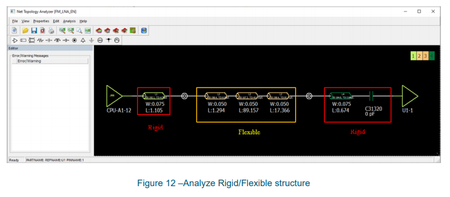

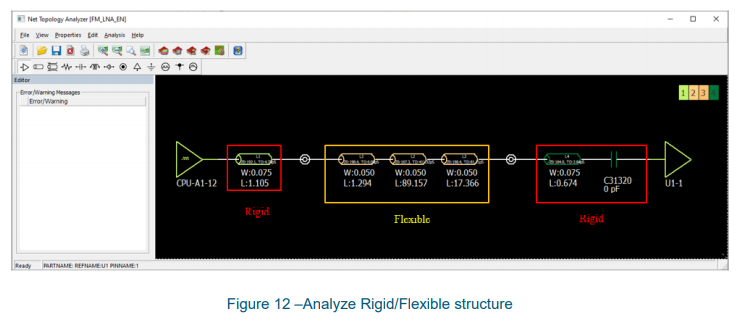

Adding a feature to support Rigid/Flexible PCB design

• System level signal integrity analysis is possible considering the multiple stackup structure of a design designed as a Rigid/Flexible structure

Adding a feature to extract SPICE Netlist

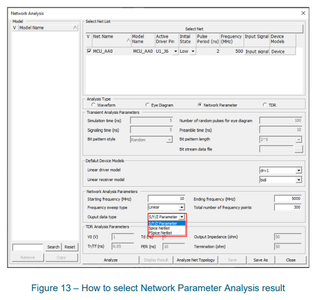

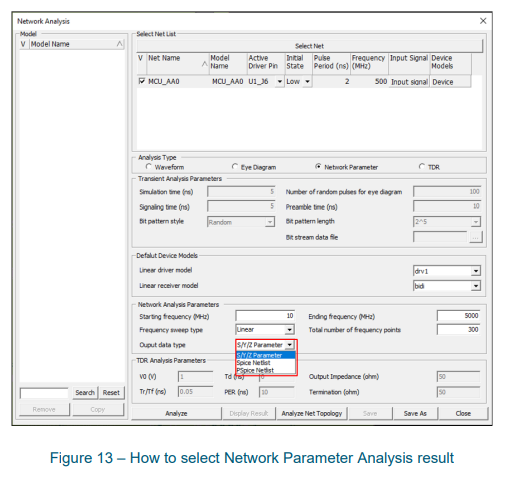

• Adding a feature to extract SPICE Netlist, you can select and determine the results of network parameter analysis. You can specify the output of the network analysis. (S/Y/Z Parameter, Spice Netlist, PSPICE Netlist)

. S/Y/Z Parameter: Network Analysis results are displayed as S/Y/Z parameters.

. Spice Netlist: Network Analysis results are saved in Berkeley Spice compatible format. (*.sp)

. PSPICE Netlist: Network Analysis results are saved in PSPICE compatible format. (*.lib)

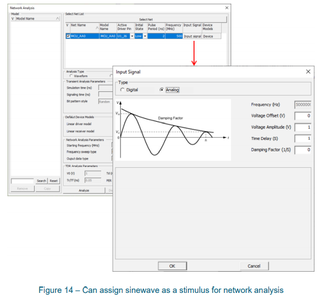

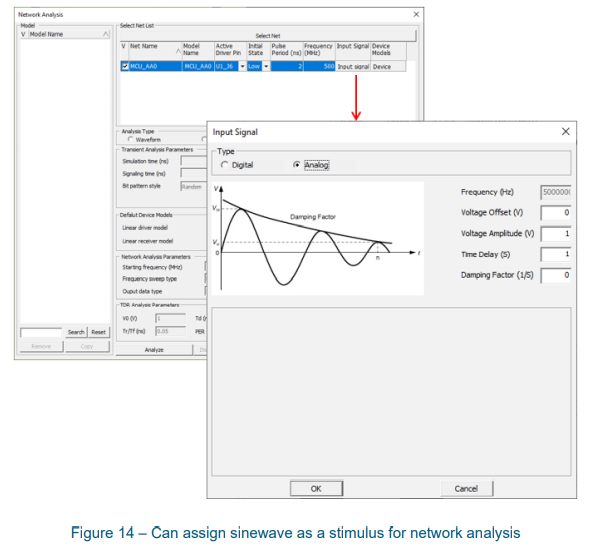

Adding a feature to assign analog input

• Added a function to apply analog waveforms such as sinewave as an analysis stimulus during network analysis

Adding and modifying new license features

• New license feature code: PollExMFG is added for the PollEx manufacturing options which will draw the same 30 AUs.

• Changed license feature code: PollEx UPE application is available in PollExBasic feature which will draw 10 AUs from 30AUs.

Adding Altair License Utility

• Altair License Utility is added in PollEx 2021.1 launcher.

Adding Altair License Management System setup panel

• The environment variable setting panel is added during install. This panel is only displayed if the environment variable has not been set.

Adding design data saving option in PollEx PCB

• Added a feature to save design data in a project directory with a compressed file (*.tgz) to share relevant data conveniently.

Added SI Explorer

• Added a feature to support pre-layout analysis SI Explorer menu. A feature to perform pre-layout analysis was added. PollEx SI Explorer menu allows to validate the design decisions throughout the design process including the selection of parts, add materials, construct board layer stack-up and create the net topology.

• Upon executing PollEx SI Explorer, the SI Explorer dialog comes up. You can start pre-layout signal integrity analysis from the scratch.

. Create layer stackup

. Create VIA model

. Create Transmission Line Model

. Create Net topology (Single-ended, Differential, Multi-coupled)

• Perform Signal Integrity Analysis (Waveform, Eye-diagram, Network Parameter)

Adding a feature to display S/Y/Z parameters

• Adding a feature to display S / Y / Z parameter in Network Parameter viewer, PollEx SI. By using this function, it is possible to compare and measure by opening the S / Y / Z parameters extracted from various conditions

Adding an automation feature to support Multi-PCB structure

• Added a feature to generate system-level net topology automatically. By using this function, multi-level topology configuration and analysis between PCBs with different stackup is possible.

• Note: In version V2021.1, only single net (Single-ended, Differential Pair) analysis is possible. The analyze function of multiple net topologies will be released in V2021.2 version.

Adding a feature to support Rigid/Flexible PCB design

• System level signal integrity analysis is possible considering the multiple stackup structure of a design designed as a Rigid/Flexible structure

Adding a feature to extract SPICE Netlist

• Adding a feature to extract SPICE Netlist, you can select and determine the results of network parameter analysis. You can specify the output of the network analysis. (S/Y/Z Parameter, Spice Netlist, PSPICE Netlist)

. S/Y/Z Parameter: Network Analysis results are displayed as S/Y/Z parameters.

. Spice Netlist: Network Analysis results are saved in Berkeley Spice compatible format. (*.sp)

. PSPICE Netlist: Network Analysis results are saved in PSPICE compatible format. (*.lib)

Adding a feature to assign analog input

• Added a function to apply analog waveforms such as sinewave as an analysis stimulus during network analysis

The most notable extensions and improvements to PollEx are listed by component

Feature

• Added a feature to save design data in a project directory with a compressed file (*.tgz).

• Added a feature for paring a differential pair net using a net string.

• Added a Pad Measure Base option in the Hole Through Pad item that set overlapped area of a pad and a solder mask (Pad+Solder Mask Overlap).

• Added a Checking Type option in the Copper Connected Pad item that you can select a type either Connected copper width ratio or Exposed copper area ratio.

• Added an option in the Net Group Shield item to pass if any one of the top or bottom side meets the checking criteria during the vertical shield check.

• Added a VIA Shielding option in the Diff – Complete Shield item.

• Added a feature to automatically set Component/Net Groups using the Part Classification set in UPE.

• Added a Net’s Input Setting menu in the Input dialog to check a grouping information of components or nets.

• Added an option in the IR Drop to check Allowable IR-Drop Value registered in the UPE.

• Added an option in the PDB Impedance to check using Target Impedance Value registered in the UPE.

• Added an option in the Result Table Export menu to export Result Area Image and ECAD Link Info.

• Added the TDR analysis type in the Network Analysis. With this option, the impedance waveform seen from the driver stage of the entire net structure can be analyzed. In this version, multiple reflections are not considered, and will be considered in our next release.

• Added a feature to select and determine the results of network parameter analysis in the Network Analysis. You can use this constraint to specify the output of the network analysis.

- S/Y/Z Parameter: Network Analysis results are displayed as S/Y/Z parameters.

- Spice Netlist: Network Analysis results are saved in Berkeley Spice compatible format. (*.sp).

- PSPICE Netlist: Network Analysis results are saved in PSPICE compatible format. (*.lib).

• Added a feature to apply analog waveforms in the Network Analysis such as sinewave as an analysis stimulus.

• Added a feature to support the Rigid/Flexible PCB design. By using this function, system level signal integrity analysis is possible considering the multiple stackup structure of a design designed as a Rigid/Flexible structure.

• Added a Network Parameter Viewer to display S/Y/Z parameters. It is enabled to compare and measure by opening the S/Y/Z parameters extracted from various conditions.

• Added an option to specify the Drill Layer when importing a design data.

• Added a command line to convert design unit.

• Added a command line to create a UPF file (/EXPORT_UPFS).

• Added an option to specify the Silk Layers for Top and Bottom when importing a design data.

Resolved Issues

• Modified to display Vdiff waveform of Differential Pair Net in the Waveform Viewer when analyzing Eye-diagram in the Network Analyzer.

• Modified to change the value of the passive component in the Net Topology Analyzer.

• Enhanced to use both Period(ps) and Frequency(MHz) when setting the operating speed of the signal in the Network Analysis.

• Enhanced a feature to generate system-level net topology automatically. Multi-level topology configurations and analysis between PCBs with different stack-ups are enabled.

• Modified the PDN Analysis to analyze even when polygons are directly connected to pins.

• Added a feature to analyze not only the heat of the active component, but also the effect of the heat of the trace joule.

• Added a feature to support Rigid/Flexible PCB. By using this function, thermal analysis is possible considering the multiple stackup structure of a design designed as a Rigid/Flexible structure.

• Fixed a bug that the partition name was not applied when adding a logic symbol using a functional symbol.

• Fixed a bug of incorrect dimensions of SOD123 package in the Generate Package Wizard.

Feature

• Added a feature to save design data in a project directory with a compressed file (*.tgz).

• Added a feature for paring a differential pair net using a net string.

• Added a Pad Measure Base option in the Hole Through Pad item that set overlapped area of a pad and a solder mask (Pad+Solder Mask Overlap).

• Added a Checking Type option in the Copper Connected Pad item that you can select a type either Connected copper width ratio or Exposed copper area ratio.

• Added an option in the Net Group Shield item to pass if any one of the top or bottom side meets the checking criteria during the vertical shield check.

• Added a VIA Shielding option in the Diff – Complete Shield item.

• Added a feature to automatically set Component/Net Groups using the Part Classification set in UPE.

• Added a Net’s Input Setting menu in the Input dialog to check a grouping information of components or nets.

• Added an option in the IR Drop to check Allowable IR-Drop Value registered in the UPE.

• Added an option in the PDB Impedance to check using Target Impedance Value registered in the UPE.

• Added an option in the Result Table Export menu to export Result Area Image and ECAD Link Info.

• Added the TDR analysis type in the Network Analysis. With this option, the impedance waveform seen from the driver stage of the entire net structure can be analyzed. In this version, multiple reflections are not considered, and will be considered in our next release.

• Added a feature to select and determine the results of network parameter analysis in the Network Analysis. You can use this constraint to specify the output of the network analysis.

- S/Y/Z Parameter: Network Analysis results are displayed as S/Y/Z parameters.

- Spice Netlist: Network Analysis results are saved in Berkeley Spice compatible format. (*.sp).

- PSPICE Netlist: Network Analysis results are saved in PSPICE compatible format. (*.lib).

• Added a feature to apply analog waveforms in the Network Analysis such as sinewave as an analysis stimulus.

• Added a feature to support the Rigid/Flexible PCB design. By using this function, system level signal integrity analysis is possible considering the multiple stackup structure of a design designed as a Rigid/Flexible structure.

• Added a Network Parameter Viewer to display S/Y/Z parameters. It is enabled to compare and measure by opening the S/Y/Z parameters extracted from various conditions.

• Added an option to specify the Drill Layer when importing a design data.

• Added a command line to convert design unit.

• Added a command line to create a UPF file (/EXPORT_UPFS).

• Added an option to specify the Silk Layers for Top and Bottom when importing a design data.

Resolved Issues

• Modified to display Vdiff waveform of Differential Pair Net in the Waveform Viewer when analyzing Eye-diagram in the Network Analyzer.

• Modified to change the value of the passive component in the Net Topology Analyzer.

• Enhanced to use both Period(ps) and Frequency(MHz) when setting the operating speed of the signal in the Network Analysis.

• Enhanced a feature to generate system-level net topology automatically. Multi-level topology configurations and analysis between PCBs with different stack-ups are enabled.

• Modified the PDN Analysis to analyze even when polygons are directly connected to pins.

• Added a feature to analyze not only the heat of the active component, but also the effect of the heat of the trace joule.

• Added a feature to support Rigid/Flexible PCB. By using this function, thermal analysis is possible considering the multiple stackup structure of a design designed as a Rigid/Flexible structure.

• Fixed a bug that the partition name was not applied when adding a logic symbol using a functional symbol.

• Fixed a bug of incorrect dimensions of SOD123 package in the Generate Package Wizard.

PollEx is the most comprehensive and integrated set of PCB design viewing, analysis, and verification tools for electrical, electronics, and manufacturing engineers. PollEx transfers data flawlessly between the industry’s most popular ECAD and simulation tools and enables many of the world’s major electronics corporations to quickly visualize and review PCB designs. Its checking tools detect issues early in the design to avoid product failures and simplify manufacture and assembly.

PollEx 2021 is available with a long list of new features, corrections, and improvements.

Samsung SDI Improves PCB Development with Altair PollEx

Altair is a global technology company that provides software and cloud solutions in the areas of product development, high performance computing (HPC) and data analytics. Altair enables organizations across broad industry segments to compete more effectively in a connected world while creating a more sustainable future.

Product: Altair PollEx

Version: 2021.1.0 with Tutorials

Supported Architectures: x64

Website Home Page : www.altair.com

Languages Supported: multilanguage

System Requirements: PC *

Size: 1.2 Gb

What You Need Minimum

Operating System

- Windows 7, 8.1 and 10.

- 64 bits only

Hardware

- OpenGL graphics card with at least 256 MB of onboard memory.

Memory

- 4 GB of RAM (8 GB recommended).

- 10 GB or more of free hard disk space.

Operating System

- Windows 7, 8.1 and 10.

- 64 bits only

Hardware

- OpenGL graphics card with at least 256 MB of onboard memory.

Memory

- 4 GB of RAM (8 GB recommended).

- 10 GB or more of free hard disk space.

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please