Cadence Allegro and OrCAD 2022 (22.10.000) | 9.8 Gb

Cadence Design Systems, Inc. , the leader in global electronic design innovation, is pleased to announce the availability of Cadence Allegro and OrCAD 22.1-2022 P001 families of products aimed at boosting performance and productivity through improvements features and big fixed issues.

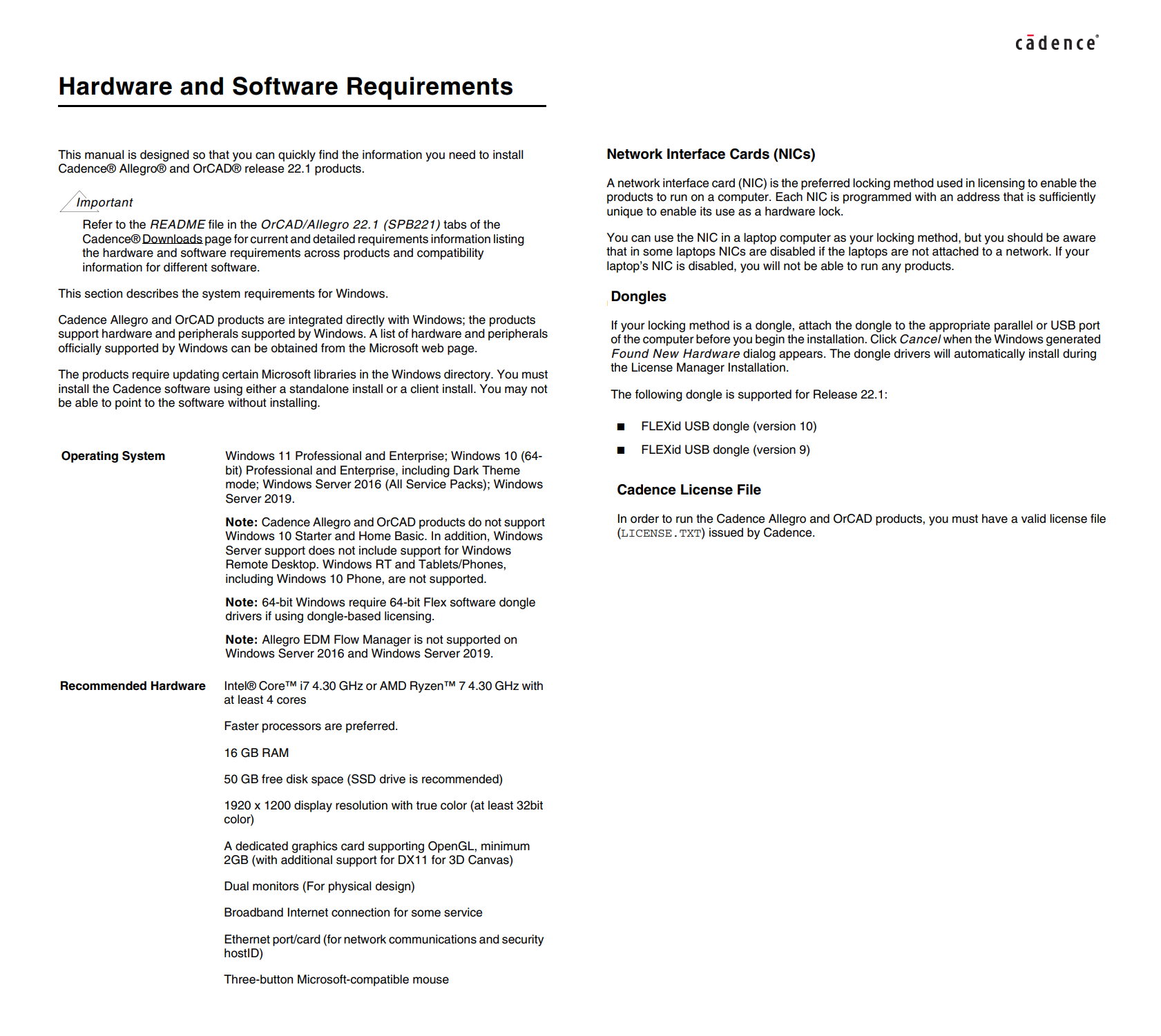

Cadence OrCAD and Allegro: What’s New in Release 22.1

The bellow presents sections describes the new features and enhancements in Allegro PCB Editor and Allegro Package Designer Plus, in release 22.1.

- Memory Usage and Performance Improvement Using 3DX Canvas

- High-Speed Structure Enhancements

. Parameterized High-Speed Structures

. Differential Pair Vias Replaced by Structures

. On-Canvas Structure Update and Variant Creation

- Converting Shapes, Vias, and Pins

- Dimensioning Update

- Route Keepouts Exception Use Model Enhancement

- Performance Enhancements

. Better Performance in Designs with Large Number of DRCs

. Faster Update to Smooth

. Better Move Performance

. Better Performance for Shape Parameter per Layer Override

. Restricting Command Window Messages

. Faster DRC Checking on Designs with Negative Layers

Note: For details on these new features and enhancements, refer to the Release_Notes.pdf file available from the Help menu on your hard drive or located here

Migrating to Release 22.1

Although the database format has not changed between releases 17.4-2019 and 22.1, you still need to acquire new licenses and an account to work with Mirrored Layers.

Database Format

You can open any release 17.4-2019 design in release 22.1 or, conversely, a release 22.1 design in release 17.4-2019 without any need to migrate the database format because the same database format is used across the two releases.

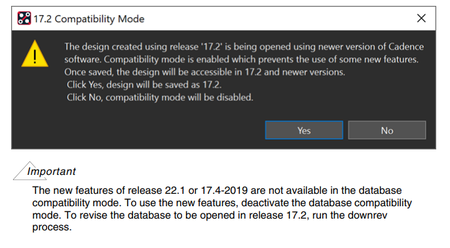

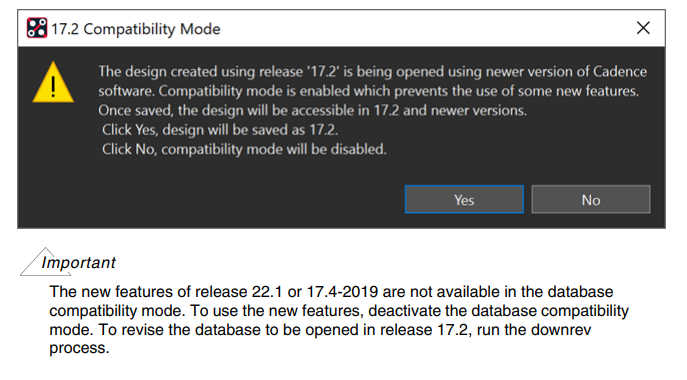

The 17.2 Database Compatibility Mode can still be enabled in User Preferences Editor to allow release 17.2 designs to be opened in releases 17.4 or 22.1 without updating the database version. Designs opened in the compatibility mode can be opened in release 17.2.

License Updates

A new license file is required to run release 22.1 products. Products from earlier releases such as 17.x, can also be opened with a release 22.1 license.

Structures and Vias in Mirrored Layers

If a database has structures in the mirrored layers state, that is marked as mirrored_layers, the database cannot be migrated to a version earlier than release 17.4 -2019, HotFix 028 (QIR4). The objects in the mirrored layers state are structures that are flipped using the Mirror Geometry command and then mirrored to the opposite side of the board. It is common to use the Mirror Geometry command to flip a structure on the same layer, but vias can also be flipped when moved or copied and if such vias are part of a symbol, module, or group, mirroring changes the vias to the Mirrored Layers state.

======================================================================================

CCRID Product ProductLevel2 Title

==============================================================================================

2462298 ADW DBEDITOR Unable to add value to the predefined values list in part classification when 'Restrict predefined values' is selected

2673073 ADW DBEDITOR Unable to check out schematic models in Allegro EDM Database Editor

2676082 ADW DBEDITOR Unable to check out schematic models in Allegro EDM Database Editor in release 17.4-2019, HotFix 030

2697393 ADW DBEDITOR Allegro EDM Database Editor is slow to use in release 17.4-2019

2697566 ADW DBEDITOR The release time for EDM models is significantly higher in release 17.4-2019, HotFix 030

2553658 ADW LRM When updating a block in the design using LRM, it is not adding the new part in the block, so Packager then fails after

2693395 ADW PART_MANAGER Placing a new part in a design shows the part as out of sync

2664409 ALLEGROX 3D_CANVAS 3D Aware Placement: checking spacing requirements for components using 3D geometry of associated components

2115283 ALLEGRO_EDITOR 3D_CANVAS Bend function is grayed out in Allegro 3D Canvas

2352077 ALLEGRO_EDITOR 3D_CANVAS SILKSCREEN mapped for Flex zones

2454283 ALLEGRO_EDITOR 3D_CANVAS PCB Editor stops responding after invoking 3D Canvas

2456820 ALLEGRO_EDITOR 3D_CANVAS 3D Viewer: Micro vias are not showing correctly in release 17.4-2019, HotFix 014 or later

2461978 ALLEGRO_EDITOR 3D_CANVAS STEP model appears deformed and smaller in 3D Canvas

2525936 ALLEGRO_EDITOR 3D_CANVAS STEP model appears oversized in 3D Canvas

2637074 ALLEGRO_EDITOR 3D_CANVAS Need new graphics engine for 3D Canvas

2558947 ALLEGRO_EDITOR DATABASE Zone Manager Mapping Issue

2565249 ALLEGRO_EDITOR DATABASE Unable to select a stackup when it is set to anything other than Primary

2644792 ALLEGRO_EDITOR DATABASE ERROR: Detected subclass BOTTOM is a zone surface but not identified in design.

2682310 ALLEGRO_EDITOR DATABASE Cadence 17.4 padstack definition on SKILL

2687247 ALLEGRO_EDITOR DATABASE Database gets corrupted when saved after moving a few components

2696887 ALLEGRO_EDITOR DATABASE DRC marker disappears despite being set to visible when the layer of the attached object is invisible

2057590 ALLEGRO_EDITOR DFM FILLED RECTANGLE or LINE objects cannot work as gang mask at the Slivers of DFF constraints

2604294 ALLEGRO_EDITOR DFM WARNING(SPMHDB-212) appears on opening some board files

2627054 ALLEGRO_EDITOR DRC_CONSTR Need CM formula to set Delta and Tolerance

2673755 ALLEGRO_EDITOR DRC_CONSTR After editing the constraint region, the board file exits unexpectedly

2674582 ALLEGRO_EDITOR DRC_CONSTR Same Net Spacing error is flagged when fillet is generated on the BBvia and cline with a tapering trace

2677369 ALLEGRO_EDITOR DRC_CONSTR Waived DRC errors reduce after updating DRC and saving the board file

2644173 ALLEGRO_EDITOR EDIT_ETCH Differential pair routing in broadside coupling only in layer L3

2541402 ALLEGRO_EDITOR GRAPHICS GPU graphics do not appear to support transparency

2653278 ALLEGRO_EDITOR GRAPHICS GPU: Drill Figures do not display after generating Drill Legend

2671216 ALLEGRO_EDITOR GRAPHICS Components randomly disappear when selected or highlighted in Allegro Symphony

2691835 ALLEGRO_EDITOR GRAPHICS Net names are not readable inside Shape/Pin/Cline

20359 ALLEGRO_EDITOR INTERACTIV Need ability to view clines and rats while editing or moving a symbol.

1668270 ALLEGRO_EDITOR INTERACTIV Prompted to save changes on exiting Allegro PCB Editor when opened in the Shape Edit application mode

2514959 ALLEGRO_EDITOR INTERACTIV Using ix and iy commands to copy and move objects is not working as expected in APD Plus

2610708 ALLEGRO_EDITOR INTERACTIV Unable to create a function key to snap to pad edge vertex in release 17.4-2019 HotFix 026

2610990 ALLEGRO_EDITOR INTERACTIV Unable to measure distance between two vertices with snap pick function keys

2624931 ALLEGRO_EDITOR INTERACTIV Conflicts between keyboard and mouse while vector editing lines, shapes, and traces

2642781 ALLEGRO_EDITOR INTERACTIV The Show-Measure shortcut (Shift + F4 key) is not working in release 17.4-2019 HotFix 025

2667215 ALLEGRO_EDITOR INTERACTIV Shrink Extends is not updating the Layout canvas unless the values are added manually

2683597 ALLEGRO_EDITOR INTERFACES PDF export uses net custom colors though 'Hide custom colors' is selected

2446648 ALLEGRO_EDITOR IN_DESIGN_ANA Improvements to scale behavior in the IR Drop analysis workflow

2643730 ALLEGRO_EDITOR IN_DESIGN_ANA PowerTree: Error SPMHGE-703 is reported and IR Drop Analysis result not loaded

2564903 ALLEGRO_EDITOR IPC Need to exclude finished and tool size from ipc2581_group_drill filter

2624953 ALLEGRO_EDITOR IPC Option to combine drill layers based on drill size in IPC 2581

2690737 ALLEGRO_EDITOR IPC Net short inconsistencies in the IPC-2581 and IPC-D-356 files

2578761 ALLEGRO_EDITOR MCAD_COLLAB Turn off the IDX enhanced mode for design exported with the mode turned on

2458759 ALLEGRO_EDITOR MULTI_USER Symphony outgoing updates occasionally stop being processed, causing lost work

2421838 ALLEGRO_EDITOR NC Allegro PCB Editor stops responding and sometimes crashes on running NC Drill

2630243 ALLEGRO_EDITOR OTHER The start page setup variable allegro_startpage_path is not working

2681574 ALLEGRO_EDITOR OTHER Enable offline editing of Allegro PCB Editor Start Page in the 17.4-2019 release and provide documentation

2685990 ALLEGRO_EDITOR OTHER Allegro PCB Editor start page customization not working in the 17.4-2019 release

2693308 ALLEGRO_EDITOR PADS_IN Running Route Automatic or Route Editor results in error about router quitting with exit code of 5

2148928 ALLEGRO_EDITOR PLACEMENT Place replicate update command selects objects which are not part of a module

2289562 ALLEGRO_EDITOR PLACEMENT Place replicate update command selects objects which are not part of a module

2649609 ALLEGRO_EDITOR PLACEMENT Save Find Filter settings for the via array command

2665069 ALLEGRO_EDITOR PLACEMENT Preview required after doing placement through QuickPlace

2190520 ALLEGRO_EDITOR SHAPE Automatically delete antenna and isolated shapes options have issues when thermal relief contact is set to Full Contact

2451965 ALLEGRO_EDITOR SHAPE Allegro PCB Editor crashes on Shape Parameters in Shape Edit app mode on Swedish version of Windows

2560062 ALLEGRO_EDITOR SHAPE Thermal relief connections missing

2684420 ALLEGRO_EDITOR SHAPE Allegro PCB Editor crashes on adding teardrops

2701562 ALLEGRO_EDITOR SHAPE Cannot delete manually-added voids to the Cavity shape

1903257 ALLEGRO_EDITOR SKILL Enhancement request for Pre and Post SKILL hooks

781814 ALLEGRO_EDITOR SKILL Provide access to SKILL functions related to the compose shape command

2603713 ALLEGRO_EDITOR STEP Enhance netrev -h to read step_mapping_path without requiring step_facet_path

2442288 ALLEGRO_EDITOR SYMBOL Layout - Renumber Pins not working for the PQFN package

2280209 ALLEGRO_EDITOR UI_GENERAL On Linux, TelSKILL window is not accepting input from the keyboard when the telskill_notty user preference is set

2305201 ALLEGRO_EDITOR UI_GENERAL SKILL window stops responding in release 17.4-2019

2356961 ALLEGRO_EDITOR UI_GENERAL SKILL window stops responding on Linux (RHE 7.8)

2493433 ALLEGRO_EDITOR UI_GENERAL Need settings to increase font size in telskill window

2519180 ALLEGRO_EDITOR UI_GENERAL set telskill command does not respond on Linux for release 17.4-2019

2582400 ALLEGRO_EDITOR UI_GENERAL Settings to increase font in telskill window

2592984 ALLEGRO_EDITOR UI_GENERAL Persisting issues with the 'Last' button in the Visibility panel: Not opening expected view

2657084 ALLEGRO_EDITOR UI_GENERAL Change font size in telskill window

2684426 ALLEGRO_EDITOR UI_GENERAL Add safe mode indication in the title bar

292305 ALLEGRO_EDITOR UI_GENERAL Support menus and error messages in a foreign language

2300949 ALLEGRO_LIB_CRT CORE Library Creator stops responding on applying 'Training/IPC-B (Design Technology)' rule to large STEP file

2319430 ALLEGRO_LIB_CRT CORE Allegro ECAD-MCAD Library Creator is unable to process 700 pins

2604255 ALLEGRO_LIB_CRT CORE Support the creation of STEP mapping file from Allegro ECAD-MCAD Library Creator

2545511 ALLEGRO_PROD_TOOLB INTEGRATION Allegro Productivity Toolbox features do not appear in the OrCAD PCB Editor menu

2526053 ALLEGRO_VIEWER OTHER New Allegro Free Physical Viewer gives an option to save the design

2600253 ALLEGRO_VIEWER OTHER Allegro Free Physical Viewer documentation should mention the [Alt] key instead of the [Shift] key for measurement

2519843 APD DEGASSING Degassing tool is not recognizing degassing hole overlap with voids

2426055 APD DIE_STACK_EDI Die stack editor not showing bumps for bottom die of two-sided die

2586794 APD DRAFTING Enable editing of dimensions by converting to texts, lines, and symbols

2591289 APD DXF_IF Thieving pattern created by advanced metal fill cannot be exported as DXF

2608496 APD EXPORT_DATA Export symbol spreadsheet does not work correctly for Pattern rotation options other than 0 degree

2631371 APD EXPORT_DATA Export Die-Text-Out option to export pre-CTE and post-CTE dies

2693873 APD EXPORT_DATA Die text-out wizard lost the padstack rotation, 225 becomes 135 degree

2683141 APD IMPORT_DATA Changing Orientation without using "flip placed symbol" option in Die Text-In wizard causing orientation to change

2625829 APD LOGIC Allegro Package Designer Plus, release 17.4-2019: Importing third-party netlist with part replace is not working.

2638898 APD OTHER Requesting that the Design Integrity checks find and clean a via within a via that does not span the same layers.

2649065 APD OTHER Package Integrity Check - Via-Pin Alignment Enhancement: Run check on selected symbol

2520567 APD SHAPE Different net shapes overlap without voiding each other

2624381 APD SHAPE Performance hit when doing a structure redefine.

2162705 APD STREAM_IF Allow APD/SiP options to export relative angle instead of just absolute angle when doing hierarchical streaming out

2671578 APD SYMB_EDIT_APP Add options for 45 degrees or user-defined degrees in change attributes

2616985 APD UI_GENERAL Cannot define specific funckeys in release 17.4-2019: ~1 (CTRL-1) not available

2680371 APD UI_GENERAL Last command recall behavior is broken in release 17.4-2019

2080288 APD WIREBOND Support stitch bonding in Allegro Package Designer Plus

2120084 APD WIREBOND Stitch bonding support in Allegro Package Designer Plus

2269050 APD WIREBOND Method for adjusting finger angle: Spin to angle and not only by specifying a value

2445218 APD WIREBOND Connect wire bond fingers with different net names

2627753 APD WIREBOND Method in Allegro Package Designer Plus to short bond fingers using a bond wire

2692794 APD WLP WLP: Exporting TIV that has NC nets causes crash

2415405 CAPTURE CONSTRAINT_MG Capture crashes on 'Synchronize Up' for certain licenses

2474865 CAPTURE CONSTRAINT_MG Environment Specific - Capture crashing when updating a part in the Design Cache using 17.4-2019 S016.

516444 CAPTURE SCHEMATIC_EDI Cut and paste in complex hierarchy resets RefDes

732857 CAPTURE SCHEMATIC_EDI Preserve reference on copy in occurrence level design

766867 CAPTURE SCHEMATIC_EDI Copy occurrence properties

985104 CAPTURE SCHEMATIC_EDI Preserve occurrence values on copy

2416428 CAPTURE_CLOUD WEB_BROWSER Symbol border is missing when project is opened in Capture on Cloud

2423887 CAPTURE_CLOUD WEB_BROWSER Capture Cloud symbol graphic discrepancies: horizontal lines are missing

2688745 CONCEPT_HDL CORE Unable to package the design after copying and pasting capacitor

2498631 CONSTRAINT_MGR ACC Loading PhysRule Table with Layer Index MIN_LINE_WIDTH smaller than Default CSet - reports MAX_LINE_WIDTH Internal error

2610320 CONSTRAINT_MGR INTERACTIV Issue with 'Select' popup command: Stops working after Assign Color

2572636 CONSTRAINT_MGR OTHER ECset not usable and will not update to Constraint Manager from Topology Workbench

2640078 CONSTRAINT_MGR OTHER Release 17.4-2019: Firefox is out-of-date

2691798 CONSTRAINT_MGR OTHER Update SKILL axlCNSSetSpacing and axlCNSSetSameNet to include constraint symbols to support expanded hole checks

2462216 CONSTRAINT_MGR SYSCAP System Capture schematic canvas attribute value does not update/refresh

2505306 CONSTRAINT_MGR SYSCAP Canvas is not updated after Attribute changed by SKILL API

1987745 CONSTRAINT_MGR XNET_DIFFPAIR System-level XNets require Design Link

2544523 DFM_WEB OTHER DFM portal images needs to be corrected

2602948 EAGLE_TRANSLATOR PCB_EDITOR CAD Translators menu on Linux missing third-party translator

2362417 INSTALLATION BASE Control file for installation should select the products.

2414991 INSTALLATION DOWNLOAD_MGR Specify Installation Directory for Download Manager during silent installation

2335760 PCB_LIBRARIAN SYMBOL_EDITOR Unable to control the pin name and pin type visibility in Symbol Editor.

2452112 PCB_LIBRARIAN SYMBOL_EDITOR Show coordinates of objects selected in Symbol Editor

2586760 PCB_LIBRARIAN SYMBOL_EDITOR Symbol Editor shows "pin name" inconsistently across interfaces

2266456 PCB_LIBRARIAN SYM_CREATOR_U Provide Text alignment and justification features in Symbol Editor

2146115 PSPICE MODELEDITOR Import CSV DMI does not work

2265452 PSPICE MODELEDITOR DMI is not working in Model Editor

2409947 PSPICE MODELEDITOR Cannot read Ports .csv file in DMI Template Code Generator

2476385 PSPICE MODELEDITOR Code imported in Model Editor using DMI translator gives compilation error

2484625 PSPICE MODELEDITOR PSpice DMI generation of Verilog-A model does not create .dll

2589656 PSPICE MODELEDITOR DMI template code generator in Model Editor, release 17.4-2019: Import CSV DMI does not work

2585275 PSPICE NETLISTER PSpice parameter is ignored during netlist without any warning in session log

690479 PSPICE SIMMODELS VPWL_FILE type option for EFREQ part: Supply frequencies in a table in a file

830331 PSPICE SIMMODELS VPWL_FILE type option for GFREQ part: Supply frequencies as a table in a file

2096124 PSPICE SIMULATOR Running simulations at temperature using Tcl produces very strange results

2544238 PSPICE SIMULATOR Temperature sweep result is different when a simulation is run through Tcl versus using GUI

2687849 PSPICE SIMULATOR Only one license used for parallel runs of psp_cmd on a machine by one user in batch mode

2443062 PSPICE TI_CONTRACT orSimSetup64 crashes followed by the message "RPC server unavailable"

2562872 PULSE ADHOC 'Pulse Projects' list in Open Projects dialog box displays the recently modified projects list in an incorrect order

2569778 PULSE ADHOC In team designs, page content is getting lost on updating designs.

2296889 PULSE CORE In OrCAD Capture, cannot log in to Search Providers for part information; getting error Error(SPDWSRV-621)

2428884 PULSE CORE Part placement performance worse in System Capture than DE-HDL

2492251 PULSE CORE Pulse not able to start on local system when there is a space in userprofile path

2520740 PULSE CORE Size of adwserver_http.out is growing every two hours by 10 GB

2619776 PULSE CORE Unified Search does not show some parts while searching.

2650534 PULSE CORE Pulse backup process stops responding

2706272 PULSE CORE Team collaboration license warning after Pulse upgrade

2675396 PULSE LIVEBOM Application_Type property in Live BOM displays a blank value

2685462 PULSE R2PLM-WC 'Publish for Manufacturing' publishing failed with ERROR (RCR-2051)

2669222 PULSE R2PLM Tools - Publish for Manufacturing does not launch; displays Error(PFM-120): Cannot connect to the file system.

2676889 PULSE R2PLM 'Publish for Manufacturing' publishing fails with ERROR - RCR-2079

2689265 PULSE R2PLM 'Publish for Manufacturing' stops responding if the design path contains a space.

2695211 PULSE R2PLM 'Publish for Manufacturing' error RWC-12036 caused by using 'Alternates' in Variant Editor

2692357 PULSE SERVER Pulse server went down pending a problem with a database shape element

2605803 PULSE UNIFIED_SEARC Support required for wildcard searches in Unified Search

2531760 PULSE VERSION_ON_SA File- Open Project defaults to Pulse project in non-Pulse managed environment

2586119 SIP_LAYOUT DEGASSING Export and import degassing parameters

2666511 SIP_LAYOUT DXF_IF Advanced shape degassing data cannot be exported in DXF

1924363 SIP_LAYOUT PLATING_BAR Plating bar check does not recognize net connected to Bar through another net

2045058 SIP_LAYOUT REPORTS Report value of CTE (coefficient of thermal expansion) compensation applied to symbols

2659525 SYSTEMSI COMMON Error on running sweep with "Enable Distributed Computing" but works if run without the option

2640874 SYSTEM_CAPTURE ADD_COMPONENT Allegro System Capture exits unexpectedly on part placement from Unified Search

2448518 SYSTEM_CAPTURE ADHOC Changes lost in design version history

2683312 SYSTEM_CAPTURE ARCHIVER Archive command when run on a hierarchical design does not archive the design blocks

2703002 SYSTEM_CAPTURE CAPTURE_IMPOR Migrating Capture design into System Capture fails; error DESIMP-435 - import of designs with Netgroups is not supported

2605427 SYSTEM_CAPTURE CONTEXT_MENUS When TOC page is active, custom menu items are inactive

2453355 SYSTEM_CAPTURE DESIGN_CORRUP Allegro System Capture: After placing title block on 'bluetooth block, shows cross icon; Part Manager shows all in sync

2624246 SYSTEM_CAPTURE EXPORT_PCB BPC20PILOT RF component from the schematic cannot be placed in the layout

2628277 SYSTEM_CAPTURE EXPORT_PCB Variant Editor in System Capture is not always saving data correctly on migrated designs.

2684226 SYSTEM_CAPTURE FIND_REPLACE Internal properties, CDS_LIBRARY_ID and CDS_LIBRARY_PHYSICAL_ID, displayed in Find and Replace

2640870 SYSTEM_CAPTURE IMPORT_BLOCK Import block selection menu does not display available blocks

2692703 SYSTEM_CAPTURE MODULE_ORDERI Module order is not preserved after importing design from DE-HDL to System Capture

2580614 SYSTEM_CAPTURE PACKAGER Outdated schematic template prevents copy/pasting from old designs

2680486 SYSTEM_CAPTURE PACKAGER Bypass or decoupling capacitor does not work if PHYS_DES_PREFIX of capacitor is not in chips but in ptf

2683837 SYSTEM_CAPTURE PACKAGER Pin Swap not working correctly on System Capture part

1842984 SYSTEM_CAPTURE PART_MANAGER Refresh to see updated page border on schematic

2101191 SYSTEM_CAPTURE PART_MANAGER Updated Page Border does not get refreshed

2700719 SYSTEM_CAPTURE PROJECT_EXPLO Esc key discards changes and closes the project

2681759 SYSTEM_CAPTURE REPORTS Schematic report does not work when executed on a hierarchical schematic.

2600396 SYSTEM_CAPTURE SCRIPTING con::applyPropStyle command does not read the CPM directive from the project.cpm file

2607240 SYSTEM_CAPTURE SCRIPTING NetInstance in db becomes Unknown in dbx

2642297 SYSTEM_CAPTURE SELECTION Unwanted selection of graphics objects

2690864 SYSTEM_CAPTURE SELECTION Grouped objects deselected on clicking pins

2566240 SYSTEM_CAPTURE SMART_PDF HotFix 022: SmartPDF prints vertical netnames with larger font

2489349 SYSTEM_CAPTURE UI Cannot minimize System Capture using minimize icon after selecting a new workspace

2554292 SYS_RELIABILITY ELEC_STRESS_D Filter changed to all or default on coming back to ERC schematic audit report

2486844 TOPXP ALLEGRO_INTEG Create constraints from Topology Workbench

2556040 TOPXP AMI_BUILDER Support MIPI C-PHY Tx model in AMI Builder

2559352 TOPXP AMI_BUILDER Add AMI model support for MIPI C-PHY

2592096 TOPXP CONSTRAINT_MA Option to set up 'Optional Pins' in Topology Workbench

2585028 TOPXP GUI Add 'Make same width' and 'Make same height' features in Topology Workbench like SystemSI

2588614 TOPXP GUI Ability to Use N Port without Autogenerated Pin names

2619017 TOPXP GUI Add a wildcard like "*" to filter the message

2634520 TOPXP GUI Topology Workbench FFT enhancements for PWL: periodic waveform and option to set start/end/repeat_period time

2635157 TOPXP GUI Current spectrum in SystemPI does not match the current time domain waveform.

2660889 TOPXP GUI Topology Workbench does not recognize pins and MCP sections of rigid-flex designs

2693534 TOPXP GUI Grid related issue in SystemSI/Topology Workbench: Cannot make bus connection during alignment of memory block

2605239 TOPXP SSIVIEWER Tcl support in SSI viewer

2585021 TOPXP SYSTEMPI Show selected probe in the main view for convenience

2024584 TOPXP SYSTEMSI Support different IBIS from various vendors in same canvas.

2024640 TOPXP SYSTEMSI Not able to assign EBD model

2700168 TOPXP TOPXPLORER Results not generated in Linux for topology in Topology Workbench

1806303 TOPXP VIA_WIZARD Improve accuracy and usability in via modeling in new System Explorer

CCRID Product ProductLevel2 Title

==============================================================================================

2462298 ADW DBEDITOR Unable to add value to the predefined values list in part classification when 'Restrict predefined values' is selected

2673073 ADW DBEDITOR Unable to check out schematic models in Allegro EDM Database Editor

2676082 ADW DBEDITOR Unable to check out schematic models in Allegro EDM Database Editor in release 17.4-2019, HotFix 030

2697393 ADW DBEDITOR Allegro EDM Database Editor is slow to use in release 17.4-2019

2697566 ADW DBEDITOR The release time for EDM models is significantly higher in release 17.4-2019, HotFix 030

2553658 ADW LRM When updating a block in the design using LRM, it is not adding the new part in the block, so Packager then fails after

2693395 ADW PART_MANAGER Placing a new part in a design shows the part as out of sync

2664409 ALLEGROX 3D_CANVAS 3D Aware Placement: checking spacing requirements for components using 3D geometry of associated components

2115283 ALLEGRO_EDITOR 3D_CANVAS Bend function is grayed out in Allegro 3D Canvas

2352077 ALLEGRO_EDITOR 3D_CANVAS SILKSCREEN mapped for Flex zones

2454283 ALLEGRO_EDITOR 3D_CANVAS PCB Editor stops responding after invoking 3D Canvas

2456820 ALLEGRO_EDITOR 3D_CANVAS 3D Viewer: Micro vias are not showing correctly in release 17.4-2019, HotFix 014 or later

2461978 ALLEGRO_EDITOR 3D_CANVAS STEP model appears deformed and smaller in 3D Canvas

2525936 ALLEGRO_EDITOR 3D_CANVAS STEP model appears oversized in 3D Canvas

2637074 ALLEGRO_EDITOR 3D_CANVAS Need new graphics engine for 3D Canvas

2558947 ALLEGRO_EDITOR DATABASE Zone Manager Mapping Issue

2565249 ALLEGRO_EDITOR DATABASE Unable to select a stackup when it is set to anything other than Primary

2644792 ALLEGRO_EDITOR DATABASE ERROR: Detected subclass BOTTOM is a zone surface but not identified in design.

2682310 ALLEGRO_EDITOR DATABASE Cadence 17.4 padstack definition on SKILL

2687247 ALLEGRO_EDITOR DATABASE Database gets corrupted when saved after moving a few components

2696887 ALLEGRO_EDITOR DATABASE DRC marker disappears despite being set to visible when the layer of the attached object is invisible

2057590 ALLEGRO_EDITOR DFM FILLED RECTANGLE or LINE objects cannot work as gang mask at the Slivers of DFF constraints

2604294 ALLEGRO_EDITOR DFM WARNING(SPMHDB-212) appears on opening some board files

2627054 ALLEGRO_EDITOR DRC_CONSTR Need CM formula to set Delta and Tolerance

2673755 ALLEGRO_EDITOR DRC_CONSTR After editing the constraint region, the board file exits unexpectedly

2674582 ALLEGRO_EDITOR DRC_CONSTR Same Net Spacing error is flagged when fillet is generated on the BBvia and cline with a tapering trace

2677369 ALLEGRO_EDITOR DRC_CONSTR Waived DRC errors reduce after updating DRC and saving the board file

2644173 ALLEGRO_EDITOR EDIT_ETCH Differential pair routing in broadside coupling only in layer L3

2541402 ALLEGRO_EDITOR GRAPHICS GPU graphics do not appear to support transparency

2653278 ALLEGRO_EDITOR GRAPHICS GPU: Drill Figures do not display after generating Drill Legend

2671216 ALLEGRO_EDITOR GRAPHICS Components randomly disappear when selected or highlighted in Allegro Symphony

2691835 ALLEGRO_EDITOR GRAPHICS Net names are not readable inside Shape/Pin/Cline

20359 ALLEGRO_EDITOR INTERACTIV Need ability to view clines and rats while editing or moving a symbol.

1668270 ALLEGRO_EDITOR INTERACTIV Prompted to save changes on exiting Allegro PCB Editor when opened in the Shape Edit application mode

2514959 ALLEGRO_EDITOR INTERACTIV Using ix and iy commands to copy and move objects is not working as expected in APD Plus

2610708 ALLEGRO_EDITOR INTERACTIV Unable to create a function key to snap to pad edge vertex in release 17.4-2019 HotFix 026

2610990 ALLEGRO_EDITOR INTERACTIV Unable to measure distance between two vertices with snap pick function keys

2624931 ALLEGRO_EDITOR INTERACTIV Conflicts between keyboard and mouse while vector editing lines, shapes, and traces

2642781 ALLEGRO_EDITOR INTERACTIV The Show-Measure shortcut (Shift + F4 key) is not working in release 17.4-2019 HotFix 025

2667215 ALLEGRO_EDITOR INTERACTIV Shrink Extends is not updating the Layout canvas unless the values are added manually

2683597 ALLEGRO_EDITOR INTERFACES PDF export uses net custom colors though 'Hide custom colors' is selected

2446648 ALLEGRO_EDITOR IN_DESIGN_ANA Improvements to scale behavior in the IR Drop analysis workflow

2643730 ALLEGRO_EDITOR IN_DESIGN_ANA PowerTree: Error SPMHGE-703 is reported and IR Drop Analysis result not loaded

2564903 ALLEGRO_EDITOR IPC Need to exclude finished and tool size from ipc2581_group_drill filter

2624953 ALLEGRO_EDITOR IPC Option to combine drill layers based on drill size in IPC 2581

2690737 ALLEGRO_EDITOR IPC Net short inconsistencies in the IPC-2581 and IPC-D-356 files

2578761 ALLEGRO_EDITOR MCAD_COLLAB Turn off the IDX enhanced mode for design exported with the mode turned on

2458759 ALLEGRO_EDITOR MULTI_USER Symphony outgoing updates occasionally stop being processed, causing lost work

2421838 ALLEGRO_EDITOR NC Allegro PCB Editor stops responding and sometimes crashes on running NC Drill

2630243 ALLEGRO_EDITOR OTHER The start page setup variable allegro_startpage_path is not working

2681574 ALLEGRO_EDITOR OTHER Enable offline editing of Allegro PCB Editor Start Page in the 17.4-2019 release and provide documentation

2685990 ALLEGRO_EDITOR OTHER Allegro PCB Editor start page customization not working in the 17.4-2019 release

2693308 ALLEGRO_EDITOR PADS_IN Running Route Automatic or Route Editor results in error about router quitting with exit code of 5

2148928 ALLEGRO_EDITOR PLACEMENT Place replicate update command selects objects which are not part of a module

2289562 ALLEGRO_EDITOR PLACEMENT Place replicate update command selects objects which are not part of a module

2649609 ALLEGRO_EDITOR PLACEMENT Save Find Filter settings for the via array command

2665069 ALLEGRO_EDITOR PLACEMENT Preview required after doing placement through QuickPlace

2190520 ALLEGRO_EDITOR SHAPE Automatically delete antenna and isolated shapes options have issues when thermal relief contact is set to Full Contact

2451965 ALLEGRO_EDITOR SHAPE Allegro PCB Editor crashes on Shape Parameters in Shape Edit app mode on Swedish version of Windows

2560062 ALLEGRO_EDITOR SHAPE Thermal relief connections missing

2684420 ALLEGRO_EDITOR SHAPE Allegro PCB Editor crashes on adding teardrops

2701562 ALLEGRO_EDITOR SHAPE Cannot delete manually-added voids to the Cavity shape

1903257 ALLEGRO_EDITOR SKILL Enhancement request for Pre and Post SKILL hooks

781814 ALLEGRO_EDITOR SKILL Provide access to SKILL functions related to the compose shape command

2603713 ALLEGRO_EDITOR STEP Enhance netrev -h to read step_mapping_path without requiring step_facet_path

2442288 ALLEGRO_EDITOR SYMBOL Layout - Renumber Pins not working for the PQFN package

2280209 ALLEGRO_EDITOR UI_GENERAL On Linux, TelSKILL window is not accepting input from the keyboard when the telskill_notty user preference is set

2305201 ALLEGRO_EDITOR UI_GENERAL SKILL window stops responding in release 17.4-2019

2356961 ALLEGRO_EDITOR UI_GENERAL SKILL window stops responding on Linux (RHE 7.8)

2493433 ALLEGRO_EDITOR UI_GENERAL Need settings to increase font size in telskill window

2519180 ALLEGRO_EDITOR UI_GENERAL set telskill command does not respond on Linux for release 17.4-2019

2582400 ALLEGRO_EDITOR UI_GENERAL Settings to increase font in telskill window

2592984 ALLEGRO_EDITOR UI_GENERAL Persisting issues with the 'Last' button in the Visibility panel: Not opening expected view

2657084 ALLEGRO_EDITOR UI_GENERAL Change font size in telskill window

2684426 ALLEGRO_EDITOR UI_GENERAL Add safe mode indication in the title bar

292305 ALLEGRO_EDITOR UI_GENERAL Support menus and error messages in a foreign language

2300949 ALLEGRO_LIB_CRT CORE Library Creator stops responding on applying 'Training/IPC-B (Design Technology)' rule to large STEP file

2319430 ALLEGRO_LIB_CRT CORE Allegro ECAD-MCAD Library Creator is unable to process 700 pins

2604255 ALLEGRO_LIB_CRT CORE Support the creation of STEP mapping file from Allegro ECAD-MCAD Library Creator

2545511 ALLEGRO_PROD_TOOLB INTEGRATION Allegro Productivity Toolbox features do not appear in the OrCAD PCB Editor menu

2526053 ALLEGRO_VIEWER OTHER New Allegro Free Physical Viewer gives an option to save the design

2600253 ALLEGRO_VIEWER OTHER Allegro Free Physical Viewer documentation should mention the [Alt] key instead of the [Shift] key for measurement

2519843 APD DEGASSING Degassing tool is not recognizing degassing hole overlap with voids

2426055 APD DIE_STACK_EDI Die stack editor not showing bumps for bottom die of two-sided die

2586794 APD DRAFTING Enable editing of dimensions by converting to texts, lines, and symbols

2591289 APD DXF_IF Thieving pattern created by advanced metal fill cannot be exported as DXF

2608496 APD EXPORT_DATA Export symbol spreadsheet does not work correctly for Pattern rotation options other than 0 degree

2631371 APD EXPORT_DATA Export Die-Text-Out option to export pre-CTE and post-CTE dies

2693873 APD EXPORT_DATA Die text-out wizard lost the padstack rotation, 225 becomes 135 degree

2683141 APD IMPORT_DATA Changing Orientation without using "flip placed symbol" option in Die Text-In wizard causing orientation to change

2625829 APD LOGIC Allegro Package Designer Plus, release 17.4-2019: Importing third-party netlist with part replace is not working.

2638898 APD OTHER Requesting that the Design Integrity checks find and clean a via within a via that does not span the same layers.

2649065 APD OTHER Package Integrity Check - Via-Pin Alignment Enhancement: Run check on selected symbol

2520567 APD SHAPE Different net shapes overlap without voiding each other

2624381 APD SHAPE Performance hit when doing a structure redefine.

2162705 APD STREAM_IF Allow APD/SiP options to export relative angle instead of just absolute angle when doing hierarchical streaming out

2671578 APD SYMB_EDIT_APP Add options for 45 degrees or user-defined degrees in change attributes

2616985 APD UI_GENERAL Cannot define specific funckeys in release 17.4-2019: ~1 (CTRL-1) not available

2680371 APD UI_GENERAL Last command recall behavior is broken in release 17.4-2019

2080288 APD WIREBOND Support stitch bonding in Allegro Package Designer Plus

2120084 APD WIREBOND Stitch bonding support in Allegro Package Designer Plus

2269050 APD WIREBOND Method for adjusting finger angle: Spin to angle and not only by specifying a value

2445218 APD WIREBOND Connect wire bond fingers with different net names

2627753 APD WIREBOND Method in Allegro Package Designer Plus to short bond fingers using a bond wire

2692794 APD WLP WLP: Exporting TIV that has NC nets causes crash

2415405 CAPTURE CONSTRAINT_MG Capture crashes on 'Synchronize Up' for certain licenses

2474865 CAPTURE CONSTRAINT_MG Environment Specific - Capture crashing when updating a part in the Design Cache using 17.4-2019 S016.

516444 CAPTURE SCHEMATIC_EDI Cut and paste in complex hierarchy resets RefDes

732857 CAPTURE SCHEMATIC_EDI Preserve reference on copy in occurrence level design

766867 CAPTURE SCHEMATIC_EDI Copy occurrence properties

985104 CAPTURE SCHEMATIC_EDI Preserve occurrence values on copy

2416428 CAPTURE_CLOUD WEB_BROWSER Symbol border is missing when project is opened in Capture on Cloud

2423887 CAPTURE_CLOUD WEB_BROWSER Capture Cloud symbol graphic discrepancies: horizontal lines are missing

2688745 CONCEPT_HDL CORE Unable to package the design after copying and pasting capacitor

2498631 CONSTRAINT_MGR ACC Loading PhysRule Table with Layer Index MIN_LINE_WIDTH smaller than Default CSet - reports MAX_LINE_WIDTH Internal error

2610320 CONSTRAINT_MGR INTERACTIV Issue with 'Select' popup command: Stops working after Assign Color

2572636 CONSTRAINT_MGR OTHER ECset not usable and will not update to Constraint Manager from Topology Workbench

2640078 CONSTRAINT_MGR OTHER Release 17.4-2019: Firefox is out-of-date

2691798 CONSTRAINT_MGR OTHER Update SKILL axlCNSSetSpacing and axlCNSSetSameNet to include constraint symbols to support expanded hole checks

2462216 CONSTRAINT_MGR SYSCAP System Capture schematic canvas attribute value does not update/refresh

2505306 CONSTRAINT_MGR SYSCAP Canvas is not updated after Attribute changed by SKILL API

1987745 CONSTRAINT_MGR XNET_DIFFPAIR System-level XNets require Design Link

2544523 DFM_WEB OTHER DFM portal images needs to be corrected

2602948 EAGLE_TRANSLATOR PCB_EDITOR CAD Translators menu on Linux missing third-party translator

2362417 INSTALLATION BASE Control file for installation should select the products.

2414991 INSTALLATION DOWNLOAD_MGR Specify Installation Directory for Download Manager during silent installation

2335760 PCB_LIBRARIAN SYMBOL_EDITOR Unable to control the pin name and pin type visibility in Symbol Editor.

2452112 PCB_LIBRARIAN SYMBOL_EDITOR Show coordinates of objects selected in Symbol Editor

2586760 PCB_LIBRARIAN SYMBOL_EDITOR Symbol Editor shows "pin name" inconsistently across interfaces

2266456 PCB_LIBRARIAN SYM_CREATOR_U Provide Text alignment and justification features in Symbol Editor

2146115 PSPICE MODELEDITOR Import CSV DMI does not work

2265452 PSPICE MODELEDITOR DMI is not working in Model Editor

2409947 PSPICE MODELEDITOR Cannot read Ports .csv file in DMI Template Code Generator

2476385 PSPICE MODELEDITOR Code imported in Model Editor using DMI translator gives compilation error

2484625 PSPICE MODELEDITOR PSpice DMI generation of Verilog-A model does not create .dll

2589656 PSPICE MODELEDITOR DMI template code generator in Model Editor, release 17.4-2019: Import CSV DMI does not work

2585275 PSPICE NETLISTER PSpice parameter is ignored during netlist without any warning in session log

690479 PSPICE SIMMODELS VPWL_FILE type option for EFREQ part: Supply frequencies in a table in a file

830331 PSPICE SIMMODELS VPWL_FILE type option for GFREQ part: Supply frequencies as a table in a file

2096124 PSPICE SIMULATOR Running simulations at temperature using Tcl produces very strange results

2544238 PSPICE SIMULATOR Temperature sweep result is different when a simulation is run through Tcl versus using GUI

2687849 PSPICE SIMULATOR Only one license used for parallel runs of psp_cmd on a machine by one user in batch mode

2443062 PSPICE TI_CONTRACT orSimSetup64 crashes followed by the message "RPC server unavailable"

2562872 PULSE ADHOC 'Pulse Projects' list in Open Projects dialog box displays the recently modified projects list in an incorrect order

2569778 PULSE ADHOC In team designs, page content is getting lost on updating designs.

2296889 PULSE CORE In OrCAD Capture, cannot log in to Search Providers for part information; getting error Error(SPDWSRV-621)

2428884 PULSE CORE Part placement performance worse in System Capture than DE-HDL

2492251 PULSE CORE Pulse not able to start on local system when there is a space in userprofile path

2520740 PULSE CORE Size of adwserver_http.out is growing every two hours by 10 GB

2619776 PULSE CORE Unified Search does not show some parts while searching.

2650534 PULSE CORE Pulse backup process stops responding

2706272 PULSE CORE Team collaboration license warning after Pulse upgrade

2675396 PULSE LIVEBOM Application_Type property in Live BOM displays a blank value

2685462 PULSE R2PLM-WC 'Publish for Manufacturing' publishing failed with ERROR (RCR-2051)

2669222 PULSE R2PLM Tools - Publish for Manufacturing does not launch; displays Error(PFM-120): Cannot connect to the file system.

2676889 PULSE R2PLM 'Publish for Manufacturing' publishing fails with ERROR - RCR-2079

2689265 PULSE R2PLM 'Publish for Manufacturing' stops responding if the design path contains a space.

2695211 PULSE R2PLM 'Publish for Manufacturing' error RWC-12036 caused by using 'Alternates' in Variant Editor

2692357 PULSE SERVER Pulse server went down pending a problem with a database shape element

2605803 PULSE UNIFIED_SEARC Support required for wildcard searches in Unified Search

2531760 PULSE VERSION_ON_SA File- Open Project defaults to Pulse project in non-Pulse managed environment

2586119 SIP_LAYOUT DEGASSING Export and import degassing parameters

2666511 SIP_LAYOUT DXF_IF Advanced shape degassing data cannot be exported in DXF

1924363 SIP_LAYOUT PLATING_BAR Plating bar check does not recognize net connected to Bar through another net

2045058 SIP_LAYOUT REPORTS Report value of CTE (coefficient of thermal expansion) compensation applied to symbols

2659525 SYSTEMSI COMMON Error on running sweep with "Enable Distributed Computing" but works if run without the option

2640874 SYSTEM_CAPTURE ADD_COMPONENT Allegro System Capture exits unexpectedly on part placement from Unified Search

2448518 SYSTEM_CAPTURE ADHOC Changes lost in design version history

2683312 SYSTEM_CAPTURE ARCHIVER Archive command when run on a hierarchical design does not archive the design blocks

2703002 SYSTEM_CAPTURE CAPTURE_IMPOR Migrating Capture design into System Capture fails; error DESIMP-435 - import of designs with Netgroups is not supported

2605427 SYSTEM_CAPTURE CONTEXT_MENUS When TOC page is active, custom menu items are inactive

2453355 SYSTEM_CAPTURE DESIGN_CORRUP Allegro System Capture: After placing title block on 'bluetooth block, shows cross icon; Part Manager shows all in sync

2624246 SYSTEM_CAPTURE EXPORT_PCB BPC20PILOT RF component from the schematic cannot be placed in the layout

2628277 SYSTEM_CAPTURE EXPORT_PCB Variant Editor in System Capture is not always saving data correctly on migrated designs.

2684226 SYSTEM_CAPTURE FIND_REPLACE Internal properties, CDS_LIBRARY_ID and CDS_LIBRARY_PHYSICAL_ID, displayed in Find and Replace

2640870 SYSTEM_CAPTURE IMPORT_BLOCK Import block selection menu does not display available blocks

2692703 SYSTEM_CAPTURE MODULE_ORDERI Module order is not preserved after importing design from DE-HDL to System Capture

2580614 SYSTEM_CAPTURE PACKAGER Outdated schematic template prevents copy/pasting from old designs

2680486 SYSTEM_CAPTURE PACKAGER Bypass or decoupling capacitor does not work if PHYS_DES_PREFIX of capacitor is not in chips but in ptf

2683837 SYSTEM_CAPTURE PACKAGER Pin Swap not working correctly on System Capture part

1842984 SYSTEM_CAPTURE PART_MANAGER Refresh to see updated page border on schematic

2101191 SYSTEM_CAPTURE PART_MANAGER Updated Page Border does not get refreshed

2700719 SYSTEM_CAPTURE PROJECT_EXPLO Esc key discards changes and closes the project

2681759 SYSTEM_CAPTURE REPORTS Schematic report does not work when executed on a hierarchical schematic.

2600396 SYSTEM_CAPTURE SCRIPTING con::applyPropStyle command does not read the CPM directive from the project.cpm file

2607240 SYSTEM_CAPTURE SCRIPTING NetInstance in db becomes Unknown in dbx

2642297 SYSTEM_CAPTURE SELECTION Unwanted selection of graphics objects

2690864 SYSTEM_CAPTURE SELECTION Grouped objects deselected on clicking pins

2566240 SYSTEM_CAPTURE SMART_PDF HotFix 022: SmartPDF prints vertical netnames with larger font

2489349 SYSTEM_CAPTURE UI Cannot minimize System Capture using minimize icon after selecting a new workspace

2554292 SYS_RELIABILITY ELEC_STRESS_D Filter changed to all or default on coming back to ERC schematic audit report

2486844 TOPXP ALLEGRO_INTEG Create constraints from Topology Workbench

2556040 TOPXP AMI_BUILDER Support MIPI C-PHY Tx model in AMI Builder

2559352 TOPXP AMI_BUILDER Add AMI model support for MIPI C-PHY

2592096 TOPXP CONSTRAINT_MA Option to set up 'Optional Pins' in Topology Workbench

2585028 TOPXP GUI Add 'Make same width' and 'Make same height' features in Topology Workbench like SystemSI

2588614 TOPXP GUI Ability to Use N Port without Autogenerated Pin names

2619017 TOPXP GUI Add a wildcard like "*" to filter the message

2634520 TOPXP GUI Topology Workbench FFT enhancements for PWL: periodic waveform and option to set start/end/repeat_period time

2635157 TOPXP GUI Current spectrum in SystemPI does not match the current time domain waveform.

2660889 TOPXP GUI Topology Workbench does not recognize pins and MCP sections of rigid-flex designs

2693534 TOPXP GUI Grid related issue in SystemSI/Topology Workbench: Cannot make bus connection during alignment of memory block

2605239 TOPXP SSIVIEWER Tcl support in SSI viewer

2585021 TOPXP SYSTEMPI Show selected probe in the main view for convenience

2024584 TOPXP SYSTEMSI Support different IBIS from various vendors in same canvas.

2024640 TOPXP SYSTEMSI Not able to assign EBD model

2700168 TOPXP TOPXPLORER Results not generated in Linux for topology in Topology Workbench

1806303 TOPXP VIA_WIZARD Improve accuracy and usability in via modeling in new System Explorer

Cadence Allegro PCB Design helps bring your innovative and bleeding-edge designs to life. The constraint-driven environment provides real-time visual feedback and ensures the functionality and manufacturability of your PCBs while allowing you to keep designing.

OrCAD is a driving force in the PCB design industry. In order to help desingers keep up with the constant pace of change Cadence has been accelerating the pace of innovation delivering a stream of updates and product enhancements to users. OrCAD provides insight into industry-first capabilities made available to customers such as real-time design, DesignTrue DFM, constraint manager, in-design analysis, and more. In July of 1999, OrCAD and its product line were acquired by Cadence Design Systems. OrCAD integrated with Cadence Allegro PCB design software creating a fully scalable solution for solving any level of PCB design challenge.

Cadence PCB Suites and Options 2022

Here we explore the various features of the Cadence PCB Suites and options.

Cadence enables global electronic design innovation and plays an essential role in the creation of today’s integrated circuits and electronics. Customers use Cadence software, hardware, IP and services to design and verify advanced semiconductors, consumer electronics, networking and telecommunications equipment, and computer systems. The company is headquartered in San Jose, Calif., with sales offices, design centers and research facilities around the world to serve the global electronics industry.

Product: Cadence Allegro and OrCAD

Version: 22.1-2022 P001 (10/6/2022) Base release

Supported Architectures: x64

Website Home Page : www.cadence.com

Languages Supported: english

System Requirements: Windows *

Size: 9.8 Gb

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please