Cadence INNOVUS 21.17.000-ISR7 | 61.0 Gb

Cadence Design Systems, Inc. , the leader in global electronic design innovation, has unveiled INNOVUS 21.17.000-ISR7 is next-generation physical implementation solution that enables system-on-chip (SoC) developers to deliver designs with best-in-class power, performance and area (PPA) while accelerating time to market.

CCMPR02768014 Hang issue after showing useful skew

CCMPR02763965 routeDesign SEGV

CCMPR02762770 Crash in routing

CCMPR02760206 editAddTrimMetal adds incorrect CM0 trim shape color when inst is mask_shift

CCMPR02759206 The add_stripes command is creating P/G stripes outside the rectilinear core boundary

CCMPR02758807 Objects of type guiPoly cannot be moved

CCMPR02758788 NanoRoute/verify_drc.

CCMPR02757033 Innovus recognizes wrong via group

CCMPR02756955 route_eco -fix_drc causing off Grid Trim Center violations

CCMPR02756628 "editPowerVia" does not consider SMAC(SAMEMETALALIGNEDCUT) violation during inserting post staple via

CCMPR02756289 ecoRoute leaves some CM0 patch wires DRC violations

CCMPR02756282 add_target_pg is removing existing wires and vias which is causing extra opens

CCMPR02755977 Innovus does not report a violation

CCMPR02755424 Column-mode secondary PG causing MaxViaStack violations even with -shape COREWIRE

CCMPR02755334 Column-mode secondary PG missing some vias on upper layers

CCMPR02755322 read_power_intent should support add_supply_state in UPF 3.0

CCMPR02755319 Run time is much longer when using 'set_dc_sources power_switch' in a design without power switches

CCMPR02754962 Observing high runtime for defOut -selected -with_shield -routing

CCMPR02754869 Tool is not able to fix Hold Violation on Q to SI path in design if net connected to different power domain cells

CCMPR02754160 When inserted passive fill, another mask's X3 trim is overlapped on the existing X3 Trim

CCMPR02754017 The check_place command causes instances with place_status unplaced become placed

CCMPR02754013 Fill gap occurs due to not aware edge constraint of rectilinear cell

CCMPR02753251 Create a new process node

CCMPR02753058 passiveFill does not consider obstructs by mask and creates trims on trim blk randomly

CCMPR02752675 Wrong voltage libraries picked for AON cells

CCMPR02752632 NRHF local build does not finish PG routing more than 6 hours for all PG nets 1 shot test

CCMPR02752388 verify_drc reports a false D12 MAR violation

CCMPR02752348 route_opt_design crash at the start of global routing iteration 6

CCMPR02752050 check_macro_place_constraint fails with **ERROR: (IMPTCM-48): narrowChannel is not a legal option for command

CCMPR02750835 Backside clock routing results in SEGV during the NR import stage

CCMPR02750801 ecoRoute memory overshoot during detail route and getting killed

CCMPR02750697 deletePowerSwitch -instanceList is deleting the connections for other PS which are not related to the deleted PS

CCMPR02750490 EndOfLine_Keepout DRCs coming over m1 in Innovus

CCMPR02750487 False report of inst overlap within setup_instance_pin_pitch_access()

CCMPR02750067 Why does the ring pin of IO filler cell connect to bump when it does viewBumpConnection?

CCMPR02749383 SE to SE end of line spacing violation using native tool command

CCMPR02748704 editPowerVia -add_vias created overlapping vias between M15 and AP

CCMPR02748454 Hang/Unable to complete adding pre staple V1 via between M1 and M2 power rails

CCMPR02748011 Random power improvements with minor change in netlists

CCMPR02747933 Tool flags "Wire width on non-uniform track" violation on port with wide width on NDR Track

CCMPR02747821 DIAG during place_opt_design step

CCMPR02747777 The X1 trim violation not fixed by "ecoRoute -fix_filler_drc_with_patch_only" after insertion filler

CCMPR02747589 add_target_pg used for secondary PG routing not handling maxViaStack rule correctly

CCMPR02747580 check_place flagging false Diff Core Edge Length violation

CCMPR02747559 Make Adaptive Density Function (V2) default

CCMPR02747466 Tool is exiting during the saveNetlist command

CCMPR02747456 Run crashing during the post route opt step

CCMPR02747255 Global placement crash with 32 local CPU

CCMPR02747175 Multibit combo merging/split SEGV

CCMPR02746954 ecoRoute -fix_filler_drc_with_patch_only cannot fix M1 violation on DCAP cells

CCMPR02746935 Add an exp option to have area crr honor power

CCMPR02746796 identify_physical_power_domains fails when extra_supply is an empty list

CCMPR02746537 IO pin display not visible issue

CCMPR02746417 Innovus tQRC extraction SEGV with backside metal extraction at set_used_viamap_vias

CCMPR02745926 streamOut is consuming 5X runtime

CCMPR02745730 Trim layer GUI support request

CCMPR02745709 Passivefill support request

CCMPR02745706 Innovus commit_partition not creating physical ports for special nets during pushdown

CCMPR02745654 Crash at the CTS stage

CCMPR02745613 -flatten_bus flag causes write_netlist -include_pg to use 1'b0 instead of vss

CCMPR02745383 place_design -noPrePlaceOpt ERROR (IMPSP-190) with FP mode after checkPlace

CCMPR02745280 M2 off_trim_grid from NR and not Verify

CCMPR02745056 routeDesign crash during data preparation

CCMPR02744892 Crash during ecoRoute -fix_drc

CCMPR02744744 assembleDesign not transforming trim shapes in the block

CCMPR02744646 place_opt_design crashes when via pillars are assigned

CCMPR02744159 Filler gap violation: add_fillers left the filler gap and trigger implant/pre-route violations

CCMPR02744137 Unable to create PG stripe over partition pins

CCMPR02743893 Router creating shorts when large inverter requires via pillars on input and output

CCMPR02743615 optDesign -postCTS hang in 21.15 & 22.30

CCMPR02743466 Make eDR default

CCMPR02743352 DRCs when routing next to cell with M3 pins because router used wrong tracks

CCMPR02742938 addFiller adding huge number of fillers when there are no vertical max stack violations

CCMPR02742746 Routing short with Innovus

CCMPR02742665 Non-fatal error during TQuantus extraction inside Innovus

CCMPR02742645 Routing creating short with routing blockage

CCMPR02742392 deleteRoutingHalo complains error IMPSYC-2210 and fails

CCMPR02742123 M0 Stub routing has longer M0 routes

CCMPR02741898 Need fcroute to route 45deg with short distant

CCMPR02741880 SEGV during routeopt

CCMPR02741832 write_lef_abstract freezes or too slow on bump design

CCMPR02741563 There are a lot of messages about DIAG when refinePlace

CCMPR02741400 Tied Net has Multiple fingers connected by same layer jogging causes Directional Span Length Spacing

CCMPR02741041 False enclosure DRC violation issue

CCMPR02740987 addPowerSwitch crash

CCMPR02740954 endcap tap swap fails if power switches inserted before well tap

CCMPR02740891 Diff Layer Cut Spacing (VIA5 to VIA6 spacing DRCs)

CCMPR02740889 Stack trace error in the postCTS stage

CCMPR02740744 route_design creating EndOfLine Keepout DRC violations

CCMPR02740567 Timer update during PBA ecoRoute

CCMPR02740529 M2 Shorts caused

CCMPR02740456 [SEGV when querying macro after populating data structures

CCMPR02739904 Crash during the finish stage

CCMPR02739859 iSpatial left unloaded buffers after MB merging

CCMPR02739804 Observing crash during the addEndCap command

CCMPR02739292 Crash during VSS power hookup insertion

CCMPR02738788 Hang issue on global routing with shielding done on clock spine net

CCMPR02738051 Innovus crashes at the Place stage

CCMPR02738033 Wrong operation of editPowerVia according to number of CPU count

CCMPR02738007 ViewBumpConnection is not working properly

CCMPR02737980 Remove existing vias when DRC occurs between vias during editAddRoute

CCMPR02737932 Tool hangs after first iteration of optDesign and ecoRoute call in routeOpt

CCMPR02737875 add_target_pg false WARN: M3 spacing(0.060000) is less than the minimum parallel spacing(0.087000) on layer M3

CCMPR02737846 dbNetExtrRCSummary reporting resistance 0 after clock

CCMPR02737302 False IMPSP-376 alarm

CCMPR02737252 Remove assign is adding buffers in wrong domain causing **ERROR: (IMPCCOPT-1044)

CCMPR02736985 place_opt_design crashes during global placement

CCMPR02736702 POD is crashing with power effort set to none

CCMPR02736520 add_target_pg is missing via when choosing incorrect track for connection

CCMPR02736501 MaxViaStack violations on Clock Shield nets

CCMPR02736114 add_target_pg used for secPG routing needs user option to choose shape type for added wires and vias

CCMPR02735984 route_pg causes IMPDF-1064 error

CCMPR02735494 Reduce the runtime of "ecoRoute -fix_filler_drc_with_patch_only"

CCMPR02735334 verify_drc does not mark violations

CCMPR02735331 Flag false MAXVIASTACK violations

CCMPR02735320 place_opt_design not able to reorder scan chain with back2back ordered section

CCMPR02735154 D10 Metal shorts in PG with the addStripe command

CCMPR02735028 refinePlace flag False Pin Access violations

CCMPR02734326 Innovus crashes at the check_library command

CCMPR02733563 SEGV during routeOpt

CCMPR02733404 NDR bottom-preferred layer demotion causing Timing Degradation

CCMPR02733313 Make floorplan "isCore2Io" WRITE-able

CCMPR02733311 SEGV when running the write_physical_context_data command when macros involved

CCMPR02733302 Secondary PG is failing to connect some tap cell pins

CCMPR02733050 addRepeaterByRule adding back to back buffers

CCMPR02732586 **ERROR: Failed to re-stitch scan chain, *** BAD SCAN ASSIGNMENT ***

CCMPR02732546 Crash in editChangeVia -selected

CCMPR02732539 Pin placements are getting dropped after the partition command

CCMPR02731965 Presence of pre-placed cells leaves untapped areas

CCMPR02731841 verifyProcessAntenna crashes

CCMPR02731839 Unexpected Incompatible Resizing done" in routeOpt

CCMPR02731820 Excessive runtime in CommonAndConstantInputSimplification transform in areaOpt

CCMPR02731799 1CPP gap is required if RX transition between cells is more than 10nm

CCMPR02731639 Total Power degradation when enabling Power Density Map

CCMPR02731437 Tool is not able to fix hold violation

CCMPR02731198 Isolation cells moved to opposite end of block from run-to-run

CCMPR02731129 Seeing DRCs after via pillar implementation

CCMPR02730743 Custom Box/gui_shape cannot be resized

CCMPR02730510 Crash during route_design

CCMPR02730480 Innovus crashes in route_pg

CCMPR02730394 FlashPG crash with VARIABLE numerical expression

CCMPR02730349 NRHF side shielding got SEGV with parallel routing

CCMPR02729978 Enhancement to snap wires to track with certain mask number

CCMPR02729907 Standard cell rails are clipped near welltap cell power pins and switch cell power pins

CCMPR02729838 Routing DRCs when accessing pins due to using incorrect track

CCMPR02729434 Innovus unplacing the FIXED IO pins

CCMPR02729307 False missing VIA reported when PG wires and block PG pins overlapped

CCMPR02729132 Crash during syn_opt spatial

CCMPR02728696 editPowerVia does not choose the appropriate via type

CCMPR02728461 SEGV during route_opt_design -ideal_clock

CCMPR02728182 Tool is not honoring add_fillers_with_drc - false while doing add_fillers

CCMPR02727899 SEGV by the write_nsw_transition_map_file command

CCMPR02727800 TQuantus SEGV with backside routing in design

CCMPR02727795 Tool is not honoring must_join settings

CCMPR02727710 Detour routing around staggered bus routing when via room available

CCMPR02727241 RouteDesign crash

CCMPR02727147 edit_pin is unable to use backside layers for pin assignment

CCMPR02727141 Pre cts does not fix max transition at best misses gas station in some case

CCMPR02727133 Antenna violation is detected by check_antenna but missed by route_global_detail

CCMPR02727112 route_opt_design ERROR with eDR set to true

CCMPR02727099 Stylus not showing Clone partition of type fence and blackbox

CCMPR02727049 Buffering fail due to power domain crossing

CCMPR02726869 Legalization problem and DIAGS messages in CCOpt

CCMPR02726640 Tool is creating "adjacent_cut_four_cut" DRC while doing add_fillers

CCMPR02726543 Occurred M1 Trim_To_Trim_Spacing violation in particular cell type after NanoRoute

CCMPR02726272 ecoRoute is not fixing M2 EOL DRCs using patch metal/wire

CCMPR02726265 Hang is seen in ccopt_design

CCMPR02726254 Innovus crashed when reading the dbase written out by the same version of the Innovus in the previous session

CCMPR02726126 Missing M6 when change width on different metalPattern

CCMPR02725828 addRepeaterByRule crash

CCMPR02725542 Top/bottom termination cell insertion

CCMPR02725251 route_design -track_opt having ~26 CSHORTS

CCMPR02725236 M0 patch extension from M0 pins that seemed unnecessary

CCMPR02724950 add_fillers fails to fill 1 site gaps

CCMPR02724797 saveDesign causes crash

CCMPR02724501 High runtime for GateDecomposition transform

CCMPR02724217 Tool crash (internal (SEGV) error/signal) in ccopt_design

CCMPR02724179 Metal_Color_Change violations on METAL2

CCMPR02723894 Default option tuning for NSwidth match

CCMPR02723750 Enhancement of missing VIA checking

CCMPR02723647 ERROR (NRDB-2031) LAYER m0 has advanced min area rule but no default min area rule, from route_design

CCMPR02723322 report_metrics crashed

CCMPR02723260 Tool does not honor place_detail_legalization_inst_gap for rectilinear cell cutout edges

CCMPR02722813 Need to add wire declaration for FE_UNCONNECTED nets

CCMPR02722724 opt_design -post_route Metal_Color_Change/Trim_Color DRCs tool swaps RA to GA cell

CCMPR02722129 reinforce_pg command option -rail_analysis_directory does not work

CCMPR02721862 commit_power_intent adding additional ISO cells in Innovus db. As per customer these are not needed

CCMPR02721208 Core dump during the global route step

CCMPR02721031 Very hard to know which clustering problems are runtime problems - follow on

CCMPR02720775 M0 patches are not fully connected to the boundaries of same DCAP cells after routeDesign -passiveFill

CCMPR02720757 Remove write/read_codesign_die_abstract 3DIC license check

CCMPR02720646 Via pillar has MAR violation on it

CCMPR02720157 MixedPlace congestions issue and DRC issue for pin access

CCMPR02719735 Crash during routeDesign -trackOpt

CCMPR02719313 Abnormal/large m0 pin-probe extension creates DRCs

CCMPR02719264 add_well_taps not handling non-macro placement obstructions

CCMPR02718780 IMPESI-3201 error seen in testing

CCMPR02718639 SEGV error during loading DB in Innovus

CCMPR02718538 Worse routing results (more SHORT vios)

CCMPR02718158 The M2 Mar DRC occur as connecting shielding to the M1 power rail

CCMPR02717819 Pre-routed CLK nets with resistance 0 in the clock stage

CCMPR02717401 RnD build unable to route all 96 nets with few bumps being out of order

CCMPR02717336 RC scaling in QRC causing SPEF reading errors in Innovus signoff extraction mode

CCMPR02717044 False pre-route DRC are reported by checkPlace

CCMPR02716656 POD flop clock latency issue when using ECF

CCMPR02716181 Spacing violations between followpin wire and prerouting

CCMPR02715542 M1 pin geometry beyond cell boundary support request

CCMPR02715423 Global variable becoming -nan after ecoRoute

CCMPR02715289 Missing connections on GND power pins after sroute (followpin wires)

CCMPR02715254 optDesign -postRoute issues DIAG messages about markToBeDeleted, coeSubTimingGraph

CCMPR02715207 Reverse 2 metal pattern in FOLLOW statement will not aligned

CCMPR02715118 Tool crash in initial detail routing in special net shape process

CCMPR02715105 add_fillers leaves gaps

CCMPR02715068 set_cell_padding requires Innovus license to execute

CCMPR02715062 check_place not catching NSWidth violations between single and double height cell

CCMPR02714900 The attachIOBuffer does not finish when inserting buffer to a high fanout port

CCMPR02714888 Routing does not fix 44 Minimal_Area violations among total of 1370 violations

CCMPR02714691 Anomalous check_library behavior for regarray cell

CCMPR02714612 flashPG engine did not connect the PD ring to nearby core ring

CCMPR02714585 Crash in the routeopt stage during restore timing graph

CCMPR02714584 flashPG engine creates overlapping staples when step-distance value is shorter than the staple's length

CCMPR02714103 Off grid trim vios

CCMPR02712473 opt_design -post_route taking long runtime

CCMPR02712443 Need to support RX transition filler

CCMPR02711802 ecoAddRepeater -spreadDist option has bugs

CCMPR02711482 routeDesign routes the clock net jogging on lower layers to make the bad latency and timing

CCMPR02710060 DRC violations seen by NanoRouter not matching with the DRCs seen with check_drc

CCMPR02709956 oa_cut_rows cuts not all rows under PADs

CCMPR02709432 merge_hierarchical_def FILL3 CM0 lost issue testcase

CCMPR02709022 Invalid scandef written out by SMART hierarchical flow

CCMPR02708563 saveNetlist -includePowerGround expands a signal bus producing netlist which does not elab

CCMPR02708393 Violation still exist after editPowerVia

CCMPR02708032 route_design -track_opt hangs for more than three days

CCMPR02706618 check_place reports false implant violations where implant layer overlaps with placement blockage

CCMPR02706602 Need hard constraints to force Internal nets' DR not to cross PD

CCMPR02705947 M1 Trim spacing violations over FILL1 cells

CCMPR02705519 ISO cell placed very far from PD boundary

CCMPR02705232 route_pg finishing with huge VIA3 cut DRCs

CCMPR02705210 addFiller adding decaps under macro halo

CCMPR02705209 Violations for m0 Off_Trim_Grid shapes, missed by NR/Verify due to negative grid index

CCMPR02705125 Huge negative net delay after CTS, positive net delay after NR

CCMPR02704796 To adjust PRL calculation for FORBIDDENSPACING rule per new DRM interpretation

CCMPR02704454 EEQ cells cause SKP behavior changed and led to worse PPA in the end of POD

CCMPR02703989 Crash during syn_opt -spatial

CCMPR02703870 Long CTS runtime during MISC section of clock clustering

CCMPR02703743 update_power_vias fails to put in via, previous versions do, VIA is required in these locations

CCMPR02703376 ViaGen not honoring the SAMEVIA spacing, using the normal spacing instead

CCMPR02703163 Violation at boundary should be based on violation marker instead of cut shape

CCMPR02702350 Option for alignment of WellTap and Top/bottom termination cell

CCMPR02701891 Stylus vivid format to enable side by side object like html

CCMPR02701196 TQuantus and signoff Quantus spefs are not matching. The scaling factors are huge

CCMPR02700555 Enhancement for flashPG to allow stripes abutment when it is same net, same width, and same track

CCMPR02700554 Enhancement for flashPG engine to use the CELL's origin as the start offset

CCMPR02699068 add support for setEditMode -keep_via to allow control of VIA deletion when removing wire by deleteSelectFromFplan

CCMPR02698552 editPowerVia does not work for the object outside die area

CCMPR02697781 FIB cell routing creating DRC with macro pins

CCMPR02697716 Huge CCOPT runtime issue

CCMPR02695549 H-tree synthesis fails to meet transition targets

CCMPR02694823 Inverter chain pair after preserve -hierarchical port

CCMPR02693469 Write netlist creates PG ports

CCMPR02692241 CCOpt -cts long run time during source shield net spec and during “Restoring CCOpt stage"

CCMPR02691307 LEQ compatible cells. LEQ-aware commands to capture eligible swap

CCMPR02690876 Sub-optimal M0 routing of libs for M0 pins. Tool should flip inst to align M0 pins and place closer

CCMPR02690466 Incorrect module density in place_opt_design

CCMPR02690110 check_drc had large increase in runtime when layer tech LEF "area" increased

CCMPR02689809 EOLK violation not detected by Innovus

CCMPR02689165 Buffer addition is not happening using the addRepeaterByRule command

CCMPR02687982 Lower MBFF ratio

CCMPR02684145 Innovus is not fixing drv violations at the end of route_opt_design due to the reason gain is not enough

CCMPR02682558 Guide constraint for group:svt/PD_SVT causing overlaps in the design

CCMPR02681749 Issue while creating UFC rule because obj type as power_domains is not applicable

CCMPR02681737 Enhancement to phase assignment on macro block pins and associated tie and terminate cells

CCMPR02681723 Enhancement of incremental mode to phase assignment

CCMPR02675297 Checks failing on few clock and data nets

CCMPR02674379 Need the congRepair step when placing ISO cells near the power domain boundary

CCMPR02668939 verifyEndCap report false alarm

CCMPR02668102 Use wide metal for all transition layers inside via pillars

CCMPR02665549 Adding all custom proc icons in single drop down list

CCMPR02661641 opt_design -post_route -hold -incr met SEGV

CCMPR02659051 Violations seen at o/p of clock buffer pin due to clk route jogs at lower layer

CCMPR02654634 Engine DRC violations are created when running add_reinforce_pg

CCMPR02654488 Innovus TQuantus extraction does not consider RC impact from floating metalFill

CCMPR02654147 Timing jump after updating same viewDefinition.tcl and re-extract RC

CCMPR02654115 flashPG engine needs to recognize the via defined by add_via_definition

CCMPR02653457 Enhancement for LVL/ISO placement during place_opt_design

CCMPR02652375 verify_drc to check full_fill trim rule

CCMPR02652026 route_opt_design crashes

CCMPR02647810 Flop merge should not merge flops at different levels in level-based CTS flows

CCMPR02646977 Need 45deg routing to the pad

CCMPR02643600 V2 VGS violation is not detected by checkPlace

CCMPR02643029 Need to be improved in write_lef_library to include all the vias from generateVias command

CCMPR02639617 Long run time in TNS Opt

CCMPR02638794 Timing degrade in the iSpatial power reclaim stage

CCMPR02628318 NanoRoute Post Route wire spreading creating thousands of CutEol violations

CCMPR02625643 writeFPlanScript does not export soft guides

CCMPR02617120 Observing crash during the addRepeaterByRule command

CCMPR02616596 flashPG enhancement to auto create PG pins when its stripes/followpins edge touch the design boundary

CCMPR02614578 Innovus stops after 2nd Iteration during the place_opt_design step

CCMPR02605225 Incorrect extraction of via pillar

CCMPR02604629 setRouteMode -earlyGlobalUseDoubleCutViaOnly Common UI equivalent

CCMPR02603789 Unbuffered nets are not been optimization even after ETF been applied before POD

CCMPR02597947 Replace diode instances To tap cell instances in the shielding log

CCMPR02589860 opt_clock_skew -post_route removes the existing path groups

CCMPR02578661 Interpolation in power analysis in Innovus

CCMPR02574222 Enhance create_gui_text with new option -orient

CCMPR02495858 Kit update

CCMPR02486269 Crash in verify_connectivity

CCMPR02485318 Question about check_floorplan

CCMPR02471954 get_message -id <IDNAME> -count is busted

CCMPR02258863 NR is not able to connect shield to powerStripe with correct number of cut

CCMPR02159896 ecoSplitFlop not splitting multibit flop

CCMPR02157972 checkDesign reports monotonous information, which increases the file size

CCMPR02100838 Improve on warning message when adding an instance back to the instance group that it is already in

CCMPR01999232 writeFPlanScript does not write out CLASS COVER cells information

CCMPR02763965 routeDesign SEGV

CCMPR02762770 Crash in routing

CCMPR02760206 editAddTrimMetal adds incorrect CM0 trim shape color when inst is mask_shift

CCMPR02759206 The add_stripes command is creating P/G stripes outside the rectilinear core boundary

CCMPR02758807 Objects of type guiPoly cannot be moved

CCMPR02758788 NanoRoute/verify_drc.

CCMPR02757033 Innovus recognizes wrong via group

CCMPR02756955 route_eco -fix_drc causing off Grid Trim Center violations

CCMPR02756628 "editPowerVia" does not consider SMAC(SAMEMETALALIGNEDCUT) violation during inserting post staple via

CCMPR02756289 ecoRoute leaves some CM0 patch wires DRC violations

CCMPR02756282 add_target_pg is removing existing wires and vias which is causing extra opens

CCMPR02755977 Innovus does not report a violation

CCMPR02755424 Column-mode secondary PG causing MaxViaStack violations even with -shape COREWIRE

CCMPR02755334 Column-mode secondary PG missing some vias on upper layers

CCMPR02755322 read_power_intent should support add_supply_state in UPF 3.0

CCMPR02755319 Run time is much longer when using 'set_dc_sources power_switch' in a design without power switches

CCMPR02754962 Observing high runtime for defOut -selected -with_shield -routing

CCMPR02754869 Tool is not able to fix Hold Violation on Q to SI path in design if net connected to different power domain cells

CCMPR02754160 When inserted passive fill, another mask's X3 trim is overlapped on the existing X3 Trim

CCMPR02754017 The check_place command causes instances with place_status unplaced become placed

CCMPR02754013 Fill gap occurs due to not aware edge constraint of rectilinear cell

CCMPR02753251 Create a new process node

CCMPR02753058 passiveFill does not consider obstructs by mask and creates trims on trim blk randomly

CCMPR02752675 Wrong voltage libraries picked for AON cells

CCMPR02752632 NRHF local build does not finish PG routing more than 6 hours for all PG nets 1 shot test

CCMPR02752388 verify_drc reports a false D12 MAR violation

CCMPR02752348 route_opt_design crash at the start of global routing iteration 6

CCMPR02752050 check_macro_place_constraint fails with **ERROR: (IMPTCM-48): narrowChannel is not a legal option for command

CCMPR02750835 Backside clock routing results in SEGV during the NR import stage

CCMPR02750801 ecoRoute memory overshoot during detail route and getting killed

CCMPR02750697 deletePowerSwitch -instanceList is deleting the connections for other PS which are not related to the deleted PS

CCMPR02750490 EndOfLine_Keepout DRCs coming over m1 in Innovus

CCMPR02750487 False report of inst overlap within setup_instance_pin_pitch_access()

CCMPR02750067 Why does the ring pin of IO filler cell connect to bump when it does viewBumpConnection?

CCMPR02749383 SE to SE end of line spacing violation using native tool command

CCMPR02748704 editPowerVia -add_vias created overlapping vias between M15 and AP

CCMPR02748454 Hang/Unable to complete adding pre staple V1 via between M1 and M2 power rails

CCMPR02748011 Random power improvements with minor change in netlists

CCMPR02747933 Tool flags "Wire width on non-uniform track" violation on port with wide width on NDR Track

CCMPR02747821 DIAG during place_opt_design step

CCMPR02747777 The X1 trim violation not fixed by "ecoRoute -fix_filler_drc_with_patch_only" after insertion filler

CCMPR02747589 add_target_pg used for secondary PG routing not handling maxViaStack rule correctly

CCMPR02747580 check_place flagging false Diff Core Edge Length violation

CCMPR02747559 Make Adaptive Density Function (V2) default

CCMPR02747466 Tool is exiting during the saveNetlist command

CCMPR02747456 Run crashing during the post route opt step

CCMPR02747255 Global placement crash with 32 local CPU

CCMPR02747175 Multibit combo merging/split SEGV

CCMPR02746954 ecoRoute -fix_filler_drc_with_patch_only cannot fix M1 violation on DCAP cells

CCMPR02746935 Add an exp option to have area crr honor power

CCMPR02746796 identify_physical_power_domains fails when extra_supply is an empty list

CCMPR02746537 IO pin display not visible issue

CCMPR02746417 Innovus tQRC extraction SEGV with backside metal extraction at set_used_viamap_vias

CCMPR02745926 streamOut is consuming 5X runtime

CCMPR02745730 Trim layer GUI support request

CCMPR02745709 Passivefill support request

CCMPR02745706 Innovus commit_partition not creating physical ports for special nets during pushdown

CCMPR02745654 Crash at the CTS stage

CCMPR02745613 -flatten_bus flag causes write_netlist -include_pg to use 1'b0 instead of vss

CCMPR02745383 place_design -noPrePlaceOpt ERROR (IMPSP-190) with FP mode after checkPlace

CCMPR02745280 M2 off_trim_grid from NR and not Verify

CCMPR02745056 routeDesign crash during data preparation

CCMPR02744892 Crash during ecoRoute -fix_drc

CCMPR02744744 assembleDesign not transforming trim shapes in the block

CCMPR02744646 place_opt_design crashes when via pillars are assigned

CCMPR02744159 Filler gap violation: add_fillers left the filler gap and trigger implant/pre-route violations

CCMPR02744137 Unable to create PG stripe over partition pins

CCMPR02743893 Router creating shorts when large inverter requires via pillars on input and output

CCMPR02743615 optDesign -postCTS hang in 21.15 & 22.30

CCMPR02743466 Make eDR default

CCMPR02743352 DRCs when routing next to cell with M3 pins because router used wrong tracks

CCMPR02742938 addFiller adding huge number of fillers when there are no vertical max stack violations

CCMPR02742746 Routing short with Innovus

CCMPR02742665 Non-fatal error during TQuantus extraction inside Innovus

CCMPR02742645 Routing creating short with routing blockage

CCMPR02742392 deleteRoutingHalo complains error IMPSYC-2210 and fails

CCMPR02742123 M0 Stub routing has longer M0 routes

CCMPR02741898 Need fcroute to route 45deg with short distant

CCMPR02741880 SEGV during routeopt

CCMPR02741832 write_lef_abstract freezes or too slow on bump design

CCMPR02741563 There are a lot of messages about DIAG when refinePlace

CCMPR02741400 Tied Net has Multiple fingers connected by same layer jogging causes Directional Span Length Spacing

CCMPR02741041 False enclosure DRC violation issue

CCMPR02740987 addPowerSwitch crash

CCMPR02740954 endcap tap swap fails if power switches inserted before well tap

CCMPR02740891 Diff Layer Cut Spacing (VIA5 to VIA6 spacing DRCs)

CCMPR02740889 Stack trace error in the postCTS stage

CCMPR02740744 route_design creating EndOfLine Keepout DRC violations

CCMPR02740567 Timer update during PBA ecoRoute

CCMPR02740529 M2 Shorts caused

CCMPR02740456 [SEGV when querying macro after populating data structures

CCMPR02739904 Crash during the finish stage

CCMPR02739859 iSpatial left unloaded buffers after MB merging

CCMPR02739804 Observing crash during the addEndCap command

CCMPR02739292 Crash during VSS power hookup insertion

CCMPR02738788 Hang issue on global routing with shielding done on clock spine net

CCMPR02738051 Innovus crashes at the Place stage

CCMPR02738033 Wrong operation of editPowerVia according to number of CPU count

CCMPR02738007 ViewBumpConnection is not working properly

CCMPR02737980 Remove existing vias when DRC occurs between vias during editAddRoute

CCMPR02737932 Tool hangs after first iteration of optDesign and ecoRoute call in routeOpt

CCMPR02737875 add_target_pg false WARN: M3 spacing(0.060000) is less than the minimum parallel spacing(0.087000) on layer M3

CCMPR02737846 dbNetExtrRCSummary reporting resistance 0 after clock

CCMPR02737302 False IMPSP-376 alarm

CCMPR02737252 Remove assign is adding buffers in wrong domain causing **ERROR: (IMPCCOPT-1044)

CCMPR02736985 place_opt_design crashes during global placement

CCMPR02736702 POD is crashing with power effort set to none

CCMPR02736520 add_target_pg is missing via when choosing incorrect track for connection

CCMPR02736501 MaxViaStack violations on Clock Shield nets

CCMPR02736114 add_target_pg used for secPG routing needs user option to choose shape type for added wires and vias

CCMPR02735984 route_pg causes IMPDF-1064 error

CCMPR02735494 Reduce the runtime of "ecoRoute -fix_filler_drc_with_patch_only"

CCMPR02735334 verify_drc does not mark violations

CCMPR02735331 Flag false MAXVIASTACK violations

CCMPR02735320 place_opt_design not able to reorder scan chain with back2back ordered section

CCMPR02735154 D10 Metal shorts in PG with the addStripe command

CCMPR02735028 refinePlace flag False Pin Access violations

CCMPR02734326 Innovus crashes at the check_library command

CCMPR02733563 SEGV during routeOpt

CCMPR02733404 NDR bottom-preferred layer demotion causing Timing Degradation

CCMPR02733313 Make floorplan "isCore2Io" WRITE-able

CCMPR02733311 SEGV when running the write_physical_context_data command when macros involved

CCMPR02733302 Secondary PG is failing to connect some tap cell pins

CCMPR02733050 addRepeaterByRule adding back to back buffers

CCMPR02732586 **ERROR: Failed to re-stitch scan chain, *** BAD SCAN ASSIGNMENT ***

CCMPR02732546 Crash in editChangeVia -selected

CCMPR02732539 Pin placements are getting dropped after the partition command

CCMPR02731965 Presence of pre-placed cells leaves untapped areas

CCMPR02731841 verifyProcessAntenna crashes

CCMPR02731839 Unexpected Incompatible Resizing done" in routeOpt

CCMPR02731820 Excessive runtime in CommonAndConstantInputSimplification transform in areaOpt

CCMPR02731799 1CPP gap is required if RX transition between cells is more than 10nm

CCMPR02731639 Total Power degradation when enabling Power Density Map

CCMPR02731437 Tool is not able to fix hold violation

CCMPR02731198 Isolation cells moved to opposite end of block from run-to-run

CCMPR02731129 Seeing DRCs after via pillar implementation

CCMPR02730743 Custom Box/gui_shape cannot be resized

CCMPR02730510 Crash during route_design

CCMPR02730480 Innovus crashes in route_pg

CCMPR02730394 FlashPG crash with VARIABLE numerical expression

CCMPR02730349 NRHF side shielding got SEGV with parallel routing

CCMPR02729978 Enhancement to snap wires to track with certain mask number

CCMPR02729907 Standard cell rails are clipped near welltap cell power pins and switch cell power pins

CCMPR02729838 Routing DRCs when accessing pins due to using incorrect track

CCMPR02729434 Innovus unplacing the FIXED IO pins

CCMPR02729307 False missing VIA reported when PG wires and block PG pins overlapped

CCMPR02729132 Crash during syn_opt spatial

CCMPR02728696 editPowerVia does not choose the appropriate via type

CCMPR02728461 SEGV during route_opt_design -ideal_clock

CCMPR02728182 Tool is not honoring add_fillers_with_drc - false while doing add_fillers

CCMPR02727899 SEGV by the write_nsw_transition_map_file command

CCMPR02727800 TQuantus SEGV with backside routing in design

CCMPR02727795 Tool is not honoring must_join settings

CCMPR02727710 Detour routing around staggered bus routing when via room available

CCMPR02727241 RouteDesign crash

CCMPR02727147 edit_pin is unable to use backside layers for pin assignment

CCMPR02727141 Pre cts does not fix max transition at best misses gas station in some case

CCMPR02727133 Antenna violation is detected by check_antenna but missed by route_global_detail

CCMPR02727112 route_opt_design ERROR with eDR set to true

CCMPR02727099 Stylus not showing Clone partition of type fence and blackbox

CCMPR02727049 Buffering fail due to power domain crossing

CCMPR02726869 Legalization problem and DIAGS messages in CCOpt

CCMPR02726640 Tool is creating "adjacent_cut_four_cut" DRC while doing add_fillers

CCMPR02726543 Occurred M1 Trim_To_Trim_Spacing violation in particular cell type after NanoRoute

CCMPR02726272 ecoRoute is not fixing M2 EOL DRCs using patch metal/wire

CCMPR02726265 Hang is seen in ccopt_design

CCMPR02726254 Innovus crashed when reading the dbase written out by the same version of the Innovus in the previous session

CCMPR02726126 Missing M6 when change width on different metalPattern

CCMPR02725828 addRepeaterByRule crash

CCMPR02725542 Top/bottom termination cell insertion

CCMPR02725251 route_design -track_opt having ~26 CSHORTS

CCMPR02725236 M0 patch extension from M0 pins that seemed unnecessary

CCMPR02724950 add_fillers fails to fill 1 site gaps

CCMPR02724797 saveDesign causes crash

CCMPR02724501 High runtime for GateDecomposition transform

CCMPR02724217 Tool crash (internal (SEGV) error/signal) in ccopt_design

CCMPR02724179 Metal_Color_Change violations on METAL2

CCMPR02723894 Default option tuning for NSwidth match

CCMPR02723750 Enhancement of missing VIA checking

CCMPR02723647 ERROR (NRDB-2031) LAYER m0 has advanced min area rule but no default min area rule, from route_design

CCMPR02723322 report_metrics crashed

CCMPR02723260 Tool does not honor place_detail_legalization_inst_gap for rectilinear cell cutout edges

CCMPR02722813 Need to add wire declaration for FE_UNCONNECTED nets

CCMPR02722724 opt_design -post_route Metal_Color_Change/Trim_Color DRCs tool swaps RA to GA cell

CCMPR02722129 reinforce_pg command option -rail_analysis_directory does not work

CCMPR02721862 commit_power_intent adding additional ISO cells in Innovus db. As per customer these are not needed

CCMPR02721208 Core dump during the global route step

CCMPR02721031 Very hard to know which clustering problems are runtime problems - follow on

CCMPR02720775 M0 patches are not fully connected to the boundaries of same DCAP cells after routeDesign -passiveFill

CCMPR02720757 Remove write/read_codesign_die_abstract 3DIC license check

CCMPR02720646 Via pillar has MAR violation on it

CCMPR02720157 MixedPlace congestions issue and DRC issue for pin access

CCMPR02719735 Crash during routeDesign -trackOpt

CCMPR02719313 Abnormal/large m0 pin-probe extension creates DRCs

CCMPR02719264 add_well_taps not handling non-macro placement obstructions

CCMPR02718780 IMPESI-3201 error seen in testing

CCMPR02718639 SEGV error during loading DB in Innovus

CCMPR02718538 Worse routing results (more SHORT vios)

CCMPR02718158 The M2 Mar DRC occur as connecting shielding to the M1 power rail

CCMPR02717819 Pre-routed CLK nets with resistance 0 in the clock stage

CCMPR02717401 RnD build unable to route all 96 nets with few bumps being out of order

CCMPR02717336 RC scaling in QRC causing SPEF reading errors in Innovus signoff extraction mode

CCMPR02717044 False pre-route DRC are reported by checkPlace

CCMPR02716656 POD flop clock latency issue when using ECF

CCMPR02716181 Spacing violations between followpin wire and prerouting

CCMPR02715542 M1 pin geometry beyond cell boundary support request

CCMPR02715423 Global variable becoming -nan after ecoRoute

CCMPR02715289 Missing connections on GND power pins after sroute (followpin wires)

CCMPR02715254 optDesign -postRoute issues DIAG messages about markToBeDeleted, coeSubTimingGraph

CCMPR02715207 Reverse 2 metal pattern in FOLLOW statement will not aligned

CCMPR02715118 Tool crash in initial detail routing in special net shape process

CCMPR02715105 add_fillers leaves gaps

CCMPR02715068 set_cell_padding requires Innovus license to execute

CCMPR02715062 check_place not catching NSWidth violations between single and double height cell

CCMPR02714900 The attachIOBuffer does not finish when inserting buffer to a high fanout port

CCMPR02714888 Routing does not fix 44 Minimal_Area violations among total of 1370 violations

CCMPR02714691 Anomalous check_library behavior for regarray cell

CCMPR02714612 flashPG engine did not connect the PD ring to nearby core ring

CCMPR02714585 Crash in the routeopt stage during restore timing graph

CCMPR02714584 flashPG engine creates overlapping staples when step-distance value is shorter than the staple's length

CCMPR02714103 Off grid trim vios

CCMPR02712473 opt_design -post_route taking long runtime

CCMPR02712443 Need to support RX transition filler

CCMPR02711802 ecoAddRepeater -spreadDist option has bugs

CCMPR02711482 routeDesign routes the clock net jogging on lower layers to make the bad latency and timing

CCMPR02710060 DRC violations seen by NanoRouter not matching with the DRCs seen with check_drc

CCMPR02709956 oa_cut_rows cuts not all rows under PADs

CCMPR02709432 merge_hierarchical_def FILL3 CM0 lost issue testcase

CCMPR02709022 Invalid scandef written out by SMART hierarchical flow

CCMPR02708563 saveNetlist -includePowerGround expands a signal bus producing netlist which does not elab

CCMPR02708393 Violation still exist after editPowerVia

CCMPR02708032 route_design -track_opt hangs for more than three days

CCMPR02706618 check_place reports false implant violations where implant layer overlaps with placement blockage

CCMPR02706602 Need hard constraints to force Internal nets' DR not to cross PD

CCMPR02705947 M1 Trim spacing violations over FILL1 cells

CCMPR02705519 ISO cell placed very far from PD boundary

CCMPR02705232 route_pg finishing with huge VIA3 cut DRCs

CCMPR02705210 addFiller adding decaps under macro halo

CCMPR02705209 Violations for m0 Off_Trim_Grid shapes, missed by NR/Verify due to negative grid index

CCMPR02705125 Huge negative net delay after CTS, positive net delay after NR

CCMPR02704796 To adjust PRL calculation for FORBIDDENSPACING rule per new DRM interpretation

CCMPR02704454 EEQ cells cause SKP behavior changed and led to worse PPA in the end of POD

CCMPR02703989 Crash during syn_opt -spatial

CCMPR02703870 Long CTS runtime during MISC section of clock clustering

CCMPR02703743 update_power_vias fails to put in via, previous versions do, VIA is required in these locations

CCMPR02703376 ViaGen not honoring the SAMEVIA spacing, using the normal spacing instead

CCMPR02703163 Violation at boundary should be based on violation marker instead of cut shape

CCMPR02702350 Option for alignment of WellTap and Top/bottom termination cell

CCMPR02701891 Stylus vivid format to enable side by side object like html

CCMPR02701196 TQuantus and signoff Quantus spefs are not matching. The scaling factors are huge

CCMPR02700555 Enhancement for flashPG to allow stripes abutment when it is same net, same width, and same track

CCMPR02700554 Enhancement for flashPG engine to use the CELL's origin as the start offset

CCMPR02699068 add support for setEditMode -keep_via to allow control of VIA deletion when removing wire by deleteSelectFromFplan

CCMPR02698552 editPowerVia does not work for the object outside die area

CCMPR02697781 FIB cell routing creating DRC with macro pins

CCMPR02697716 Huge CCOPT runtime issue

CCMPR02695549 H-tree synthesis fails to meet transition targets

CCMPR02694823 Inverter chain pair after preserve -hierarchical port

CCMPR02693469 Write netlist creates PG ports

CCMPR02692241 CCOpt -cts long run time during source shield net spec and during “Restoring CCOpt stage"

CCMPR02691307 LEQ compatible cells. LEQ-aware commands to capture eligible swap

CCMPR02690876 Sub-optimal M0 routing of libs for M0 pins. Tool should flip inst to align M0 pins and place closer

CCMPR02690466 Incorrect module density in place_opt_design

CCMPR02690110 check_drc had large increase in runtime when layer tech LEF "area" increased

CCMPR02689809 EOLK violation not detected by Innovus

CCMPR02689165 Buffer addition is not happening using the addRepeaterByRule command

CCMPR02687982 Lower MBFF ratio

CCMPR02684145 Innovus is not fixing drv violations at the end of route_opt_design due to the reason gain is not enough

CCMPR02682558 Guide constraint for group:svt/PD_SVT causing overlaps in the design

CCMPR02681749 Issue while creating UFC rule because obj type as power_domains is not applicable

CCMPR02681737 Enhancement to phase assignment on macro block pins and associated tie and terminate cells

CCMPR02681723 Enhancement of incremental mode to phase assignment

CCMPR02675297 Checks failing on few clock and data nets

CCMPR02674379 Need the congRepair step when placing ISO cells near the power domain boundary

CCMPR02668939 verifyEndCap report false alarm

CCMPR02668102 Use wide metal for all transition layers inside via pillars

CCMPR02665549 Adding all custom proc icons in single drop down list

CCMPR02661641 opt_design -post_route -hold -incr met SEGV

CCMPR02659051 Violations seen at o/p of clock buffer pin due to clk route jogs at lower layer

CCMPR02654634 Engine DRC violations are created when running add_reinforce_pg

CCMPR02654488 Innovus TQuantus extraction does not consider RC impact from floating metalFill

CCMPR02654147 Timing jump after updating same viewDefinition.tcl and re-extract RC

CCMPR02654115 flashPG engine needs to recognize the via defined by add_via_definition

CCMPR02653457 Enhancement for LVL/ISO placement during place_opt_design

CCMPR02652375 verify_drc to check full_fill trim rule

CCMPR02652026 route_opt_design crashes

CCMPR02647810 Flop merge should not merge flops at different levels in level-based CTS flows

CCMPR02646977 Need 45deg routing to the pad

CCMPR02643600 V2 VGS violation is not detected by checkPlace

CCMPR02643029 Need to be improved in write_lef_library to include all the vias from generateVias command

CCMPR02639617 Long run time in TNS Opt

CCMPR02638794 Timing degrade in the iSpatial power reclaim stage

CCMPR02628318 NanoRoute Post Route wire spreading creating thousands of CutEol violations

CCMPR02625643 writeFPlanScript does not export soft guides

CCMPR02617120 Observing crash during the addRepeaterByRule command

CCMPR02616596 flashPG enhancement to auto create PG pins when its stripes/followpins edge touch the design boundary

CCMPR02614578 Innovus stops after 2nd Iteration during the place_opt_design step

CCMPR02605225 Incorrect extraction of via pillar

CCMPR02604629 setRouteMode -earlyGlobalUseDoubleCutViaOnly Common UI equivalent

CCMPR02603789 Unbuffered nets are not been optimization even after ETF been applied before POD

CCMPR02597947 Replace diode instances To tap cell instances in the shielding log

CCMPR02589860 opt_clock_skew -post_route removes the existing path groups

CCMPR02578661 Interpolation in power analysis in Innovus

CCMPR02574222 Enhance create_gui_text with new option -orient

CCMPR02495858 Kit update

CCMPR02486269 Crash in verify_connectivity

CCMPR02485318 Question about check_floorplan

CCMPR02471954 get_message -id <IDNAME> -count is busted

CCMPR02258863 NR is not able to connect shield to powerStripe with correct number of cut

CCMPR02159896 ecoSplitFlop not splitting multibit flop

CCMPR02157972 checkDesign reports monotonous information, which increases the file size

CCMPR02100838 Improve on warning message when adding an instance back to the instance group that it is already in

CCMPR01999232 writeFPlanScript does not write out CLASS COVER cells information

The Innovus Implementation System is a massively parallel physical implementation system that enables engineers to deliver high-quality designs with competitive power, performance and area (PPA) targets while accelerating time to market. It is a part of the Cadence digital design platform that supports the company’s overall System Design Enablement strategy, which enables system and semiconductor companies to create complete, differentiated end products more efficiently.

Place and Route in Cadence Innovus

Complete flow of innovus tool has been demonstrated in this video. Both command line and GUI mode have been covered in the same video. Important input files for this flow has also been discussed and how to create them has been explained.

Cadence is a pivotal leader in electronic systems design, building upon more than 30 years of computational software expertise. The company applies its underlying Intelligent System Design strategy to deliver software, hardware and IP that turn design concepts into reality. Cadence customers are the world’s most innovative companies, delivering extraordinary electronic products from chips to boards to complete systems for the most dynamic market applications, including hyperscale computing, 5G communications, automotive, mobile, aerospace, consumer, industrial and healthcare. For nine years in a row, Fortune magazine has named Cadence one of the 100 Best Companies to Work For.

Owner: Cadence Design Systems, Inc.

Product Name: INNOVUS Implementation System

Version: 21.17.000-ISR7 *

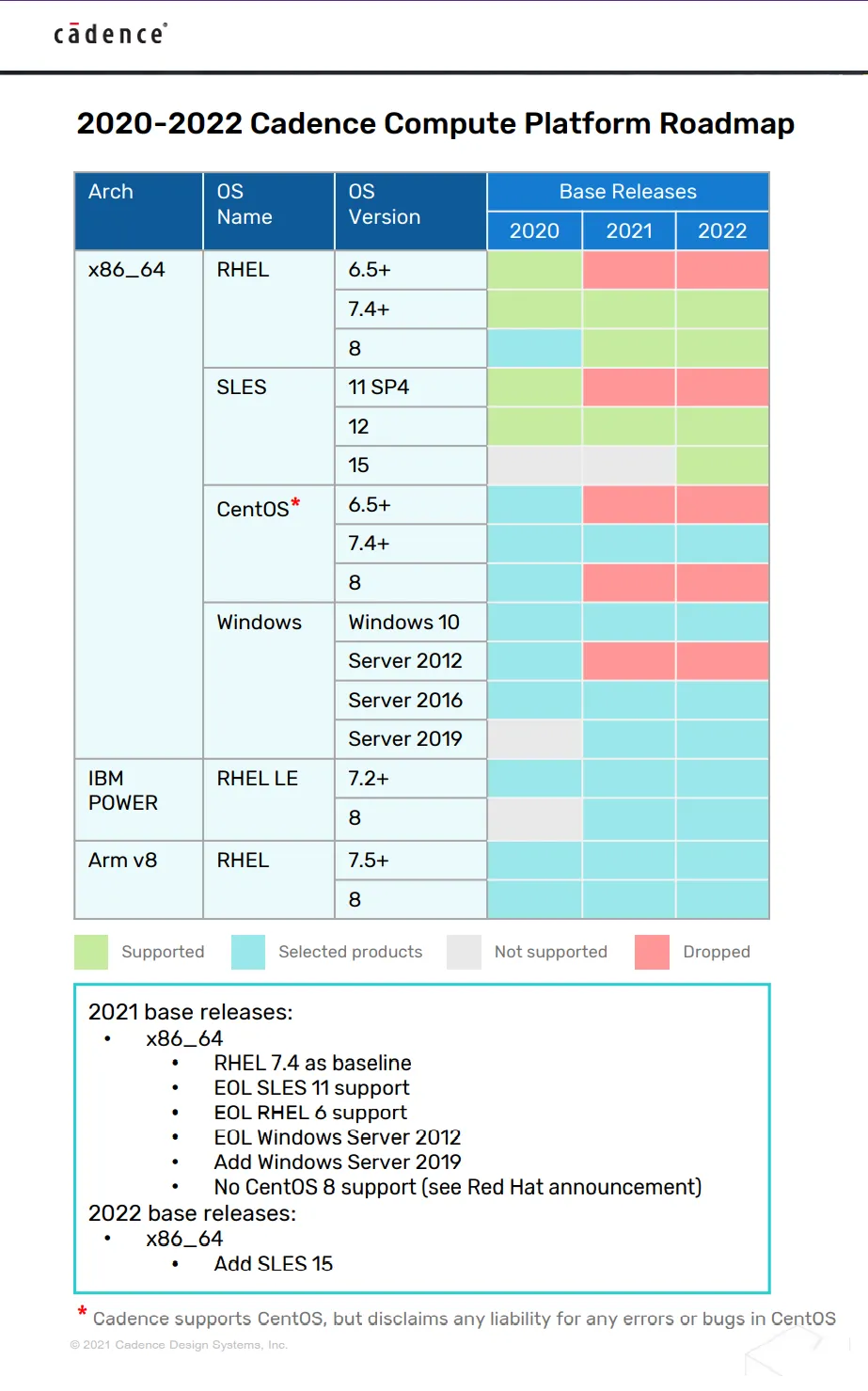

Supported Platform: lnx86

Website Home Page : ww.cadence.com

Languages Supported: english

System Requirements: Linux **

Size: 61.0 Gb

Base_INNOVUS21.10.000_lnx86

Hotfix_INNOVUS21.11.000-ISR1_lnx86

Hotfix_INNOVUS21.12.000-ISR2_lnx86

Hotfix_INNOVUS21.13.000-ISR3_lnx86

Hotfix_INNOVUS21.14.000-ISR4_lnx86

Hotfix_INNOVUS21.15.000-ISR5_lnx86

Hotfix_INNOVUS21.16.000-ISR6_lnx86

Hotfix_INNOVUS21.17.000-ISR7_lnx86

Hotfix_INNOVUS21.11.000-ISR1_lnx86

Hotfix_INNOVUS21.12.000-ISR2_lnx86

Hotfix_INNOVUS21.13.000-ISR3_lnx86

Hotfix_INNOVUS21.14.000-ISR4_lnx86

Hotfix_INNOVUS21.15.000-ISR5_lnx86

Hotfix_INNOVUS21.16.000-ISR6_lnx86

Hotfix_INNOVUS21.17.000-ISR7_lnx86

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please