Cadence PCB Allegro and OrCAD 2022 HF2 (22.10.002) | 3.5 Gb

Cadence Design Systems, Inc. , the leader in global electronic design innovation, is pleased to announce the availability of Cadence PCB Allegro and OrCAD 2022 HF2 (22.10.002) families of products aimed at boosting performance and productivity through improvements features and big fixed issues.

=============================================================================

CCRID Product ProductLevel2 Title

=====================================================================

2299554 ALLEGRO_EDITOR 3D_CANVAS Error message on starting 3D Canvas and after bending all objects regarding object outside design

2744798 ALLEGRO_EDITOR ARTWORK Popup menu issue in Japanese environment of OrCAD PCB Editor 17.4.

2713038 ALLEGRO_EDITOR DATABASE Updating components and padstacks and changing layers take longer for database with around 100,000 padstacks

2743228 ALLEGRO_EDITOR DATABASE adw_uprev is crashing on all JEDEC models

2727858 ALLEGRO_EDITOR DFA Unable to enter 0 for toe, heel, side constraint in component lead spreadsheet of DFA constraints BFH

2715275 ALLEGRO_EDITOR DRC_CONSTR DRC behavior not same between Constraint Manager and DRC flag

2741815 ALLEGRO_EDITOR DRC_CONSTR DRC Browser: Filter by Area shows performance issues when enabling the option.

2734765 ALLEGRO_EDITOR DXF NcDrill figures for pins with no pad defined are not exported to DXF.

2744585 ALLEGRO_EDITOR GRAPHICS Splitting via stack within delete command does not correct labeling

2670119 ALLEGRO_EDITOR IN_DESIGN_ANA Aurora IR Drop Results: Switch between multiple results

2694821 ALLEGRO_EDITOR IN_DESIGN_ANA Aurora IR Drop provide view mode for via current

2729786 ALLEGRO_EDITOR IN_DESIGN_ANA Aurora IR drop vertical range should persist when layer is changed

2752652 ALLEGRO_EDITOR IN_DESIGN_ANA IR vision custom range, then disable the custom range, the custom range persists, no way to reset

2752655 ALLEGRO_EDITOR IN_DESIGN_ANA Aurora IR drop via current distribution scale doesn't match with table

2763639 ALLEGRO_EDITOR IN_DESIGN_ANA Allegro crashes when attempting to load irda with nonideal ground results

2742997 ALLEGRO_EDITOR MULTI_USER Allegro Symphony muserver.exe was unable to run due to undefined system environment variables.

2649616 ALLEGRO_EDITOR PLACEMENT Place Replicate Module's layer map form doesn't fit on screen when db has a lot of layers

2361613 APD ASSY_RULE_CHE The checking function of Solder Mask to Filled Via Drill spacing is failed.

2725794 APD ASSY_RULE_CHE ADRC violations not reported correctly unless Layer is made visible

2729610 APD ASSY_RULE_CHE Via to package edge spacing not working correctly (assembly rule checker)

2736438 APD DEGASSING stream out degassing holes

2742652 APD EDIT_ETCH APD Plus crashes when adding vias

2675887 APD INTERACTIVE Request for attribute to prevent objects from being copied

2625040 APD LOGIC Skill API requested for Logic - Push Connectivity

2730353 APD LOGIC Ability to customized NetNames

2730346 APD OTHER Daisy Chain tool: Ability to choose layer and feature where we want it to be routed

2742530 APD OTHER Include via structures during DC routing

2723122 APD SHAPE unable to add teardrop at t-junction

2730098 CONCEPT_HDL CORE Canceling the Physical Part Filter window closes all open windows and crashes the application

2601230 CONSTRAINT_MGR OTHER Missing Net Class column in the Spacing Constraint Matrix html Report

2743900 CONSTRAINT_MGR SYSCAP Detect corruption due to illegal constraints on a deisgn object

2715038 CONSTRAINT_MGR UI_FORMS When generating ECSet audit report, part of the generating difference report window gets left back on the screen

2728668 GRE GLOBAL Allegro 17.4 and 22.1 crash while trying to run Flowplan/Plan/Plan/topological

2726583 ORBITIO BUMP_FLOORPLA create_bump: '-offset' option cannot work well in bump pitch constraint

2732209 ORBITIO DATABASE Anchor Device: master device should not be moved by slave device

2728788 ORBITIO DIEABSTRACT DieAbstract: add feature as optional item to show the change log about die abstract merging progress

2732200 ORBITIO GUI GUI: unassign anchor device

2735692 ORBITIO GUI OIO: Reopening the IO Info Table during the same session return to the default size.

2737150 ORBITIO GUI MSFT :: Hatteras :: Selection Filter :: reset option dont work

2738543 ORBITIO GUI System Planner GUI enhancement: dim background

2736709 ORBITIO INNOVUS_IF [Modularization flow - Abstract Lef] Partition Blocks need to output abstract LEF by planner::create_module_model

2732883 ORBITIO INTEGRITY_IF 23.10: write_def cannot export [VIAS] section

2726193 ORBITIO IO_FLOORPLAN [Modulization Flow - Flatten] - Ungroup command will remove the objects in other devices use same Device Template

2730222 ORBITIO IO_FLOORPLAN pin <None> for no pin LEF was exported to verilog.

2726403 ORBITIO OTHER IO Info Import: Warning message when PADCellPinName is empty but LEF Macro has a pin.

2739486 ORBITIO SELECTION [Intel] select_obj selected unexpected object

2724613 ORBITIO TCL create_bump: rename the option '-pin_proximity' to '-pin_group_pitch'

2728829 ORBITIO TCL Tcl: need command 'create_partition' for selected objects

2728840 ORBITIO TCL Tcl: need command 'flatten_partition' for selected objects

2728370 ORBITIO VOLTUS_IF Integrity ERA flows : Expose vsrc_search_distance option to run_era

2734468 PCB_LIBRARIAN SETUP Lock settings in library SITE.CPM prevent changes to unrelated settings in PDV Setup.

2267067 PCB_LIBRARIAN SYMBOL_EDITOR Can not see and select the dot in NSE for some symbols created in old PDV (DEHDL)

2626457 PCB_LIBRARIAN SYMBOL_EDITOR Symbol graphics are not visible while placing the part in SC

2706959 PCB_LIBRARIAN SYMBOL_EDITOR Need a better way to handle initSymEd.tcl file in Site config.

2717524 PSPICE LIBRARIES IRF640 model is not simulated in release 17.4-2019

2668949 PSPICE SIMMODELS Inverting behavior of IBIS model not honored by translated IBIS model

2729172 PSPICE SIMULATOR Inconsistent display of license check-out time in .out file

2114232 PSPICE SLPS Co-simulation profile gives S-function error because .stl file is not copied from PSpice profile

2723553 PSPICE SLPS PSpice MATLAB co-simulation gives error: Error reported by S-function 'PSpice'

2745640 PULSE R2PLM-3DX PLM - 3DX connection, when I have generated my documents and want to check the Result it's not possible.

2107415 SIP_LAYOUT INTERACTIVE This design has pads defined to be only on the Top layer, (SMT) but are showing pads on other layers.

2713889 SYSTEM_CAPTURE ALIGN_DISTRIB Left align or right align functionality in System Capture does not align net names correctly.

2739765 SYSTEM_CAPTURE ASSIGN_SIGNAL System Capture using 97% System memory and crashing computer when updating design.

2729214 SYSTEM_CAPTURE CAPTURE_IMPOR Members of component with multiple symbols missing swap_info property

2737537 SYSTEM_CAPTURE CONSTRAINT_MA system capture: adding parts in a replicated block (103 times) hangs

2719769 SYSTEM_CAPTURE CUSTOM_TEXT Text boxes: Text formatting and location is inconsistent between users

2743224 SYSTEM_CAPTURE DRC Inconsistency in highlight option in the schematic audit report

2762465 SYSTEM_CAPTURE DRC Selecting Schematic Audit Violations don't allow for navigating to the respective violating circuit/component.

2736840 SYSTEM_CAPTURE IMPORT_BLOCK Migration from DE-HDL fails due to trailing spaces in signal and bus names

2744539 SYSTEM_CAPTURE IMPORT_DEHDL_ Issues during HDL Import

2726221 SYSTEM_CAPTURE INTERNATIONAL Garbled characters in Violation tab if CDS_CP_TRANSLATION_LANGUAGE

2690171 SYSTEM_CAPTURE MENUS_AND_TOO Allow user control on order of custom menu items in System Capture

2686723 SYSTEM_CAPTURE MISCELLANEOUS Need Tcl API to unmerge all table cells

2649751 SYSTEM_CAPTURE NAVIGATION System Capture navigation view merges nets at system level

2597225 SYSTEM_CAPTURE PART_MANAGER Variant Part info is not updated with the CIS Database is modified

2741947 SYSTEM_CAPTURE PRINT Version Control PDF's are visually small and must be manually made larger repeatedly.

2745388 SYSTEM_CAPTURE RENAME System Capture crash on signal rename when connecting to part

2745579 SYSTEM_CAPTURE RENAME System Capture crashes when renaming net

2674182 SYSTEM_CAPTURE REPLACE Break in bus connections after ctap symbol update in reference library.

2713261 SYSTEM_CAPTURE REPLACE Page Border with Japanese notes cannot be edited in the System Capture environment

2720379 SYSTEM_CAPTURE SYMBOL_GEN Symbol block generation for large number of pins goes outside of page border and makes symbol almost impossible to edit.

2738449 SYSTEM_CAPTURE TABLE_OF_CONT system capture TOC (Table Of Content) customization required to define page name / instance name of replicated block

2738522 SYSTEM_CAPTURE UI Cursor jumps to end of the word while renaming NetGroups or NetGroup Members

2636015 SYSTEM_DESIGN SDE_NAVIGATIO SLD - Allow the ability to define a PACK_IGNORE attribute to system block

CCRID Product ProductLevel2 Title

=====================================================================

2299554 ALLEGRO_EDITOR 3D_CANVAS Error message on starting 3D Canvas and after bending all objects regarding object outside design

2744798 ALLEGRO_EDITOR ARTWORK Popup menu issue in Japanese environment of OrCAD PCB Editor 17.4.

2713038 ALLEGRO_EDITOR DATABASE Updating components and padstacks and changing layers take longer for database with around 100,000 padstacks

2743228 ALLEGRO_EDITOR DATABASE adw_uprev is crashing on all JEDEC models

2727858 ALLEGRO_EDITOR DFA Unable to enter 0 for toe, heel, side constraint in component lead spreadsheet of DFA constraints BFH

2715275 ALLEGRO_EDITOR DRC_CONSTR DRC behavior not same between Constraint Manager and DRC flag

2741815 ALLEGRO_EDITOR DRC_CONSTR DRC Browser: Filter by Area shows performance issues when enabling the option.

2734765 ALLEGRO_EDITOR DXF NcDrill figures for pins with no pad defined are not exported to DXF.

2744585 ALLEGRO_EDITOR GRAPHICS Splitting via stack within delete command does not correct labeling

2670119 ALLEGRO_EDITOR IN_DESIGN_ANA Aurora IR Drop Results: Switch between multiple results

2694821 ALLEGRO_EDITOR IN_DESIGN_ANA Aurora IR Drop provide view mode for via current

2729786 ALLEGRO_EDITOR IN_DESIGN_ANA Aurora IR drop vertical range should persist when layer is changed

2752652 ALLEGRO_EDITOR IN_DESIGN_ANA IR vision custom range, then disable the custom range, the custom range persists, no way to reset

2752655 ALLEGRO_EDITOR IN_DESIGN_ANA Aurora IR drop via current distribution scale doesn't match with table

2763639 ALLEGRO_EDITOR IN_DESIGN_ANA Allegro crashes when attempting to load irda with nonideal ground results

2742997 ALLEGRO_EDITOR MULTI_USER Allegro Symphony muserver.exe was unable to run due to undefined system environment variables.

2649616 ALLEGRO_EDITOR PLACEMENT Place Replicate Module's layer map form doesn't fit on screen when db has a lot of layers

2361613 APD ASSY_RULE_CHE The checking function of Solder Mask to Filled Via Drill spacing is failed.

2725794 APD ASSY_RULE_CHE ADRC violations not reported correctly unless Layer is made visible

2729610 APD ASSY_RULE_CHE Via to package edge spacing not working correctly (assembly rule checker)

2736438 APD DEGASSING stream out degassing holes

2742652 APD EDIT_ETCH APD Plus crashes when adding vias

2675887 APD INTERACTIVE Request for attribute to prevent objects from being copied

2625040 APD LOGIC Skill API requested for Logic - Push Connectivity

2730353 APD LOGIC Ability to customized NetNames

2730346 APD OTHER Daisy Chain tool: Ability to choose layer and feature where we want it to be routed

2742530 APD OTHER Include via structures during DC routing

2723122 APD SHAPE unable to add teardrop at t-junction

2730098 CONCEPT_HDL CORE Canceling the Physical Part Filter window closes all open windows and crashes the application

2601230 CONSTRAINT_MGR OTHER Missing Net Class column in the Spacing Constraint Matrix html Report

2743900 CONSTRAINT_MGR SYSCAP Detect corruption due to illegal constraints on a deisgn object

2715038 CONSTRAINT_MGR UI_FORMS When generating ECSet audit report, part of the generating difference report window gets left back on the screen

2728668 GRE GLOBAL Allegro 17.4 and 22.1 crash while trying to run Flowplan/Plan/Plan/topological

2726583 ORBITIO BUMP_FLOORPLA create_bump: '-offset' option cannot work well in bump pitch constraint

2732209 ORBITIO DATABASE Anchor Device: master device should not be moved by slave device

2728788 ORBITIO DIEABSTRACT DieAbstract: add feature as optional item to show the change log about die abstract merging progress

2732200 ORBITIO GUI GUI: unassign anchor device

2735692 ORBITIO GUI OIO: Reopening the IO Info Table during the same session return to the default size.

2737150 ORBITIO GUI MSFT :: Hatteras :: Selection Filter :: reset option dont work

2738543 ORBITIO GUI System Planner GUI enhancement: dim background

2736709 ORBITIO INNOVUS_IF [Modularization flow - Abstract Lef] Partition Blocks need to output abstract LEF by planner::create_module_model

2732883 ORBITIO INTEGRITY_IF 23.10: write_def cannot export [VIAS] section

2726193 ORBITIO IO_FLOORPLAN [Modulization Flow - Flatten] - Ungroup command will remove the objects in other devices use same Device Template

2730222 ORBITIO IO_FLOORPLAN pin <None> for no pin LEF was exported to verilog.

2726403 ORBITIO OTHER IO Info Import: Warning message when PADCellPinName is empty but LEF Macro has a pin.

2739486 ORBITIO SELECTION [Intel] select_obj selected unexpected object

2724613 ORBITIO TCL create_bump: rename the option '-pin_proximity' to '-pin_group_pitch'

2728829 ORBITIO TCL Tcl: need command 'create_partition' for selected objects

2728840 ORBITIO TCL Tcl: need command 'flatten_partition' for selected objects

2728370 ORBITIO VOLTUS_IF Integrity ERA flows : Expose vsrc_search_distance option to run_era

2734468 PCB_LIBRARIAN SETUP Lock settings in library SITE.CPM prevent changes to unrelated settings in PDV Setup.

2267067 PCB_LIBRARIAN SYMBOL_EDITOR Can not see and select the dot in NSE for some symbols created in old PDV (DEHDL)

2626457 PCB_LIBRARIAN SYMBOL_EDITOR Symbol graphics are not visible while placing the part in SC

2706959 PCB_LIBRARIAN SYMBOL_EDITOR Need a better way to handle initSymEd.tcl file in Site config.

2717524 PSPICE LIBRARIES IRF640 model is not simulated in release 17.4-2019

2668949 PSPICE SIMMODELS Inverting behavior of IBIS model not honored by translated IBIS model

2729172 PSPICE SIMULATOR Inconsistent display of license check-out time in .out file

2114232 PSPICE SLPS Co-simulation profile gives S-function error because .stl file is not copied from PSpice profile

2723553 PSPICE SLPS PSpice MATLAB co-simulation gives error: Error reported by S-function 'PSpice'

2745640 PULSE R2PLM-3DX PLM - 3DX connection, when I have generated my documents and want to check the Result it's not possible.

2107415 SIP_LAYOUT INTERACTIVE This design has pads defined to be only on the Top layer, (SMT) but are showing pads on other layers.

2713889 SYSTEM_CAPTURE ALIGN_DISTRIB Left align or right align functionality in System Capture does not align net names correctly.

2739765 SYSTEM_CAPTURE ASSIGN_SIGNAL System Capture using 97% System memory and crashing computer when updating design.

2729214 SYSTEM_CAPTURE CAPTURE_IMPOR Members of component with multiple symbols missing swap_info property

2737537 SYSTEM_CAPTURE CONSTRAINT_MA system capture: adding parts in a replicated block (103 times) hangs

2719769 SYSTEM_CAPTURE CUSTOM_TEXT Text boxes: Text formatting and location is inconsistent between users

2743224 SYSTEM_CAPTURE DRC Inconsistency in highlight option in the schematic audit report

2762465 SYSTEM_CAPTURE DRC Selecting Schematic Audit Violations don't allow for navigating to the respective violating circuit/component.

2736840 SYSTEM_CAPTURE IMPORT_BLOCK Migration from DE-HDL fails due to trailing spaces in signal and bus names

2744539 SYSTEM_CAPTURE IMPORT_DEHDL_ Issues during HDL Import

2726221 SYSTEM_CAPTURE INTERNATIONAL Garbled characters in Violation tab if CDS_CP_TRANSLATION_LANGUAGE

2690171 SYSTEM_CAPTURE MENUS_AND_TOO Allow user control on order of custom menu items in System Capture

2686723 SYSTEM_CAPTURE MISCELLANEOUS Need Tcl API to unmerge all table cells

2649751 SYSTEM_CAPTURE NAVIGATION System Capture navigation view merges nets at system level

2597225 SYSTEM_CAPTURE PART_MANAGER Variant Part info is not updated with the CIS Database is modified

2741947 SYSTEM_CAPTURE PRINT Version Control PDF's are visually small and must be manually made larger repeatedly.

2745388 SYSTEM_CAPTURE RENAME System Capture crash on signal rename when connecting to part

2745579 SYSTEM_CAPTURE RENAME System Capture crashes when renaming net

2674182 SYSTEM_CAPTURE REPLACE Break in bus connections after ctap symbol update in reference library.

2713261 SYSTEM_CAPTURE REPLACE Page Border with Japanese notes cannot be edited in the System Capture environment

2720379 SYSTEM_CAPTURE SYMBOL_GEN Symbol block generation for large number of pins goes outside of page border and makes symbol almost impossible to edit.

2738449 SYSTEM_CAPTURE TABLE_OF_CONT system capture TOC (Table Of Content) customization required to define page name / instance name of replicated block

2738522 SYSTEM_CAPTURE UI Cursor jumps to end of the word while renaming NetGroups or NetGroup Members

2636015 SYSTEM_DESIGN SDE_NAVIGATIO SLD - Allow the ability to define a PACK_IGNORE attribute to system block

Cadence Allegro PCB Design helps bring your innovative and bleeding-edge designs to life. The constraint-driven environment provides real-time visual feedback and ensures the functionality and manufacturability of your PCBs while allowing you to keep designing.

OrCAD is a driving force in the PCB design industry. In order to help desingers keep up with the constant pace of change Cadence has been accelerating the pace of innovation delivering a stream of updates and product enhancements to users. OrCAD provides insight into industry-first capabilities made available to customers such as real-time design, DesignTrue DFM, constraint manager, in-design analysis, and more. In July of 1999, OrCAD and its product line were acquired by Cadence Design Systems. OrCAD integrated with Cadence Allegro PCB design software creating a fully scalable solution for solving any level of PCB design challenge.

Cadence PCB Suites and Options 2022

Here we explore the various features of the Cadence PCB Suites and options.

Cadence enables global electronic design innovation and plays an essential role in the creation of today’s integrated circuits and electronics. Customers use Cadence software, hardware, IP and services to design and verify advanced semiconductors, consumer electronics, networking and telecommunications equipment, and computer systems. The company is headquartered in San Jose, Calif., with sales offices, design centers and research facilities around the world to serve the global electronics industry.

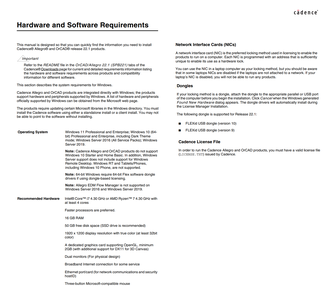

Product: Cadence Allegro and OrCAD

Version: 2022 HF2 (22.10.002)

Supported Architectures: x64

Website Home Page : www.cadence.com

Languages Supported: english

System Requirements: Windows *

Software Prerequisites: pre-installed Cadence Allegro and OrCAD 2022 (22.10.000) and above

Size: 3.5 Gb

Cadence Allegro and OrCAD 2022 (22.10.000)

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please