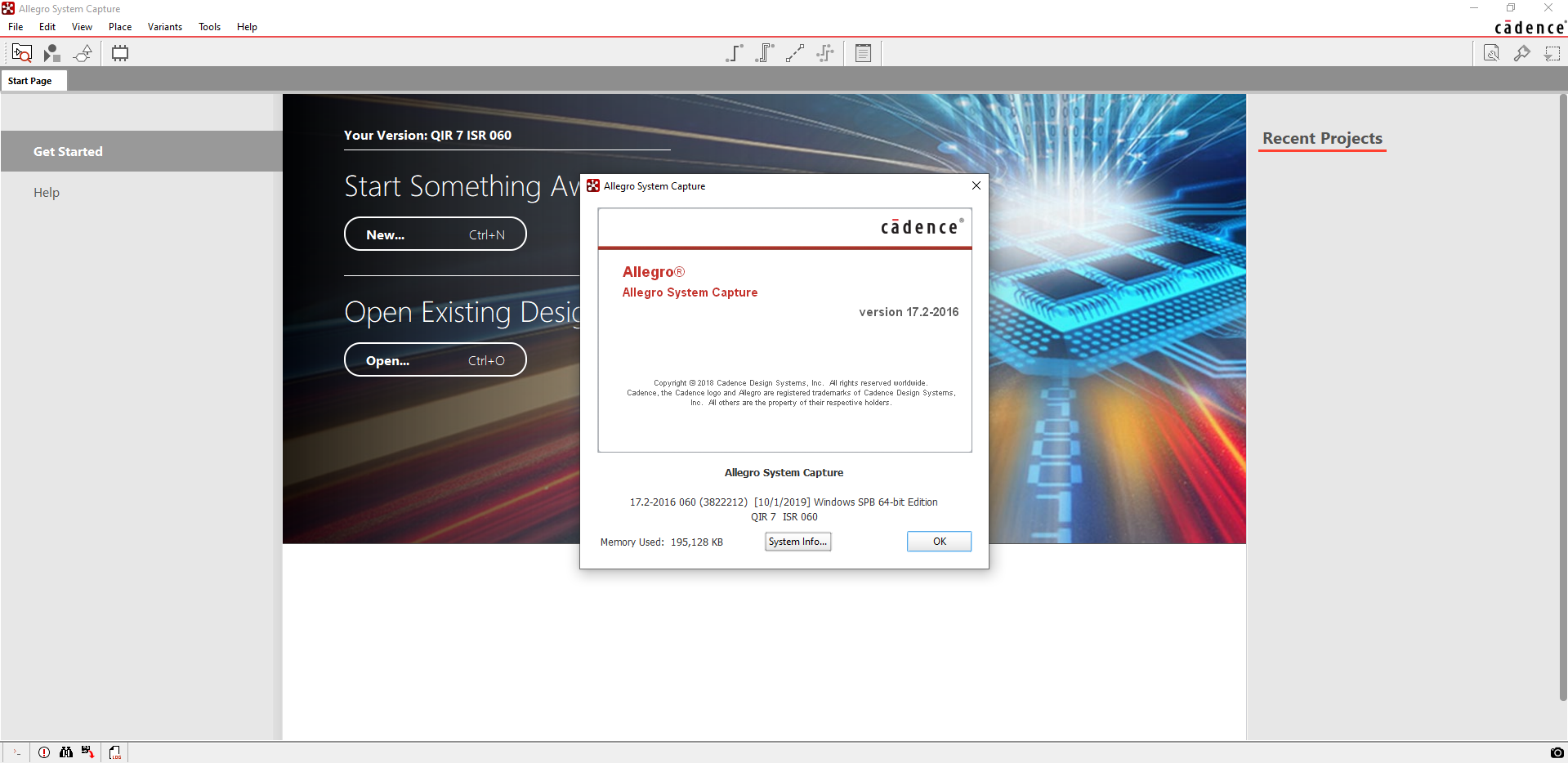

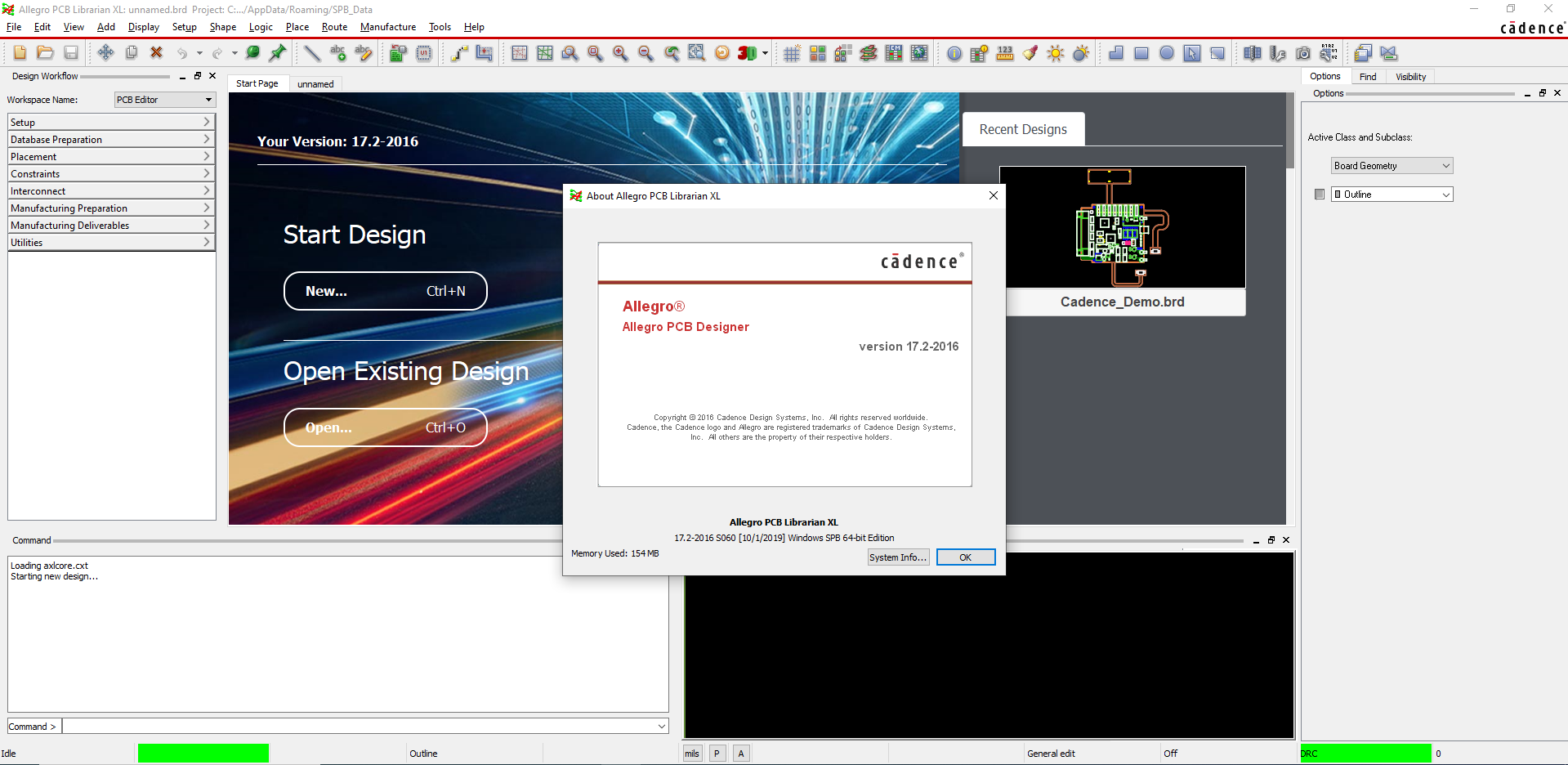

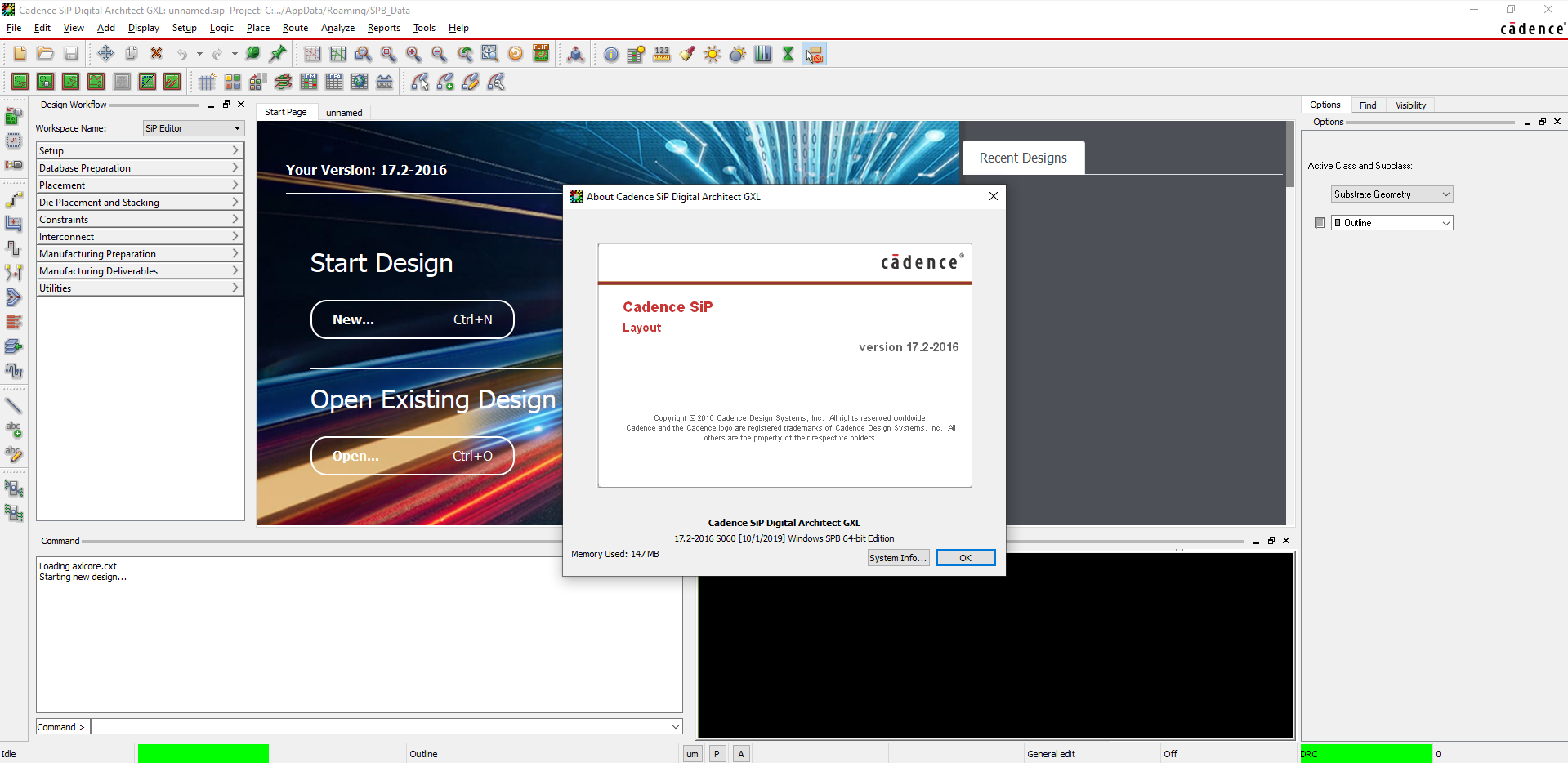

Cadence SPB Allegro and OrCAD 17.20.000-2016 HF060 | 3.9 Gb

Cadence Design Systems, Inc. , the leader in global electronic design innovation, has unveiled a new of improvements to the Cadence SPB Allegro and OrCAD 17.20 families of products aimed at boosting performance and productivity through improvements features and big fixed issues.

- ADW DBADMIN EDM is not allowing to modify step model

- ADW DBEDITOR 'BOTH' in ALT_SYMBOLS prevents correct generation of part_table.ptf

- ADW DBEDITOR DBEditor poor performance in high latency networks

- ADW LIBDISTRIBUTI EDM Library Server stops often and adwserver.out file is extremely large, more than 1GB

- ALLEGRO_EDITOR DATABASE Netlist error when importing from Capture CIS

- ALLEGRO_EDITOR DRC_CONSTR Crash during DRC: DBDoctor exits with error 'Illegal database pointer encountered'

- ALLEGRO_EDITOR DRC_CONSTR Via at SMD fit DRC not detected with rounded rectangle pads

- ALLEGRO_EDITOR EDIT_ETCH Drill hole to line DRC while sliding but 'Allow DRC' is not selected in the Options tab

- ALLEGRO_EDITOR INTERFACE_DES Error message (SPMHSY-49) displayed on running 'Tools' - 'Database Check'

- ALLEGRO_EDITOR MODULES Create Module File / Place replicate assigns incorrect netname

- ALLEGRO_EDITOR SCHEM_FTB netrev.lst is created in the wrong folder

- ALLEGRO_EDITOR STEP Update STEP Mapping Data Only should be seperate Menu/Command.

- APD VIA_STRUCTURE High speed via structure instance not adding properly

- CONCEPT_HDL CORE Error on choosing 'Enable Hierarchical Variant'

- PCB_LIBRARIAN CORE Prompt displayed for license choice marked to be used as default

- PCB_LIBRARIAN CORE Part Developer pop-up option 'Edit' for symbols displays an error message

- PCB_LIBRARIAN SYMBOL_EDITOR Part Developer new Symbol Editor: cannot move inverted pins that contain circle and dot

- PULSE R2PLM Second publish with CPM-derived item number and cadName set to $NUMBER causes 'an item is not unique' error

- SIP_LAYOUT ORBITIO_IF Support keepout translation between OrbitIO and Allegro layout/physical editors

- ADW DBEDITOR 'BOTH' in ALT_SYMBOLS prevents correct generation of part_table.ptf

- ADW DBEDITOR DBEditor poor performance in high latency networks

- ADW LIBDISTRIBUTI EDM Library Server stops often and adwserver.out file is extremely large, more than 1GB

- ALLEGRO_EDITOR DATABASE Netlist error when importing from Capture CIS

- ALLEGRO_EDITOR DRC_CONSTR Crash during DRC: DBDoctor exits with error 'Illegal database pointer encountered'

- ALLEGRO_EDITOR DRC_CONSTR Via at SMD fit DRC not detected with rounded rectangle pads

- ALLEGRO_EDITOR EDIT_ETCH Drill hole to line DRC while sliding but 'Allow DRC' is not selected in the Options tab

- ALLEGRO_EDITOR INTERFACE_DES Error message (SPMHSY-49) displayed on running 'Tools' - 'Database Check'

- ALLEGRO_EDITOR MODULES Create Module File / Place replicate assigns incorrect netname

- ALLEGRO_EDITOR SCHEM_FTB netrev.lst is created in the wrong folder

- ALLEGRO_EDITOR STEP Update STEP Mapping Data Only should be seperate Menu/Command.

- APD VIA_STRUCTURE High speed via structure instance not adding properly

- CONCEPT_HDL CORE Error on choosing 'Enable Hierarchical Variant'

- PCB_LIBRARIAN CORE Prompt displayed for license choice marked to be used as default

- PCB_LIBRARIAN CORE Part Developer pop-up option 'Edit' for symbols displays an error message

- PCB_LIBRARIAN SYMBOL_EDITOR Part Developer new Symbol Editor: cannot move inverted pins that contain circle and dot

- PULSE R2PLM Second publish with CPM-derived item number and cadName set to $NUMBER causes 'an item is not unique' error

- SIP_LAYOUT ORBITIO_IF Support keepout translation between OrbitIO and Allegro layout/physical editors

Cadence Design Systems announced new capabilities for OrCAD Capture, PSpice Designer and PCB Designer 17.2-2016 that address challenges with flex and rigid-flex design as well as mixed-signal simulation complexities in IoT, wearables and wireless mobile devices. This latest release reduces PCB development time by addressing the need to design reliable circuits for smaller, more compact devices.

This OrCAD portfolio includes new advanced technology enabled for integrated rigid-flex planning, design and real-time visualization, as well as built-in translators that enable direct design imports from select EDA vendors. PSpice Designer now supports system-level simulation using C/C++/SystemC and VerilogA, via the new PSpice compact model interface. This enables hardware/software virtual prototyping so that electrical engineers can design and simulate intelligent IoT devices. OrCAD is the only fully scalable PCB design solution available in the market that seamlessly transitions from mainstream to enterprise PCB solution with the Allegro environment.

To enable a faster and more efficient flex and rigid-flex design creation critical to IoT, wearables and wireless devices, the OrCAD portfolio uses a new multi-stack-up database capability and extensive in-design inter-layer checks, which helps users avoid errors introduced through manual checking. The OrCAD portfolio also features enhancements targeted towards improving PCB editors’ productivity and ease-of-use in padstack editing, constraint management, shape editing and in-design DRCs. To address efficiency needs, the portfolio includes an advanced design differencing engine that enables design review with global teams using state of art visuals. Finally, to give designers more control over their design component annotation process, advanced annotation and auto-referencing capabilities are now available.

Allegro 17.2 release introduces many new capabilities for Flex and Rigid-Flex designs.

Cadence enables global electronic design innovation and plays an essential role in the creation of today’s integrated circuits and electronics. Customers use Cadence software, hardware, IP and services to design and verify advanced semiconductors, consumer electronics, networking and telecommunications equipment, and computer systems. The company is headquartered in San Jose, Calif., with sales offices, design centers and research facilities around the world to serve the global electronics industry.

Product: Cadence SPB Allegro and OrCAD (Including EDM)

Version: 17.20.000-2016 HF060

Supported Architectures: x64

Website Home Page : www.cadence.com

Language: english

System Requirements: PC *

Supported Operating Systems: *

System Requirements: Cadence SPB Allegro and OrCAD (Including EDM) version 17.20.000-2016 and above

Size: 3.9 Gb

Cadence Allegro and OrCAD 17.2-2016 Hardware and Software Requirements:

Operating System:

Microsoft Windows 7 Professional, Enterprise, Ultimate or Home Premium (64-bit); Windows 8 (64-bit) (All Service Packs); Windows 10 (64-bit); Windows 2008 R2 Server; Windows 2012 Server (All Service Packs).

Note:Cadence Allegro and OrCAD (Including EDM) products do not support Windows 7 Starter and Home Basic. In addition, Windows Server support does not include support for Windows Remote Desktop. Windows RT and Tablets are not supported.

Minimum Hardware:

- Intel Pentium 4 or AMD Athlon XP 2000 with multi-core CPU

- Ram:8 GB RAM

- Virtual memory at least twice physical memory

- 50 GB free disk space

- 1,024 x 768 display resolution with true color (16-bit color)

- Broadband Internet connection for some service

- Ethernet card (for network communications and security hostID)

- Three-button Microsoft-compatible mouse

Recommended Hardware:

- Intel Core 2 Duo 2.66 GHz or AMD Athlon 64 X2 5200+

- Note: Faster processors are preferred.

- RAM:8 GB RAM

- Disk:500 GB free disk space

- Display:1,280 x 1024 display resolution with true color (at least 32bit color)

- GPU:A dedicated graphics card

- Display:Dual monitors

- Microsoft Internet Explorer 11.0 or later

Operating System:

Microsoft Windows 7 Professional, Enterprise, Ultimate or Home Premium (64-bit); Windows 8 (64-bit) (All Service Packs); Windows 10 (64-bit); Windows 2008 R2 Server; Windows 2012 Server (All Service Packs).

Note:Cadence Allegro and OrCAD (Including EDM) products do not support Windows 7 Starter and Home Basic. In addition, Windows Server support does not include support for Windows Remote Desktop. Windows RT and Tablets are not supported.

Minimum Hardware:

- Intel Pentium 4 or AMD Athlon XP 2000 with multi-core CPU

- Ram:8 GB RAM

- Virtual memory at least twice physical memory

- 50 GB free disk space

- 1,024 x 768 display resolution with true color (16-bit color)

- Broadband Internet connection for some service

- Ethernet card (for network communications and security hostID)

- Three-button Microsoft-compatible mouse

Recommended Hardware:

- Intel Core 2 Duo 2.66 GHz or AMD Athlon 64 X2 5200+

- Note: Faster processors are preferred.

- RAM:8 GB RAM

- Disk:500 GB free disk space

- Display:1,280 x 1024 display resolution with true color (at least 32bit color)

- GPU:A dedicated graphics card

- Display:Dual monitors

- Microsoft Internet Explorer 11.0 or later

Cadence Allegro and OrCAD 17.20.000-2016

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please