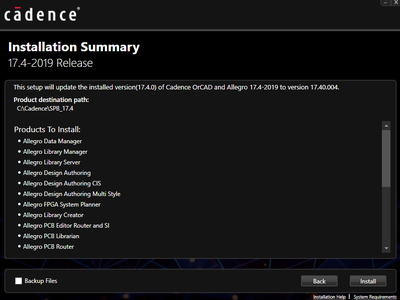

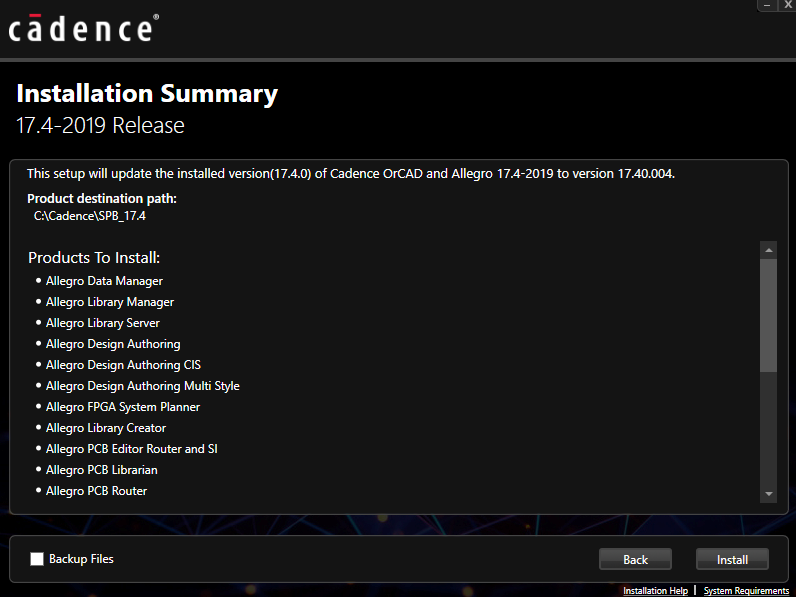

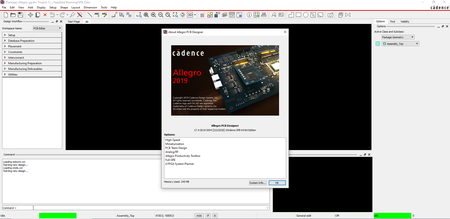

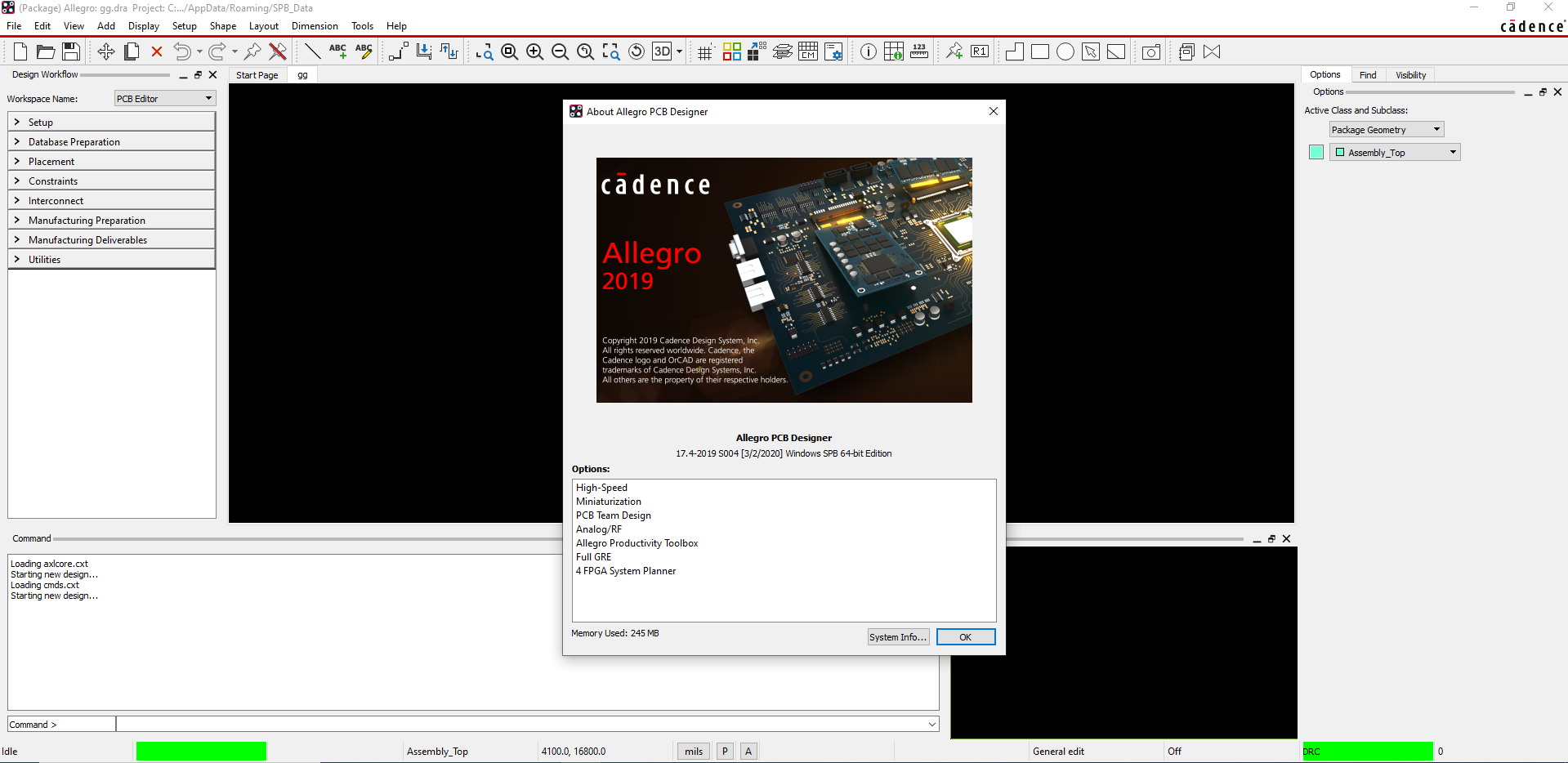

Cadence SPB Allegro and OrCAD 17.40.000-2019 HF004 | 2.7 Gb

Cadence Design Systems, Inc. , the leader in global electronic design innovation, has unveiled a new of improvements in hot fix 004 to the Cadence SPB Allegro and OrCAD 17.40 families of products aimed at boosting performance and productivity through improvements features and big fixed issues.

- ADW DBEDITOR dbeditor - old version retained when using Copy-as

- ADW PART_BROWSER Hyperlink support with pipe to shorten the path does not work in new Component Browser

- ALLEGRO_EDITOR DFM DFM Copper Feature reporting Min shape width (positive) as 0 mils

- ALLEGRO_EDITOR DFM DFM Cutout to shape reports a violation at 9.44 mils when rule is set to 8 mils.

- ALLEGRO_EDITOR EDIT_ETCH Sliding vias containing dynamic teardrop jump away in unpredictable directions

- ALLEGRO_EDITOR EDIT_ETCH Lag in commands when working with board in release 17.2-2016 and 16.6

- ALLEGRO_EDITOR MULTI_USER Symphony team design error with intermittent crash on refreshing DB

- ALLEGRO_EDITOR PLACEMENT Place Manual on fixed part causes crash.

- ALLEGRO_EDITOR SCRIPTS View switching on the visibility tab does not work in script.

- ALLEGRO_EDITOR UI_FORMS Issue with working layers form - cannot see all layers in one go.

- APD BGA_GENERATOR 'add connect' does not snap to the BGA pins for padstacks other than SMD

- APD OTHER axlGeoClosestPointOnArc produces incorrect results

- APD REPORTS Net delay report is stuck on one net

- CAPTURE BACKANNOTATE Error message while backannotating after swapping in PCB Editor

- CAPTURE BACKANNOTATE Design Sync gives Error message when PCB Editor has used function swap, however it does swap the functions in schematic.

- CAPTURE DRC DRC window reports each DRC warning twice

- CAPTURE DRC Online DRCs to locate footprints from path relative to active board

- CAPTURE DRC Waiving a DRC error in release 17.4-2019: Not listed in DRC windows

- CAPTURE DRC Missing function for Waive DRCs in Find window in Capture in release 17.4-2019

- CAPTURE LIBRARY CONNECTOR.OLB\CON2 has predefined footprint value in release 17.4-2019

- CAPTURE ONLINEDRC Capture crashes when copying hierarchical block multiple times with Online DRC on

- CAPTURE ONLINEDRC Online DRC reports error of missing pins with H-Part, hence does not perform Design Sync

- CAPTURE ONLINEDRC Footprint are still listed as missing in Online DRC

- CAPTURE ONLINEDRC Online DRC does not support parts with CLASS set to MECHANICAL

- CONCEPT_HDL CORE Note command results in alignment issue due to spaces added to the end of words

- CONCEPT_HDL CREFER DE-HDL crashes on setting 'Generate Cross References for all nets' from 'Cross Referencer Options' to run CRefer

- CONCEPT_HDL CREFER Crefer generating schematic with wrong RefDes without suffix

- CONCEPT_HDL OTHER Pin Names not backannotating to Allegro Design Entry HDL

- CONSTRAINT_MGR ANALYSIS Attempting to add a via to a .dra will crash Allegro with no dump file generated.

- CONSTRAINT_MGR UI_FORMS Length values are light gray in Net > RPD worksheet in CM

- CONSTRAINT_MGR UI_FORMS UI issue: CM auto scrolling to the left when net name is selected

- EAGLE_TRANSLATOR PCB_EDITOR PCB Translator stacks all of the incoming components in the lower left corner of the board.

- PCB_LIBRARIAN SYM_CREATOR_C Value of $PN

- PULSE UNIFIED_SEARC Cannot access third-party components using valid credentials from Capture

- SIG_EXPLORER SIMULATION SigXplorer crashes when using the 'Manage LayerStacks' option.

- SIP_LAYOUT DEGASSING Degassing does not add voids to the entire shape

- SIP_LAYOUT DEGASSING Teardrop prevents the shape degassing command from completing

- SYSTEM_CAPTURE CUSTOM_TEXT Custom variables become read-only after a note is added to the schematic.

- SYSTEM_CAPTURE IMPORT_DEHDL_Unable to import the project sheets, fails for a page

- SYSTEM_CAPTURE PROPERTY_EDIT Cannot change project variables

- SYSTEM_CAPTURE PROPERTY_EDIT Unable to exit edit mode after editing RefDes value on canvas

- ADW PART_BROWSER Hyperlink support with pipe to shorten the path does not work in new Component Browser

- ALLEGRO_EDITOR DFM DFM Copper Feature reporting Min shape width (positive) as 0 mils

- ALLEGRO_EDITOR DFM DFM Cutout to shape reports a violation at 9.44 mils when rule is set to 8 mils.

- ALLEGRO_EDITOR EDIT_ETCH Sliding vias containing dynamic teardrop jump away in unpredictable directions

- ALLEGRO_EDITOR EDIT_ETCH Lag in commands when working with board in release 17.2-2016 and 16.6

- ALLEGRO_EDITOR MULTI_USER Symphony team design error with intermittent crash on refreshing DB

- ALLEGRO_EDITOR PLACEMENT Place Manual on fixed part causes crash.

- ALLEGRO_EDITOR SCRIPTS View switching on the visibility tab does not work in script.

- ALLEGRO_EDITOR UI_FORMS Issue with working layers form - cannot see all layers in one go.

- APD BGA_GENERATOR 'add connect' does not snap to the BGA pins for padstacks other than SMD

- APD OTHER axlGeoClosestPointOnArc produces incorrect results

- APD REPORTS Net delay report is stuck on one net

- CAPTURE BACKANNOTATE Error message while backannotating after swapping in PCB Editor

- CAPTURE BACKANNOTATE Design Sync gives Error message when PCB Editor has used function swap, however it does swap the functions in schematic.

- CAPTURE DRC DRC window reports each DRC warning twice

- CAPTURE DRC Online DRCs to locate footprints from path relative to active board

- CAPTURE DRC Waiving a DRC error in release 17.4-2019: Not listed in DRC windows

- CAPTURE DRC Missing function for Waive DRCs in Find window in Capture in release 17.4-2019

- CAPTURE LIBRARY CONNECTOR.OLB\CON2 has predefined footprint value in release 17.4-2019

- CAPTURE ONLINEDRC Capture crashes when copying hierarchical block multiple times with Online DRC on

- CAPTURE ONLINEDRC Online DRC reports error of missing pins with H-Part, hence does not perform Design Sync

- CAPTURE ONLINEDRC Footprint are still listed as missing in Online DRC

- CAPTURE ONLINEDRC Online DRC does not support parts with CLASS set to MECHANICAL

- CONCEPT_HDL CORE Note command results in alignment issue due to spaces added to the end of words

- CONCEPT_HDL CREFER DE-HDL crashes on setting 'Generate Cross References for all nets' from 'Cross Referencer Options' to run CRefer

- CONCEPT_HDL CREFER Crefer generating schematic with wrong RefDes without suffix

- CONCEPT_HDL OTHER Pin Names not backannotating to Allegro Design Entry HDL

- CONSTRAINT_MGR ANALYSIS Attempting to add a via to a .dra will crash Allegro with no dump file generated.

- CONSTRAINT_MGR UI_FORMS Length values are light gray in Net > RPD worksheet in CM

- CONSTRAINT_MGR UI_FORMS UI issue: CM auto scrolling to the left when net name is selected

- EAGLE_TRANSLATOR PCB_EDITOR PCB Translator stacks all of the incoming components in the lower left corner of the board.

- PCB_LIBRARIAN SYM_CREATOR_C Value of $PN

- PULSE UNIFIED_SEARC Cannot access third-party components using valid credentials from Capture

- SIG_EXPLORER SIMULATION SigXplorer crashes when using the 'Manage LayerStacks' option.

- SIP_LAYOUT DEGASSING Degassing does not add voids to the entire shape

- SIP_LAYOUT DEGASSING Teardrop prevents the shape degassing command from completing

- SYSTEM_CAPTURE CUSTOM_TEXT Custom variables become read-only after a note is added to the schematic.

- SYSTEM_CAPTURE IMPORT_DEHDL_Unable to import the project sheets, fails for a page

- SYSTEM_CAPTURE PROPERTY_EDIT Cannot change project variables

- SYSTEM_CAPTURE PROPERTY_EDIT Unable to exit edit mode after editing RefDes value on canvas

Cadence OrCAD and Allegro 17.4-2019 is a sleeker and more modern version of the OrCAD and Allegro release, with enhanced usability and a slew of new productivity- enhancing features. You get more intuitive and easy- to- use flows that enable optimized schematic- to- board- to- manufacturing transitions. So, whether you design schematics, work with physical layouts, manage or create libraries and parts, or administer ECAD processes, there are features in this release that will benefit you.

Starting with OrCAD and Cadence Allegro PCB - Tutorial for Beginners

Cadence enables global electronic design innovation and plays an essential role in the creation of today’s integrated circuits and electronics. Customers use Cadence software, hardware, IP and services to design and verify advanced semiconductors, consumer electronics, networking and telecommunications equipment, and computer systems. The company is headquartered in San Jose, Calif., with sales offices, design centers and research facilities around the world to serve the global electronics industry.

Product: Cadence SPB Allegro and OrCAD

Version: 17.40.000-2019 HF004

Supported Architectures: x64

Website Home Page : www.cadence.com

Language: english

System Requirements: PC *

Supported Operating Systems: *

Software Prerequisites: Cadence SPB Allegro and OrCAD 17.40.000- 2019 and above

Size: 2.7 Gb

System Requirements:

OS: Windows 10 (64-bit) Professional, Windows Server 2012 (All Service Packs); Windows Server 2012 R2; Windows Server 2016.

CPU: Intel Core i7 4.30 GHz or AMD Ryzen 7 4.30 GHz with at least 4 cores

Memory: 16 GB RAM

Space: 50 GB free disk space (SSD drive is recommended)

Display: 1920 x 1200 display resolution with true color (at least 32bit color)

GPU: A dedicated graphics card supporting OpenGL, minimum 2GB (with additional support for DX11 for 3D Canvas)

Monitors: Dual monitors (For physical design)

Supported MATLAB Version: R2019A-64Bit (For the PSpice-MATLAB interface)

OS: Windows 10 (64-bit) Professional, Windows Server 2012 (All Service Packs); Windows Server 2012 R2; Windows Server 2016.

CPU: Intel Core i7 4.30 GHz or AMD Ryzen 7 4.30 GHz with at least 4 cores

Memory: 16 GB RAM

Space: 50 GB free disk space (SSD drive is recommended)

Display: 1920 x 1200 display resolution with true color (at least 32bit color)

GPU: A dedicated graphics card supporting OpenGL, minimum 2GB (with additional support for DX11 for 3D Canvas)

Monitors: Dual monitors (For physical design)

Supported MATLAB Version: R2019A-64Bit (For the PSpice-MATLAB interface)

Cadence SPB Allegro and OrCAD 17.40.000-2019

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please