Cadence Virtuoso, Release Version IC6.1.8 ISR30 | 11.6 Gb

Cadence Design Systems, Inc. , the leader in global electronic design innovation, has unveiled Virtuoso, Release Version IC6.1.8 ISR30 is a holistic, system-based solution that provides the functionality to drive simulation and LVS-clean layout of ICs and packages from a single schematic.

CCRs Fixed in IC6.1.8 and/or ICADVM20.1 ISR30 - Date: February 2023

2758141 Tags are not retained when corners are moved

2756190 Using diffstbprobe at a sub-block during stability analysis gives a netlisting error

2755697 Checking out a schematic view and canceling the action makes a design managed maestro cellview read-only

2755363 The x_sides default argument of leModifyCorner is not applicable starting from IC6.1.8 ISR27

2754780 Wrong LPP chosen for the creation of VDR marker when voltage is negative

2748741 Virtuoso ADE errors out with SPECTRE-16850 message while running a stability analysis

2748446 diffstbprobe does not get netlisted correctly when probed at a lower level and errors out with SPECTRE-16850 message

2747594 Opening a schematic in edit mode takes more time than expected

2746842 diffstbprobe does not get netlisted correctly when probed at a lower level

2746503 OCEAN measure for Measure Across All does not work from IC6.1.8 ISR24

2746473 Signals that can be plotted from Results Browser cannot be plotted from ADE Assembler

2744452 Assisted flow breaks when concatenating SIPOA_TLINE properties and misses a blank

2743372 Netlist error when user-defined variables are imported from ADE L to a maestro cellview

2743210 MAS calculations get an eval error for both corners

2743054 The 'Plot/print vs' argument is unavailable even when the 'Number of occurrences' is set to 'multiple' in the 'delay' function

2741825 In the Virtuoso Automated Placement and Routing flow, removing an analog guard ring must restore the Modgen

2741027 Maestro cellview using multiple DSPF views gets stuck in netlisting phase

2740708 minEndOfLineSpacing and widthRanges give false endToEndSpacing spacing violations

2740342 Unable to change the spacing after dropping vias when Create Bus command restarts from an existing bus

2740257 High Current design intent push-up does not work if pre-existing top design intent does not have all its members defined

2740218 Include the transient dynamic parameter statement to the Spectre netlist generated by Virtuoso ADE

2739823 A design managed maestro view automatically changes to read-only when the check-in status of schematic or symbol views is changed

2739748 Virtuoso Space-based Router is not honoring maxLength routing constraint for M1

2739393 Reliability analysis in an AMS simulation returns an error when a variable is used for Temperature in age analysis

2739127 Reliability analysis in an AMS simulation gets stuck in netlisting phase due to a SKILL error

2739049 Virtuoso needs a few minutes to open a customer-specific maestro view

2737700 Simulation remains incomplete because some points get stuck in netlisting

2737112 Simulation in ADE Explorer is slow when Optimize Single Point Run and ignoreDesignChangesDuringRun are enabled and a third-party simulator is used

2736915 Check in of a schematic cellview makes a design managed maestro cellview read-only

2735786 An error occurs when plotting a BER curve for an eye diagram

2735511 Netlisting fails with errors for one maestro test but completes successfully for other tests

2735426 Stimuli Assignment form does not find variables defined in Vsources

2735371 Innovus produces a core file when trying to restore an MSOA design

2735273 maesimserv process cannot be launched on SUSE Linux Enterprise Server

2735235 Quick Align with Copy reference does not copy all preselected source objects

2735131 Within a Virtual Hierarchy, instances do not snap to a row region

2733721 Simulation remains incomplete because some points get stuck in netlisting

2733131 The 'Save By Subckt Instances' table does not save new entries in ADE Assembler, works fine in ADE Explorer

2731726 Custom calculator function not running correctly in LSCS

2731671 The openResults function returns an incorrect output when run from an expression evaluator process

2731626 Value for the Preset Override field is not set correctly when spectreXPresetOverride is set to customized

2730582 Row-based placement does not place standard cells due to the presence of markers

2730459 SKILL functions for changing the background color of Waveform windows shall be made public

2729717 Quick Align with Copy reference does not work on the first attempt

2729553 Batch mode process is not killed when the job is run in LSCS mode

2729383 The new value set for a local scoped option does not get updated in the netlist

2729236 Tooltip is not correct for the function YP in the Expression Builder

2729137 While specifying a path using design variables, expand the variable before specifying the path to the working directory

2728939 Assisted Export seems to drop SIPOA_TLINE property for some Pcell instances

2728331 Virtuoso exits unexpectedly when handling event filters

2727624 ADE Assembler does not refresh the Outputs Setup tab

2727127 Virtuoso ElectroMagnetic-EMX: EM extracted view fails with top-level selection

2726375 Custom parasitic parameters specified in the Semino section are not considered correctly for SmartView netlisting

2725119 Issue when using VAR in the model section for dependent variable

2724998 The values in the Dynamic Parameter table are retained even when all the rows are deleted

2724963 The VCP TAP Insertion flow and row creation are not consistent within a Virtuoso session

2724448 DEVICE_TYPE CDF parameter value from instance should be honored for compDef use

2724410 ciDiReplaceOrAddPropertyGroupDef fails as design intent profiles are not loaded during Virtuoso startup

2724247 Display proper errors when wrong DUTs are selected

2724137 Trunk Generation is not working when multiple local WSP regions exist and the routing area is PRboundary

2723543 PAM4 level 0 histogram cannot be evaluated in ADE outputs

2723401 Improve the error message for the netlist error received from a node entry for pnoise analysis

2722395 Extraction errors after flatten command due to disconnect between the no conn symbol and wire segment

2722012 Virtuoso stops unexpectedly after frequent right clicks in the Corners Setup form

2721484 diffstbprobe does not get netlisted correctly when probed at a lower level

2721378 Contents of the graph labels cannot be copied and pasted using the RMB options

2721219 CDL netlister does not honor lxRemoveDevice property on vdc when vdc is connected to iterated instance

2721216 CDL netlister does not honor lxRemoveDevice property on iprobe when iprobe is connected to subckts

2721215 CDL netlister does not honor lxRemoveDevice property on diffstbprobe when diffstbprobe is connected to subckts

2720860 Virtuoso stops responding and Window Manager freezes after the global variables with config sweeps are dragged and dropped from active setup to run plan

2720616 ciCacheGet(cv) models return nil when setting envSet 'conTypesOnDemand'

2719834 Netlisting must report errors for removed or renamed nport instances with S-parameter cell specification

2719662 Unable to run Spectre EMIR analysis from an OCEAN XL saved from Virtuoso ADE

2719407 Netlist syntax error is reported during fault generation

2718442 AMS UNL netlisting error in an AMS simulation run from a maestro cellview

2718126 Extract the desired signal from AC psf database

2718076 Auto Generator Hierarchy is enhanced to reuse cell methodology for custom cells

2717993 SKILL Lint rule for pcDefinePCell incorrectly informs about a global variable in the default parameter expression

2717840 Check in of a design managed schematic cellview incorrectly tries to make a maestro cellview read-only

2716018 Net Tracer warning message displayed regarding the attempt to create a layer

2715531 Wrong LPP chosen for the creation of VDR marker when voltage is negative

2715313 The Insert Filler Cells command does not respect the cellname filter specified in the row template

2714802 The Map Bus Name does not replace <> to []" when hnlMapNetInName is set in simrc

2714610 User-defined macros differ due to antenna diode related ground pin in a design

2714562 SpiceIn does not update port direction with pre-existing symbol when the Overwrite cellviews option is set to ALL

2713404 check_single_shape needs to gather sameMetalAlignedCut violations

2713171 Create new dataset causes existing datasets to be disabled

2712043 Incorrect related power pin extraction by Virtuoso Power Manager

2711344 Warning message displayed that techCreateLayer layer number 1150 already exists when adding a net trace

2708948 Remove the limit of 10K points in a single fault simulation run

2708663 Issue in isolation_enable_condition derivation utility

2708499 SiP-Design Rile Check (DRC) flow should not have dependency on the order of Virtuoso and SPB tools in the PATH environment variable

2706430 AutoVia is leading to sameMetalAlignedCuts violation

2706389 Netlist error is reported after the hierarchical copy of a library with a smart view

2706053 Error messages are reported when closing the layout window

2705719 Remove hspice view for rcwireload component in the Analog Library

2703677 Plot across Corners and Plot All not working for parameterized getAsciiWave

2698182 Router having issues with 3 and 4 terminal bus structures

2697590 Object layer-purpose pairs incorrectly removed from the Layers palette

2694797 Results of nested sweep pss-fd cannot be plotted in Virtuoso Visualization and Analysis XL using Calculator

2692670 Renaming or copying an EMX library does not complete the command successfully.

2692666 Results are not plotted in Virtuoso Visualization and Analysis XL using Calculator, but are plotted fine in the Results Browser

2688023 Renaming or copying an EMX library does not complete the command successfully

2684369 Neither upfront error checking nor calcVal lint check the correctness of the ?result argument

2683848 User-defined macros differ due to the pg function in a design

2683846 User-defined macros differ due to antenna diode related power pin in a design

2682917 Incorrect sorting of Pass/Fail values

2681402 VALE schematic migration: Schematic with off grid wiring created short on migrated schematic

2677663 DRD functionality does not recognize some of the layers listed in layout

2677457 The Link Graph feature does not work as expected when multiple axes limits are set manually

2677449 The Link Graph feature does not work as expected when multiple axes limits are set manually

2677436 The Link Graph feature does not work as expected when multiple axes limits are set manually

2677429 The Link Graph feature does not work as expected when multiple axes limits are set manually

2674226 Cannot process batch runs in parallel with implementation sets

2672998 AMS UNL netlisting issue due to a missing presistor instance

2662923 Users need to restart Virtuoso to make the eye diagram work

2648166 Area Estimator is enhanced to support i1278 flextor schematic Pcell

2627515 An incorrect error message is shown when corners are enabled in the run plan but disabled in Data View

2610969 VDR labels with different values created on same layer

2608305 Using VAR syntax in noise circle expression gives an error in ADE Assembler, works fine in ADE Explorer

2602408 LSCS job remains pending indefinitely for post-layout simulations across corners and certain output expressions

2600449 Renaming or copying an EMX library does not complete the command successfully

2578976 Changing the 'Common reference' setting in Property Editor form does not work as expected

2568872 Cannot change Stage pulldown to show stress simulation in Reliability Report view for age+she

2557411 Voltus-Fi: Violation Browser option is repeatedly selected and deselected and Virtuoso stops responding

2542276 Virtuoso stops unexpectedly while specifying Checks/Asserts options

2518102 Selecting one Max Resistance highlights all other Max Resistance paths in schematic

2481205 maeSetVar does not work for local variables when the current value is a sweep set

2477035 Design variable is not seen in Design Variables field in ADE Explorer after importing setup

2336033 Data View/Setup Assistant shows overridden errpreset for Spectre X, APS, and Spectre, misleading users

2009590 Virtuoso Visualization and Analysis XL exits unexpectedly when running simulations

1485721 The Running step Abstract form does not display the Overlap and Grid tabs

February 2023

2756190 Using diffstbprobe at a sub-block during stability analysis gives a netlisting error

2755697 Checking out a schematic view and canceling the action makes a design managed maestro cellview read-only

2755363 The x_sides default argument of leModifyCorner is not applicable starting from IC6.1.8 ISR27

2754780 Wrong LPP chosen for the creation of VDR marker when voltage is negative

2748741 Virtuoso ADE errors out with SPECTRE-16850 message while running a stability analysis

2748446 diffstbprobe does not get netlisted correctly when probed at a lower level and errors out with SPECTRE-16850 message

2747594 Opening a schematic in edit mode takes more time than expected

2746842 diffstbprobe does not get netlisted correctly when probed at a lower level

2746503 OCEAN measure for Measure Across All does not work from IC6.1.8 ISR24

2746473 Signals that can be plotted from Results Browser cannot be plotted from ADE Assembler

2744452 Assisted flow breaks when concatenating SIPOA_TLINE properties and misses a blank

2743372 Netlist error when user-defined variables are imported from ADE L to a maestro cellview

2743210 MAS calculations get an eval error for both corners

2743054 The 'Plot/print vs' argument is unavailable even when the 'Number of occurrences' is set to 'multiple' in the 'delay' function

2741825 In the Virtuoso Automated Placement and Routing flow, removing an analog guard ring must restore the Modgen

2741027 Maestro cellview using multiple DSPF views gets stuck in netlisting phase

2740708 minEndOfLineSpacing and widthRanges give false endToEndSpacing spacing violations

2740342 Unable to change the spacing after dropping vias when Create Bus command restarts from an existing bus

2740257 High Current design intent push-up does not work if pre-existing top design intent does not have all its members defined

2740218 Include the transient dynamic parameter statement to the Spectre netlist generated by Virtuoso ADE

2739823 A design managed maestro view automatically changes to read-only when the check-in status of schematic or symbol views is changed

2739748 Virtuoso Space-based Router is not honoring maxLength routing constraint for M1

2739393 Reliability analysis in an AMS simulation returns an error when a variable is used for Temperature in age analysis

2739127 Reliability analysis in an AMS simulation gets stuck in netlisting phase due to a SKILL error

2739049 Virtuoso needs a few minutes to open a customer-specific maestro view

2737700 Simulation remains incomplete because some points get stuck in netlisting

2737112 Simulation in ADE Explorer is slow when Optimize Single Point Run and ignoreDesignChangesDuringRun are enabled and a third-party simulator is used

2736915 Check in of a schematic cellview makes a design managed maestro cellview read-only

2735786 An error occurs when plotting a BER curve for an eye diagram

2735511 Netlisting fails with errors for one maestro test but completes successfully for other tests

2735426 Stimuli Assignment form does not find variables defined in Vsources

2735371 Innovus produces a core file when trying to restore an MSOA design

2735273 maesimserv process cannot be launched on SUSE Linux Enterprise Server

2735235 Quick Align with Copy reference does not copy all preselected source objects

2735131 Within a Virtual Hierarchy, instances do not snap to a row region

2733721 Simulation remains incomplete because some points get stuck in netlisting

2733131 The 'Save By Subckt Instances' table does not save new entries in ADE Assembler, works fine in ADE Explorer

2731726 Custom calculator function not running correctly in LSCS

2731671 The openResults function returns an incorrect output when run from an expression evaluator process

2731626 Value for the Preset Override field is not set correctly when spectreXPresetOverride is set to customized

2730582 Row-based placement does not place standard cells due to the presence of markers

2730459 SKILL functions for changing the background color of Waveform windows shall be made public

2729717 Quick Align with Copy reference does not work on the first attempt

2729553 Batch mode process is not killed when the job is run in LSCS mode

2729383 The new value set for a local scoped option does not get updated in the netlist

2729236 Tooltip is not correct for the function YP in the Expression Builder

2729137 While specifying a path using design variables, expand the variable before specifying the path to the working directory

2728939 Assisted Export seems to drop SIPOA_TLINE property for some Pcell instances

2728331 Virtuoso exits unexpectedly when handling event filters

2727624 ADE Assembler does not refresh the Outputs Setup tab

2727127 Virtuoso ElectroMagnetic-EMX: EM extracted view fails with top-level selection

2726375 Custom parasitic parameters specified in the Semino section are not considered correctly for SmartView netlisting

2725119 Issue when using VAR in the model section for dependent variable

2724998 The values in the Dynamic Parameter table are retained even when all the rows are deleted

2724963 The VCP TAP Insertion flow and row creation are not consistent within a Virtuoso session

2724448 DEVICE_TYPE CDF parameter value from instance should be honored for compDef use

2724410 ciDiReplaceOrAddPropertyGroupDef fails as design intent profiles are not loaded during Virtuoso startup

2724247 Display proper errors when wrong DUTs are selected

2724137 Trunk Generation is not working when multiple local WSP regions exist and the routing area is PRboundary

2723543 PAM4 level 0 histogram cannot be evaluated in ADE outputs

2723401 Improve the error message for the netlist error received from a node entry for pnoise analysis

2722395 Extraction errors after flatten command due to disconnect between the no conn symbol and wire segment

2722012 Virtuoso stops unexpectedly after frequent right clicks in the Corners Setup form

2721484 diffstbprobe does not get netlisted correctly when probed at a lower level

2721378 Contents of the graph labels cannot be copied and pasted using the RMB options

2721219 CDL netlister does not honor lxRemoveDevice property on vdc when vdc is connected to iterated instance

2721216 CDL netlister does not honor lxRemoveDevice property on iprobe when iprobe is connected to subckts

2721215 CDL netlister does not honor lxRemoveDevice property on diffstbprobe when diffstbprobe is connected to subckts

2720860 Virtuoso stops responding and Window Manager freezes after the global variables with config sweeps are dragged and dropped from active setup to run plan

2720616 ciCacheGet(cv) models return nil when setting envSet 'conTypesOnDemand'

2719834 Netlisting must report errors for removed or renamed nport instances with S-parameter cell specification

2719662 Unable to run Spectre EMIR analysis from an OCEAN XL saved from Virtuoso ADE

2719407 Netlist syntax error is reported during fault generation

2718442 AMS UNL netlisting error in an AMS simulation run from a maestro cellview

2718126 Extract the desired signal from AC psf database

2718076 Auto Generator Hierarchy is enhanced to reuse cell methodology for custom cells

2717993 SKILL Lint rule for pcDefinePCell incorrectly informs about a global variable in the default parameter expression

2717840 Check in of a design managed schematic cellview incorrectly tries to make a maestro cellview read-only

2716018 Net Tracer warning message displayed regarding the attempt to create a layer

2715531 Wrong LPP chosen for the creation of VDR marker when voltage is negative

2715313 The Insert Filler Cells command does not respect the cellname filter specified in the row template

2714802 The Map Bus Name does not replace <> to []" when hnlMapNetInName is set in simrc

2714610 User-defined macros differ due to antenna diode related ground pin in a design

2714562 SpiceIn does not update port direction with pre-existing symbol when the Overwrite cellviews option is set to ALL

2713404 check_single_shape needs to gather sameMetalAlignedCut violations

2713171 Create new dataset causes existing datasets to be disabled

2712043 Incorrect related power pin extraction by Virtuoso Power Manager

2711344 Warning message displayed that techCreateLayer layer number 1150 already exists when adding a net trace

2708948 Remove the limit of 10K points in a single fault simulation run

2708663 Issue in isolation_enable_condition derivation utility

2708499 SiP-Design Rile Check (DRC) flow should not have dependency on the order of Virtuoso and SPB tools in the PATH environment variable

2706430 AutoVia is leading to sameMetalAlignedCuts violation

2706389 Netlist error is reported after the hierarchical copy of a library with a smart view

2706053 Error messages are reported when closing the layout window

2705719 Remove hspice view for rcwireload component in the Analog Library

2703677 Plot across Corners and Plot All not working for parameterized getAsciiWave

2698182 Router having issues with 3 and 4 terminal bus structures

2697590 Object layer-purpose pairs incorrectly removed from the Layers palette

2694797 Results of nested sweep pss-fd cannot be plotted in Virtuoso Visualization and Analysis XL using Calculator

2692670 Renaming or copying an EMX library does not complete the command successfully.

2692666 Results are not plotted in Virtuoso Visualization and Analysis XL using Calculator, but are plotted fine in the Results Browser

2688023 Renaming or copying an EMX library does not complete the command successfully

2684369 Neither upfront error checking nor calcVal lint check the correctness of the ?result argument

2683848 User-defined macros differ due to the pg function in a design

2683846 User-defined macros differ due to antenna diode related power pin in a design

2682917 Incorrect sorting of Pass/Fail values

2681402 VALE schematic migration: Schematic with off grid wiring created short on migrated schematic

2677663 DRD functionality does not recognize some of the layers listed in layout

2677457 The Link Graph feature does not work as expected when multiple axes limits are set manually

2677449 The Link Graph feature does not work as expected when multiple axes limits are set manually

2677436 The Link Graph feature does not work as expected when multiple axes limits are set manually

2677429 The Link Graph feature does not work as expected when multiple axes limits are set manually

2674226 Cannot process batch runs in parallel with implementation sets

2672998 AMS UNL netlisting issue due to a missing presistor instance

2662923 Users need to restart Virtuoso to make the eye diagram work

2648166 Area Estimator is enhanced to support i1278 flextor schematic Pcell

2627515 An incorrect error message is shown when corners are enabled in the run plan but disabled in Data View

2610969 VDR labels with different values created on same layer

2608305 Using VAR syntax in noise circle expression gives an error in ADE Assembler, works fine in ADE Explorer

2602408 LSCS job remains pending indefinitely for post-layout simulations across corners and certain output expressions

2600449 Renaming or copying an EMX library does not complete the command successfully

2578976 Changing the 'Common reference' setting in Property Editor form does not work as expected

2568872 Cannot change Stage pulldown to show stress simulation in Reliability Report view for age+she

2557411 Voltus-Fi: Violation Browser option is repeatedly selected and deselected and Virtuoso stops responding

2542276 Virtuoso stops unexpectedly while specifying Checks/Asserts options

2518102 Selecting one Max Resistance highlights all other Max Resistance paths in schematic

2481205 maeSetVar does not work for local variables when the current value is a sweep set

2477035 Design variable is not seen in Design Variables field in ADE Explorer after importing setup

2336033 Data View/Setup Assistant shows overridden errpreset for Spectre X, APS, and Spectre, misleading users

2009590 Virtuoso Visualization and Analysis XL exits unexpectedly when running simulations

1485721 The Running step Abstract form does not display the Overlap and Grid tabs

February 2023

The Cadence Virtuoso System Design Platform links two world-class Cadence technologies—custom IC design and package/PCB design/analysis—creating a holistic methodology that automates and streamlines the design and verification flow for multi-die heterogeneous systems. Leveraging the Virtuoso Schematic Editor and the Virtuoso Analog Design Environment, it provides a single platform for IC-and package/system-level design capture, analysis, and verification. In addition, the Virtuoso System Design Platform provides an automated bidirectional interface with the Cadence SiP-level implementation environment and Clarity 3d Solver. The Virtuoso System Design Platform allows IC designers to easily include system-level layout parasitics in the IC verification flow, enabling time savings by combining package/board layout connectivity data with the IC layout parasitic electrical model. The automatically generated “system-aware” schematic that results can then be easily used to create a testbench for final circuit-level simulation. The Virtuoso System Design Platform automates this entire flow, eliminating the highly manual and error-prone process of integrating system-level layout parasitic models back into the IC designer’s flow.

Cadence Virtuoso: Introduction

This video shows the basic introduction to one of the most used IC design tools in the industry and academia - Cadence virtuoso. It also shows how to edit schematic design in cadence virtuoso.

Cadence is a pivotal leader in electronic design and computational expertise, using its Intelligent System Design strategy to turn design concepts into reality. Cadence customers are the world’s most creative and innovative companies, delivering extraordinary electronic products from chips to boards to systems for the most dynamic market applications.

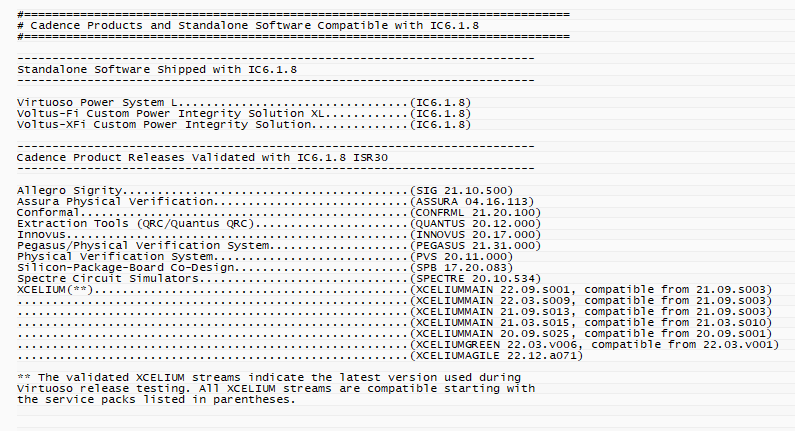

Product: Cadence Virtuoso

Version: IC6.1.8 ISR30

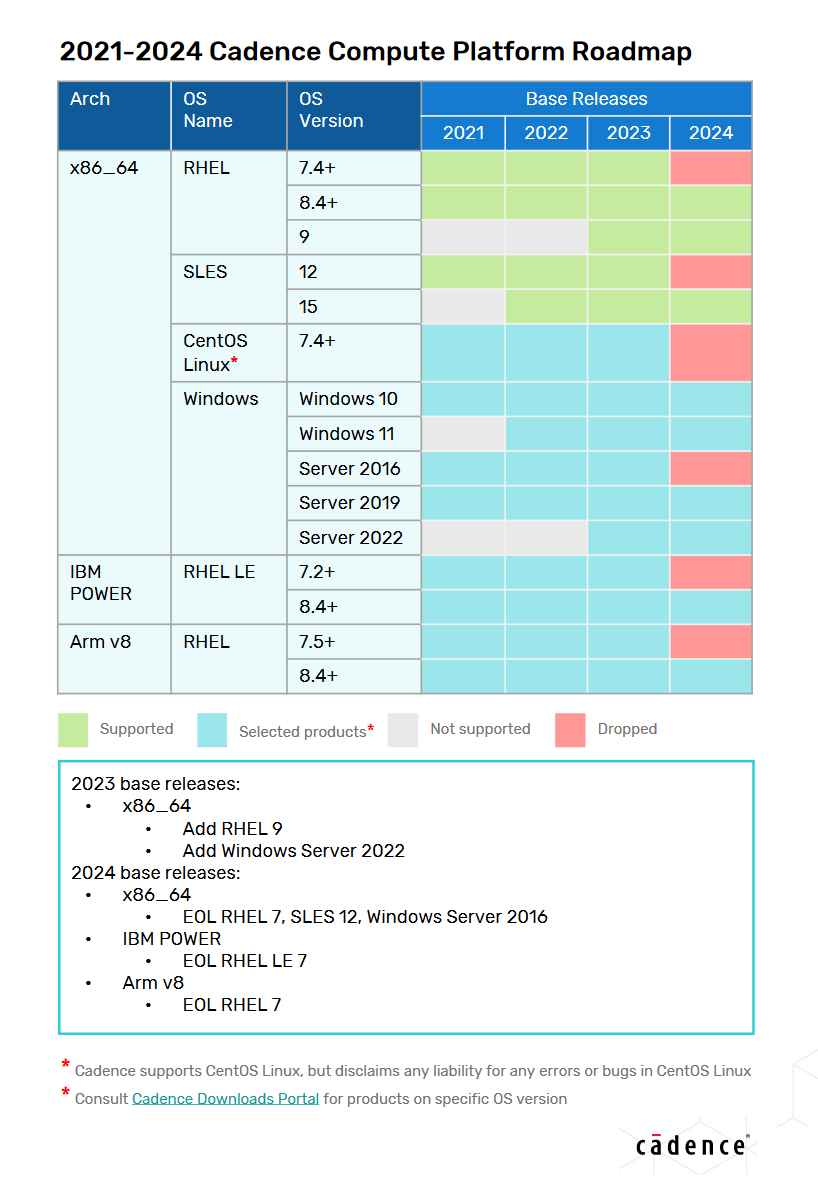

Supported Architectures: x86_64

Website Home Page : www.cadence.com

Languages Supported: english

System Requirements: Linux *

Size: 11.6 Gb

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please