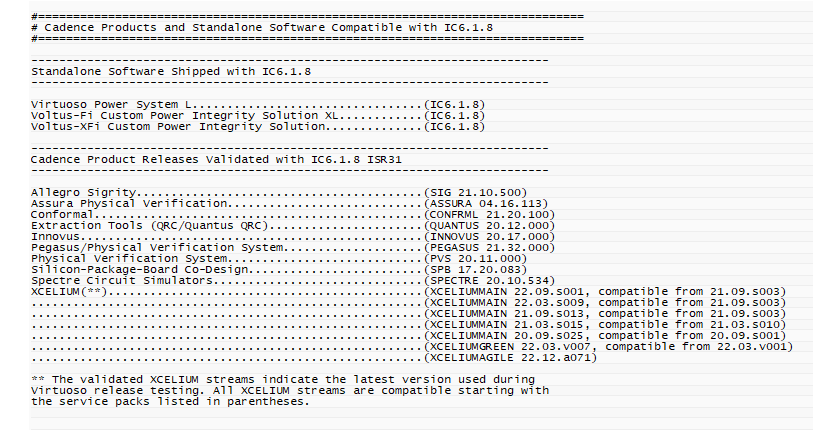

Cadence Virtuoso, Release Version IC6.1.8 ISR31 | 11.6 Gb

Cadence Design Systems, Inc. , the leader in global electronic design innovation, has unveiled Virtuoso, Release Version IC6.1.8 ISR31 (06.18.310) is a holistic, system-based solution that provides the functionality to drive simulation and LVS-clean layout of ICs and packages from a single schematic.

CCRs Fixed in IC6.1.8 and/or ICADVM20.1 ISR31 - Date: March 2023

2778577 Area Estimator throws parameter warning while estimating the area for the specified schematic

2772025 VerilogIn issues OpenSSL internal error on a FIPS-enabled machine

2768789 Aging simulations remains in pending state

2768317 Switch_pin not extracted correctly

2768052 FigGroup containing a multipart path and a pin is flattened when copied from one cellview to another

2767148 For minEndOfLineSpacing constraint, DRD flagging sameMask constraint violation for a diffMask

2766560 Abstract Generator exits unexpectedly because the Power Rails Analysis message exceeds the character limit imposed on the strings

2766080 Netlisting fails for Verilog-AMS cell that has 3 million pins

2765395 Spectre Monitor is not terminated and remains idle after exiting ADE Assembler

2764794 diffstbprobel_gnd netlists with incorrect probe syntax causes simulation errors

2763983 The Stress option is not available to select from the Stage drop-down list in the Reliability Report view

2763262 diffstbprobel_gnd netlists with incorrect probe syntax causes simulation errors

2762314 EAD LTE does not generate correct power values in Power Instance File for dummy devices in the child cell

2762172 Concurrent Layout fails to refresh data with SOS cache mode

2761760 When the Snap wires to snap pattern option is set but there is no WSP, the Create Bus command uses minSpacing

2761758 Virtuoso exits unexpectedly during an implementation run in Virtuoso ADE Verifier

2761394 Using Static EMIR analysis generates wrong statements

2760621 History results get overwritten when other histories are merged in it

2760437 Spectre monitor stays on the grid and uses 100% CPU after a simulation is stopped abruptly

2760422 The simulator log file is missing in a Monte Carlo simulation

2760377 Unable to read vertical marker information

2760000 Suspending jobs from command line and stopping them in GUI starts launching undesired simulation jobs

2759923 Create correct 45-degree slot edges when slotting 45-degree path segments

2759455 EMIR Analysis with SHE for a specific foundry performs unnecessary checks

2759452 LTE power file must check multiplier value and distribute power accordingly

2759185 Simulation fails when suspended LSCS jobs are restarted in ADE Assembler

2758926 Coloring conflict occurs in the Pin Accessibility Checker when uncolored extended pin view is used by the router

2758686 An error occurs when running stability analysis with diffstbprobel_gnd

2758500 Running an AMS simulation in ADE Explorer gives the error 'sh: cdsDiff: command not found' in the terminal

2757556 FuSa report cannot be generated

2757421 Results tab does not display the updated values when alternate data sets are loaded

2757102 Avoid message boxes when running simulations from ADE Verifier in non-GUI mode

2756835 Spectre output displays unnecessary device information due to the wrong netlisting of the DC option 'where'

2756814 Virtuoso exits unexpectedly when batch mode simulation is stopped using the Stop button on the main toolbar

2756763 Using AMS UNL with ADE Explorer gives the error 'sh: cdsDiff: command not found'

2755379 Exclude Types setting does not work appropriately for the Routability Check command when invoked from the Wire Assistant

2755038 Wire Editing with allowedJogWidths creates jogs with wrong mask color

2754238 Virtuoso exits unexpectedly when recreating a Pcell

2753874 In ICRP mode, the calcVal function in the Monte Carlo simulation pulls a value from an incorrect point

2753067 Error occurs during AMS reliability simulation when using the Configure Stress File option

2752756 When running the FGR chop command, the Contact Space value resets to a different value in latest Virtuoso version versus IC6.1.8 ISR16

2752636 Virtuoso stops unexpectedly when running a run plan

2751961 Cannot open the Axis Properties form for y axis again after changing the axis properties in a certain way

2750903 Virtuoso Power Manager could not run due to issue in UPF syntax

2750781 In some cases, LSCS does not show all the commands in the context-sensitive menu to view log files

2749554 If a cell name of a testbench starts with a numeric character, the waveform is not plotted

2749549 An analog2digital expression sent to ADE Assembler returns incorrect results

2749406 The Auto-Create Pins tool failed to create pins for the specified net shapes when run in Schematic Aware mode

2749364 Virtuoso exits unexpectedly when flipping objects with a large number of vertices in a layout

2749317 Symbol compression fails after adjustment

2749205 Wrong parameter calculation of FGR in latest Virtuoso version versus IC6.1.8 ISR16.

2749198 The View Implementation command in Virtuoso ADE Verifier does not work for remote or batch runs with LSF

2749008 Virtuoso exits unexpectedly when extracting a layout with a non-uniquified module hierarchy

2748480 Noise separation not working with selected instances

2747944 The Monte Carlo setup form does not accept dumpseed as an additional option in the Netlist Options field

2747890 Need an environment variable to globally disable quick plot data

2747806 Need an environment variable to disable quick plot data for all implementation used in Virtuoso ADE Verifier

2747564 Number of points submitted for simulation do not match the points selected in Run Preview

2747420 Passing pPar for model of analogLib cap causes OSSHNL-305 conflict error in AMS UNL netlister

2747346 Netlist creation fails in LSCS when a ternary conditional operator is used to set the temperature

2746344 The TDDB result view is disabled when using the LSCS method for job distribution

2744493 Saving the symbol view causes Virtuoso to become unresponsive

2743667 Models from the ahdlLib and rfLib libraries report errors when amsLibCompile is used

2743236 Virtuoso exits unexpectedly when dbSave() is applied to Virtuoso Layout Editor

2741895 Cannot set reference edge for quick align inside preselected instances with an overlapping text drawing rectangle

2741419 When using a transient dynamic parameter, a previously removed design variable reappears

2741189 A bus created with analog2digital using awvCreateBus has an incorrect expression when sent to ADE Assembler

2740308 The Quick Plot command does not plot all waveforms

2740008 Checker shows the wrong minEndOfLineSpacing reference when multiple rules are specified

2739509 Cannot plot graphs for stress simulation when the Save Intermediate Results option is set to either None or Some

2738775 List of instance IDs not passed to vcpfeRegisterPostPlacementProc when boundary=rowRegion

2738710 Scaling is not effective for HPR metal extraction

2737643 Batch checker reports pin spacing violation due to NetClass spacings similar to IC6.1.7

2737394 ADE Explorer does not generate correct netlist with postlpreset and postlnets using Constraint Manager

2737074 Incorrect netlist is generated for Verilog-A views when hnlUseSchematicForInherittedConnection is enabled in the. simrc file

2736966 ADE Verifier is creating more jobs than the max limit when implementation runs are started incrementally

2736853 DEF Out cannot export information related to ROUTEHALO

2736568 Save signal statement is missing in the netlist when running simulation with the config view in EAD

2735316 Isolation modeling issue

2734753 Support generic parser in the custom self-heating effects (SHE) flow

2734410 A disabled tcl file is lost after saving a maestro view or running a simulation

2732409 Incorrect netlist generated when using the 'Generate noise' option with mtline analog library model

2730456 Not able to edit points of cutting boundary in the GUI

2728990 Abstract Generator does not work as expected in ICADVM20.1 ISR28 during power rail analysis due to segmentation fault error

2728760 Cannot save signals with the selected mode when the design with a period in the library name is simulated

2728317 Cannot select the desired edge as the reference for quick align when another overlapping edge is present

2727130 Simulation schematic generation incorrect when ports are overlapping

2725823 Feedback loop issue

2725108 Unable to complete a DRC clean route with a single horizontal M1 wire between the two pins and involves additional routing layers

2723970 Cannot plot the S-parameters when the specified mode for S-parameter analysis is 'other'

2722420 Auto P&R fill is leaving gaps and moving devices

2721251 Abstract Generator exits unexpectedly in the abstract step during power rail analysis

2720085 abeLayerAvoid produces incorrect results

2719728 Pin size and layer changed for Pcell instances after assisted export

2719721 A bus created with analog2digital using awvCreateBus has an incorrect expression when sent to ADE Assembler

2719456 The View Netlist command in the context-sensitive menu of results is not enabled for a fault simulation

2718009 Library import could not be completed

2717594 In Virtuoso ADE Verifier reference flow, simulation run reports an error when the parent requirement is editable, but the child is non-editable

2717270 The selection mechanism of the Pin Tool user interface needs to be enhanced for better usability

2715840 calcVal arguments ?cornerName and ?matchParams are not working correctly together

2715648 The ?ignoreParams argument of calcVal set to rest interferes with a Monte Carlo simulation

2715371 Unable to infer antenna diode related power pin for flat and user-defined macros

2714607 User-defined macro differs in a design by voltage_name

2714604 User-defined macro differs in a design by direction

2714601 User-defined macro differs in a design by pg_type

2714599 User-defined macro differs in a design by power_down_function

2714595 User-defined macro differs in a design by related power pin

2714453 Via Property Editor displays the wrong metal layer for backside BV0 via

2706619 Calibration over corners fails due to brackets around calcVal expression

2697957 The waveform icon appears in results although the expression has an error

2691288 Load markNetOptions from a base technology file when the ITDB technology file references the base technology file

2683849 User-defined macro differs in a design by switch function

2674873 Getting an xmelab RNGDIR error on using the simrc variable simVerilogBusJustificationStr or hnlSetBusDirectionDescending

2669632 Using the View Results shortcut command for an implementation opens the maestro cellview in modified state and shows the Save prompt when the cellview is closed

2665041 Need read-only histories to come along when a maestro view is copied

2648334 Virtuoso keeps exiting unexpectedly when doing various layout tasks such as moving objects and editing cells in place

2643096 Improper connectivity handling when modifying a pathSeg in Layout EXL with EAD Browser active

2642126 Clean up the relationship between the ?matchParams and ?cornerName arguments of calcVal

2632551 Verilog Netlister generates an incorrect netlist when multi-dimensional buses are used in the schematic

2632171 Net tracer traces a net from package down to IC but cannot trace it back up to the package

2631266 The Library Property Editor form is displayed behind the Library Manager in RHEL 7.9

2622318 Metal short resistor Pcell - Need to twice generate as schematic for Pcell to get evaluated correctly

2615346 GUI does not reflect what is netlisted when using pnoise sampled if Change is not clicked

2598190 Image export operation removes some layers

2590166 Virtuoso SystemVerilog Netlister creates an incompatible netlist that fails when running simulation

2590108 pnoise sampled fails when not clicking Change after Enable/disable on Choose Analysis form

2576818 Impedance plots are not correctly plotted when loading a graph window from a .grf file

2551832 In the referenced flow, changes made in maestro views are updated correctly in referenced cellviews using AutoSync, but not propagated to the top Verifier cellview

2520514 After the Re-run Unfinished Points command is used in LSCS mode, the context-sensitive menu of results is like ICRP

2498198 The maestro cellview setup disappears after a run plan run is stopped by lint checks

2494147 An analog2digital expression sent to ADE Assembler returns incorrect results

2472344 When Area estimator is run and the design contains iterated instances, the iterated instances become scalarized and as a result the schematic is modified

2259631 Incorrect points are taken when specifying variables through the 'Add Specific Points' option for AC analysis

2182536 Using plotting template when there are no results to be plotted causes Virtuoso to exit unexpectedly

2162370 A bus created from analog2digital results in an incorrect expression when sent to ADE Assembler

2155201 The Save a Copy command does not work for read-only histories in ADE Assembler

2046842 Provide better ways to access the Spectre log for a fault simulation

2043783 Provide better ways to access netlist, job log, and Spectre output for a fault simulation

1888640 The Save a Copy command does not work for read-only histories in ADE Assembler

1778962 Any change to the Resolution field in the Save Image form is not honored

March 2023

2772025 VerilogIn issues OpenSSL internal error on a FIPS-enabled machine

2768789 Aging simulations remains in pending state

2768317 Switch_pin not extracted correctly

2768052 FigGroup containing a multipart path and a pin is flattened when copied from one cellview to another

2767148 For minEndOfLineSpacing constraint, DRD flagging sameMask constraint violation for a diffMask

2766560 Abstract Generator exits unexpectedly because the Power Rails Analysis message exceeds the character limit imposed on the strings

2766080 Netlisting fails for Verilog-AMS cell that has 3 million pins

2765395 Spectre Monitor is not terminated and remains idle after exiting ADE Assembler

2764794 diffstbprobel_gnd netlists with incorrect probe syntax causes simulation errors

2763983 The Stress option is not available to select from the Stage drop-down list in the Reliability Report view

2763262 diffstbprobel_gnd netlists with incorrect probe syntax causes simulation errors

2762314 EAD LTE does not generate correct power values in Power Instance File for dummy devices in the child cell

2762172 Concurrent Layout fails to refresh data with SOS cache mode

2761760 When the Snap wires to snap pattern option is set but there is no WSP, the Create Bus command uses minSpacing

2761758 Virtuoso exits unexpectedly during an implementation run in Virtuoso ADE Verifier

2761394 Using Static EMIR analysis generates wrong statements

2760621 History results get overwritten when other histories are merged in it

2760437 Spectre monitor stays on the grid and uses 100% CPU after a simulation is stopped abruptly

2760422 The simulator log file is missing in a Monte Carlo simulation

2760377 Unable to read vertical marker information

2760000 Suspending jobs from command line and stopping them in GUI starts launching undesired simulation jobs

2759923 Create correct 45-degree slot edges when slotting 45-degree path segments

2759455 EMIR Analysis with SHE for a specific foundry performs unnecessary checks

2759452 LTE power file must check multiplier value and distribute power accordingly

2759185 Simulation fails when suspended LSCS jobs are restarted in ADE Assembler

2758926 Coloring conflict occurs in the Pin Accessibility Checker when uncolored extended pin view is used by the router

2758686 An error occurs when running stability analysis with diffstbprobel_gnd

2758500 Running an AMS simulation in ADE Explorer gives the error 'sh: cdsDiff: command not found' in the terminal

2757556 FuSa report cannot be generated

2757421 Results tab does not display the updated values when alternate data sets are loaded

2757102 Avoid message boxes when running simulations from ADE Verifier in non-GUI mode

2756835 Spectre output displays unnecessary device information due to the wrong netlisting of the DC option 'where'

2756814 Virtuoso exits unexpectedly when batch mode simulation is stopped using the Stop button on the main toolbar

2756763 Using AMS UNL with ADE Explorer gives the error 'sh: cdsDiff: command not found'

2755379 Exclude Types setting does not work appropriately for the Routability Check command when invoked from the Wire Assistant

2755038 Wire Editing with allowedJogWidths creates jogs with wrong mask color

2754238 Virtuoso exits unexpectedly when recreating a Pcell

2753874 In ICRP mode, the calcVal function in the Monte Carlo simulation pulls a value from an incorrect point

2753067 Error occurs during AMS reliability simulation when using the Configure Stress File option

2752756 When running the FGR chop command, the Contact Space value resets to a different value in latest Virtuoso version versus IC6.1.8 ISR16

2752636 Virtuoso stops unexpectedly when running a run plan

2751961 Cannot open the Axis Properties form for y axis again after changing the axis properties in a certain way

2750903 Virtuoso Power Manager could not run due to issue in UPF syntax

2750781 In some cases, LSCS does not show all the commands in the context-sensitive menu to view log files

2749554 If a cell name of a testbench starts with a numeric character, the waveform is not plotted

2749549 An analog2digital expression sent to ADE Assembler returns incorrect results

2749406 The Auto-Create Pins tool failed to create pins for the specified net shapes when run in Schematic Aware mode

2749364 Virtuoso exits unexpectedly when flipping objects with a large number of vertices in a layout

2749317 Symbol compression fails after adjustment

2749205 Wrong parameter calculation of FGR in latest Virtuoso version versus IC6.1.8 ISR16.

2749198 The View Implementation command in Virtuoso ADE Verifier does not work for remote or batch runs with LSF

2749008 Virtuoso exits unexpectedly when extracting a layout with a non-uniquified module hierarchy

2748480 Noise separation not working with selected instances

2747944 The Monte Carlo setup form does not accept dumpseed as an additional option in the Netlist Options field

2747890 Need an environment variable to globally disable quick plot data

2747806 Need an environment variable to disable quick plot data for all implementation used in Virtuoso ADE Verifier

2747564 Number of points submitted for simulation do not match the points selected in Run Preview

2747420 Passing pPar for model of analogLib cap causes OSSHNL-305 conflict error in AMS UNL netlister

2747346 Netlist creation fails in LSCS when a ternary conditional operator is used to set the temperature

2746344 The TDDB result view is disabled when using the LSCS method for job distribution

2744493 Saving the symbol view causes Virtuoso to become unresponsive

2743667 Models from the ahdlLib and rfLib libraries report errors when amsLibCompile is used

2743236 Virtuoso exits unexpectedly when dbSave() is applied to Virtuoso Layout Editor

2741895 Cannot set reference edge for quick align inside preselected instances with an overlapping text drawing rectangle

2741419 When using a transient dynamic parameter, a previously removed design variable reappears

2741189 A bus created with analog2digital using awvCreateBus has an incorrect expression when sent to ADE Assembler

2740308 The Quick Plot command does not plot all waveforms

2740008 Checker shows the wrong minEndOfLineSpacing reference when multiple rules are specified

2739509 Cannot plot graphs for stress simulation when the Save Intermediate Results option is set to either None or Some

2738775 List of instance IDs not passed to vcpfeRegisterPostPlacementProc when boundary=rowRegion

2738710 Scaling is not effective for HPR metal extraction

2737643 Batch checker reports pin spacing violation due to NetClass spacings similar to IC6.1.7

2737394 ADE Explorer does not generate correct netlist with postlpreset and postlnets using Constraint Manager

2737074 Incorrect netlist is generated for Verilog-A views when hnlUseSchematicForInherittedConnection is enabled in the. simrc file

2736966 ADE Verifier is creating more jobs than the max limit when implementation runs are started incrementally

2736853 DEF Out cannot export information related to ROUTEHALO

2736568 Save signal statement is missing in the netlist when running simulation with the config view in EAD

2735316 Isolation modeling issue

2734753 Support generic parser in the custom self-heating effects (SHE) flow

2734410 A disabled tcl file is lost after saving a maestro view or running a simulation

2732409 Incorrect netlist generated when using the 'Generate noise' option with mtline analog library model

2730456 Not able to edit points of cutting boundary in the GUI

2728990 Abstract Generator does not work as expected in ICADVM20.1 ISR28 during power rail analysis due to segmentation fault error

2728760 Cannot save signals with the selected mode when the design with a period in the library name is simulated

2728317 Cannot select the desired edge as the reference for quick align when another overlapping edge is present

2727130 Simulation schematic generation incorrect when ports are overlapping

2725823 Feedback loop issue

2725108 Unable to complete a DRC clean route with a single horizontal M1 wire between the two pins and involves additional routing layers

2723970 Cannot plot the S-parameters when the specified mode for S-parameter analysis is 'other'

2722420 Auto P&R fill is leaving gaps and moving devices

2721251 Abstract Generator exits unexpectedly in the abstract step during power rail analysis

2720085 abeLayerAvoid produces incorrect results

2719728 Pin size and layer changed for Pcell instances after assisted export

2719721 A bus created with analog2digital using awvCreateBus has an incorrect expression when sent to ADE Assembler

2719456 The View Netlist command in the context-sensitive menu of results is not enabled for a fault simulation

2718009 Library import could not be completed

2717594 In Virtuoso ADE Verifier reference flow, simulation run reports an error when the parent requirement is editable, but the child is non-editable

2717270 The selection mechanism of the Pin Tool user interface needs to be enhanced for better usability

2715840 calcVal arguments ?cornerName and ?matchParams are not working correctly together

2715648 The ?ignoreParams argument of calcVal set to rest interferes with a Monte Carlo simulation

2715371 Unable to infer antenna diode related power pin for flat and user-defined macros

2714607 User-defined macro differs in a design by voltage_name

2714604 User-defined macro differs in a design by direction

2714601 User-defined macro differs in a design by pg_type

2714599 User-defined macro differs in a design by power_down_function

2714595 User-defined macro differs in a design by related power pin

2714453 Via Property Editor displays the wrong metal layer for backside BV0 via

2706619 Calibration over corners fails due to brackets around calcVal expression

2697957 The waveform icon appears in results although the expression has an error

2691288 Load markNetOptions from a base technology file when the ITDB technology file references the base technology file

2683849 User-defined macro differs in a design by switch function

2674873 Getting an xmelab RNGDIR error on using the simrc variable simVerilogBusJustificationStr or hnlSetBusDirectionDescending

2669632 Using the View Results shortcut command for an implementation opens the maestro cellview in modified state and shows the Save prompt when the cellview is closed

2665041 Need read-only histories to come along when a maestro view is copied

2648334 Virtuoso keeps exiting unexpectedly when doing various layout tasks such as moving objects and editing cells in place

2643096 Improper connectivity handling when modifying a pathSeg in Layout EXL with EAD Browser active

2642126 Clean up the relationship between the ?matchParams and ?cornerName arguments of calcVal

2632551 Verilog Netlister generates an incorrect netlist when multi-dimensional buses are used in the schematic

2632171 Net tracer traces a net from package down to IC but cannot trace it back up to the package

2631266 The Library Property Editor form is displayed behind the Library Manager in RHEL 7.9

2622318 Metal short resistor Pcell - Need to twice generate as schematic for Pcell to get evaluated correctly

2615346 GUI does not reflect what is netlisted when using pnoise sampled if Change is not clicked

2598190 Image export operation removes some layers

2590166 Virtuoso SystemVerilog Netlister creates an incompatible netlist that fails when running simulation

2590108 pnoise sampled fails when not clicking Change after Enable/disable on Choose Analysis form

2576818 Impedance plots are not correctly plotted when loading a graph window from a .grf file

2551832 In the referenced flow, changes made in maestro views are updated correctly in referenced cellviews using AutoSync, but not propagated to the top Verifier cellview

2520514 After the Re-run Unfinished Points command is used in LSCS mode, the context-sensitive menu of results is like ICRP

2498198 The maestro cellview setup disappears after a run plan run is stopped by lint checks

2494147 An analog2digital expression sent to ADE Assembler returns incorrect results

2472344 When Area estimator is run and the design contains iterated instances, the iterated instances become scalarized and as a result the schematic is modified

2259631 Incorrect points are taken when specifying variables through the 'Add Specific Points' option for AC analysis

2182536 Using plotting template when there are no results to be plotted causes Virtuoso to exit unexpectedly

2162370 A bus created from analog2digital results in an incorrect expression when sent to ADE Assembler

2155201 The Save a Copy command does not work for read-only histories in ADE Assembler

2046842 Provide better ways to access the Spectre log for a fault simulation

2043783 Provide better ways to access netlist, job log, and Spectre output for a fault simulation

1888640 The Save a Copy command does not work for read-only histories in ADE Assembler

1778962 Any change to the Resolution field in the Save Image form is not honored

March 2023

The Cadence Virtuoso System Design Platform links two world-class Cadence technologies—custom IC design and package/PCB design/analysis—creating a holistic methodology that automates and streamlines the design and verification flow for multi-die heterogeneous systems. Leveraging the Virtuoso Schematic Editor and the Virtuoso Analog Design Environment, it provides a single platform for IC-and package/system-level design capture, analysis, and verification. In addition, the Virtuoso System Design Platform provides an automated bidirectional interface with the Cadence SiP-level implementation environment and Clarity 3d Solver. The Virtuoso System Design Platform allows IC designers to easily include system-level layout parasitics in the IC verification flow, enabling time savings by combining package/board layout connectivity data with the IC layout parasitic electrical model. The automatically generated “system-aware” schematic that results can then be easily used to create a testbench for final circuit-level simulation. The Virtuoso System Design Platform automates this entire flow, eliminating the highly manual and error-prone process of integrating system-level layout parasitic models back into the IC designer’s flow.

Cadence Virtuoso: Introduction

This video shows the basic introduction to one of the most used IC design tools in the industry and academia - Cadence virtuoso. It also shows how to edit schematic design in cadence virtuoso.

Cadence is a pivotal leader in electronic design and computational expertise, using its Intelligent System Design strategy to turn design concepts into reality. Cadence customers are the world’s most creative and innovative companies, delivering extraordinary electronic products from chips to boards to systems for the most dynamic market applications.

Product: Cadence Virtuoso

Version: IC6.1.8 ISR31 (06.18.310) hotfix

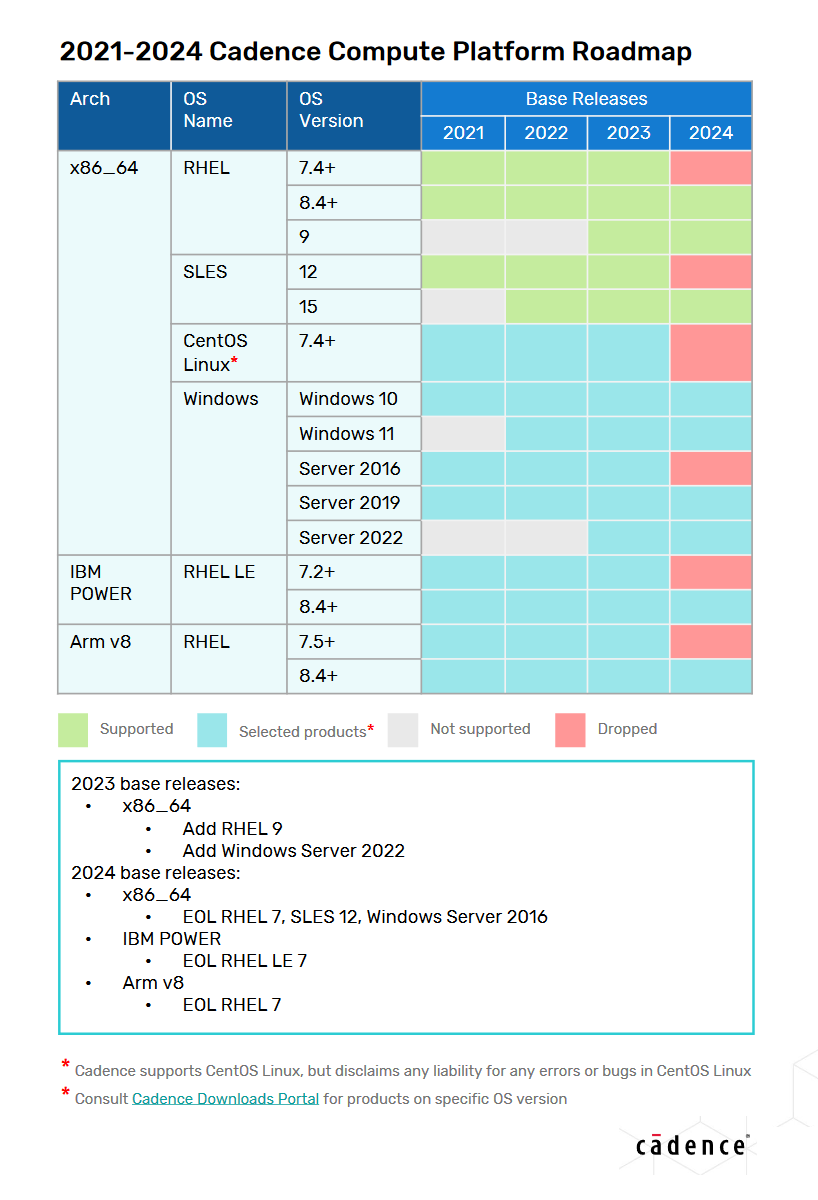

Supported Architectures: x86_64

Website Home Page : www.cadence.com

Languages Supported: english

System Requirements: Linux *

Size: 11.6 Gb

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please