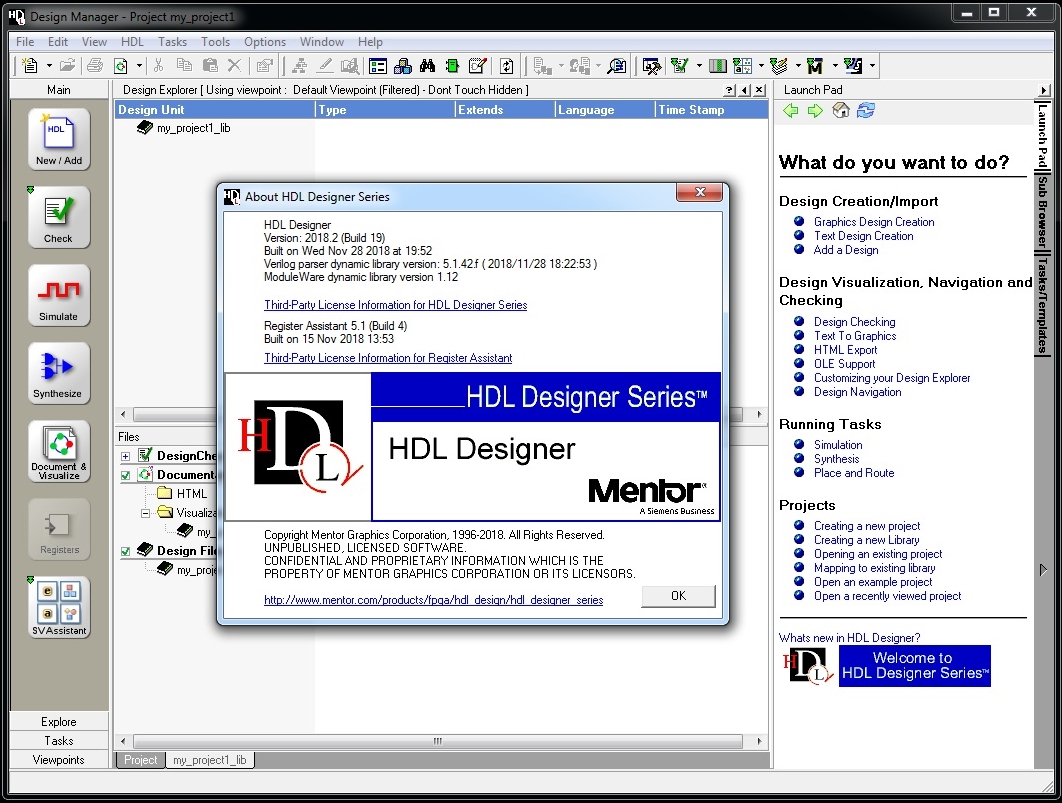

Mentor Graphics HDL Designer Series (HDS) 2018.2 | 832.3 mb

Mentor Graphics Corp. introduced the HDL Designer Series (HDS) 2018.2, a family of point tools for complex Verilog, VHDL, or mixed-language design.

What’s New in HDL Designer Series 2018.2 - December 2018:

Summary

HDL Designer

— Microsemi Libero Integration

— ModuleWare library enhancement

. Enhanced VHDL package support for selected ModuleWare components

SVAssistant

— Compilation flow speedup; 6x faster

— Performance improvements

— Advanced templates for “Extend This Class”

. Can include template files within template project e.g. SV_class.svt

— Several parser enhancements

— Java 8 upgrade

— Eclipse Neon 4.6.3 and CDT 9.2.1 upgrade

DesignChecker

— Capacity improvement

. Memory footprint optimization; reduced up to 50% measured on selected customer designs

— Batch flow enhancements

. Auto detection of design unit names in the hierarchy in basic batch flow

. Re-run analysis from UI after loading batch results database

— DesignChecker base rules help is now integrated with InfoHub

— Several parser enhancements

Register Assistant

— RTL Verilog pipelining support

— Java 8 upgrade

— Eclipse Neon 4.6.3

Quality

— >70 Defects & Enhancements Resolved

Note: For details on these new features and enhancements, refer to the manual .pdf files available from the Help menu in each module or from the Manuals folder on your hard drive.

Refer to the list of issues and enhancements that have been addressed in the 2018.2 release.

HDL Designer Series

DR 900086 Request to support integration with Actel® Libero.

DR 1147472 Request to fix broken links between the FPGA Technology Setup and Precision Synthesis Prepare Data dialog boxes with Precision 2015.1.

DR 1220365 Request to support changing the language of components backwards in the Design Unit view.

DR 1236062 Request to enhance the integration between HDS and MicroSemi to support SmartFusion SoC flow.

DR 1242714 Request to support integration with new Actel devices.

DR 1247713 Request to fix links in Algorithmic State Machines (ASM) to work correctly without generation errors.

DR 1248855 Request to support importing MicroSemi Libero IPs.

DR 1262965 Request to fix a crash that occurs on saving a Verilog module that has a missing module port and “input” in uppercase.

DR 1294682 Request to enhance the DesignChecker documentation to clarify the API commands supported in the DesignChecker independent batch mode versus the DesignChecker-HDS batch flow.

DR 1302587 Request to fix an error raised on adding files to a SystemVerilog-VHDL Assistant project.

DR 1310688 Request to support instantiating an encrypted Verilog IP on a block diagram.

DR 1312714 Request to fix an example in the DesignChecker API Reference Manual.

DR 1313442 Request to enhance the documentation of the Name Spaces base rule.

DR 1316728 Request to fix an issue in which it is not possible to exit the Add Existing Design dialog box, when the project directory is read-only, expect by ending the HDL Designer Series process.

DR 1316785 Request to fix a crash that occurs on importing a specific design.

DR 1323514 Request to fix the high CPU usage resulting from starting SystemVerilog-VHDL Assistant from HDL Designer Series.

DR 1325278 Request to fix the behavior of cross-referencing to “when” and “elsif” generate statements.

DR 1328683 Request to support expanding the internal variable %unit in Questa flow when using Verilog.

DR 1329657 Request to fix an issue in which the predefined attribute `last_event raises a generation error when used on indexed array record elements.

DR 1330912 Request to fix a DesignChecker hang that occurs on using an empty “Case generate” choice.

DR 1331548 Request to fix the internal variables %(SourceDir), %(HDSDir), and %(HDLDir) on Windows.

DR 1338694 Request to run Questa simulation flow in batch mode without user intervention.

DR 1350367 Request to enable the MicroSemi Libero/Designer task to support Verilog .v and .vm files.

DR 1350372 Request to import encrypted Verilog files created using Libero into HDS.

DesignChecker

DR 1059971 Request to preserve indexes in vectors, instead of elaborating them, when creating missing components.

DR 1127001 Request to fix a false synthesis error that DesignChecker raises when using Generics in an assignment.

DR 1193607 Request to fix an issue in which DesignChecker is auto-generating invalid VHDL for a missing component.

DR 1257863 Request to fix the behavior of the Exceptions parameter in the Statement Style base rule.

DR 1303214 Request to support re-running DesignChecker in GUI (Graphical User Interface) mode after loading results.

DR 1303576 Request to fix a crash that occurs on using the runAnalysis API command with files existing in a read-only directory.

DR 1318885 Request to run DesignChecker design unit level checking without the need to specify all design units.

DR 1320095 Request to fix cross-referencing from a checked file in the Checked Files/Design Units tab to its source file when using relative paths.

DR 1322664 Request to fix the importFromQuesta API command to enable importing from Questa designs having Unisims.

DR 1323259 Request to isolate the content of exported reports from the content of generated .tbc files.

DR 1324607 Request to fix an invalid syntax error reported by DesignChecker when the dialect is set as VHDL 2008.

DR 1329126 Request to integrate the documentation of the DesignChecker base rules into the InfoHub.

DR 1329205 Request to fix the DesignChecker Help menu to open the User Guide and API Reference Manual menu items correctly on Linux.

DR 1329578 Request to fix a parser error raised on using VHDL 2008 with DesignChecker.

DR 1329711 Request to support relative paths in the global constraints file.

DR 1330177 Request to enable saving the DesignChecker results file when the violations produced are only syntax errors.

DR 1330489 Request to fix the Export Combined Report feature to create the output directory or raise an error message if the directory does not exist.

DR 1331830 Request to fix the violation tree to expand correctly when setting an exclusion in the DesignChecker GUI.

DR 1332260 Request to fix the documentation of the addFile API command in the DesignChecker API Reference Manual.

DR 1332569 Request to fix an issue in which the Import From Questa operation fails when file names and design unit names contain special characters.

DR 1332570 Request to fix the Missing Declarations feature to support extended identifiers to ensure that generated files open correctly.

DR 1332671 Request to fix an issue in which applying the setBlackBox API command to a file that was not imported using the importFromQuesta API command results in false syntax errors and reduced performance.

DR 1333318 Request to fix the documentation of the policySettings API command in the DesignChecker API Reference Manual.

DR 1333320 Request to add examples for some API commands in the DesignChecker API Reference Manual.

DR 1333355 Request to provide complete and correct information when using the loadResults API command to load a .tbc file while the global constraints file is set.

DR 1334192 Request to enable the HTML results file to show only column headers when there are no violations reported.

DR 1334198 Request to improve the formatting of DesignChecker’s HTML results file to be able to view the file correctly in Microsoft® Excel®.

DR 1334394 Request to enhance the policySettings API command to support the full path of configured rules.

DR 1334408 Request to support adding justification comments through the policySettings API command.

DR 1336901 Request to fix a deep analysis failure that occurs on analyzing a design containing a VHDL incomplete type.

DR 1340677 Request to enhance the documentation of the projectSettings API command.

SystemVerilog-VHDL Assistant

DR 1316799 Request to fix a crash that occurs on running “Import From Questa” for a specific test case.

DR 1330653 Request to fix an error raised on invoking SystemVerilog-VHDL Assistant 2018.1 for the first time.

DR 1335084 Request to fix a parser error that SystemVerilog-VHDL Assistant raises for a valid SystemVerilog file.

DR 1336553 Request to fix the Go To feature to navigate to the architecture instead of the configuration in case of “for … use configuration”.

DR 1336571 Request to fix the Go To feature to navigate to the correct design unit in case of “for others : … use entity”.

DR 1337156 Request to make the behavior of Go To > Design Unit and Go To > Binding Aspect consistent in a specific test case.

DR 1342973 Request to fix a syntax error that SystemVerilog-VHDL Assistant reports in a package.

DR 1346115 Request to fix an issue in which SystemVerilog-VHDL Assistant does not parse a valid VHDL file.

Register Assistant

The following issues and enhancement requests have been addressed in the Register Assistant 5.1 release:

DR 1147317 Request to fix an incorrect internal signal name that Register Assistant uses in generation when the input contains RTL parameters referencing an undefined block.

DR 1291650 Request to show the About dialog box on Windows.

DR 1298569 Request to fix an issue in which using the VHDL attribute “length” in Field Condition and Field Action generates an incorrect input port named “length”.

DR 1339518 Request to fix an existing Register Assistant example.

DR 1343583 Request to enable multiple reserved fields in the same register to share the same name.

HDL Designer Series

DR 900086 Request to support integration with Actel® Libero.

DR 1147472 Request to fix broken links between the FPGA Technology Setup and Precision Synthesis Prepare Data dialog boxes with Precision 2015.1.

DR 1220365 Request to support changing the language of components backwards in the Design Unit view.

DR 1236062 Request to enhance the integration between HDS and MicroSemi to support SmartFusion SoC flow.

DR 1242714 Request to support integration with new Actel devices.

DR 1247713 Request to fix links in Algorithmic State Machines (ASM) to work correctly without generation errors.

DR 1248855 Request to support importing MicroSemi Libero IPs.

DR 1262965 Request to fix a crash that occurs on saving a Verilog module that has a missing module port and “input” in uppercase.

DR 1294682 Request to enhance the DesignChecker documentation to clarify the API commands supported in the DesignChecker independent batch mode versus the DesignChecker-HDS batch flow.

DR 1302587 Request to fix an error raised on adding files to a SystemVerilog-VHDL Assistant project.

DR 1310688 Request to support instantiating an encrypted Verilog IP on a block diagram.

DR 1312714 Request to fix an example in the DesignChecker API Reference Manual.

DR 1313442 Request to enhance the documentation of the Name Spaces base rule.

DR 1316728 Request to fix an issue in which it is not possible to exit the Add Existing Design dialog box, when the project directory is read-only, expect by ending the HDL Designer Series process.

DR 1316785 Request to fix a crash that occurs on importing a specific design.

DR 1323514 Request to fix the high CPU usage resulting from starting SystemVerilog-VHDL Assistant from HDL Designer Series.

DR 1325278 Request to fix the behavior of cross-referencing to “when” and “elsif” generate statements.

DR 1328683 Request to support expanding the internal variable %unit in Questa flow when using Verilog.

DR 1329657 Request to fix an issue in which the predefined attribute `last_event raises a generation error when used on indexed array record elements.

DR 1330912 Request to fix a DesignChecker hang that occurs on using an empty “Case generate” choice.

DR 1331548 Request to fix the internal variables %(SourceDir), %(HDSDir), and %(HDLDir) on Windows.

DR 1338694 Request to run Questa simulation flow in batch mode without user intervention.

DR 1350367 Request to enable the MicroSemi Libero/Designer task to support Verilog .v and .vm files.

DR 1350372 Request to import encrypted Verilog files created using Libero into HDS.

DesignChecker

DR 1059971 Request to preserve indexes in vectors, instead of elaborating them, when creating missing components.

DR 1127001 Request to fix a false synthesis error that DesignChecker raises when using Generics in an assignment.

DR 1193607 Request to fix an issue in which DesignChecker is auto-generating invalid VHDL for a missing component.

DR 1257863 Request to fix the behavior of the Exceptions parameter in the Statement Style base rule.

DR 1303214 Request to support re-running DesignChecker in GUI (Graphical User Interface) mode after loading results.

DR 1303576 Request to fix a crash that occurs on using the runAnalysis API command with files existing in a read-only directory.

DR 1318885 Request to run DesignChecker design unit level checking without the need to specify all design units.

DR 1320095 Request to fix cross-referencing from a checked file in the Checked Files/Design Units tab to its source file when using relative paths.

DR 1322664 Request to fix the importFromQuesta API command to enable importing from Questa designs having Unisims.

DR 1323259 Request to isolate the content of exported reports from the content of generated .tbc files.

DR 1324607 Request to fix an invalid syntax error reported by DesignChecker when the dialect is set as VHDL 2008.

DR 1329126 Request to integrate the documentation of the DesignChecker base rules into the InfoHub.

DR 1329205 Request to fix the DesignChecker Help menu to open the User Guide and API Reference Manual menu items correctly on Linux.

DR 1329578 Request to fix a parser error raised on using VHDL 2008 with DesignChecker.

DR 1329711 Request to support relative paths in the global constraints file.

DR 1330177 Request to enable saving the DesignChecker results file when the violations produced are only syntax errors.

DR 1330489 Request to fix the Export Combined Report feature to create the output directory or raise an error message if the directory does not exist.

DR 1331830 Request to fix the violation tree to expand correctly when setting an exclusion in the DesignChecker GUI.

DR 1332260 Request to fix the documentation of the addFile API command in the DesignChecker API Reference Manual.

DR 1332569 Request to fix an issue in which the Import From Questa operation fails when file names and design unit names contain special characters.

DR 1332570 Request to fix the Missing Declarations feature to support extended identifiers to ensure that generated files open correctly.

DR 1332671 Request to fix an issue in which applying the setBlackBox API command to a file that was not imported using the importFromQuesta API command results in false syntax errors and reduced performance.

DR 1333318 Request to fix the documentation of the policySettings API command in the DesignChecker API Reference Manual.

DR 1333320 Request to add examples for some API commands in the DesignChecker API Reference Manual.

DR 1333355 Request to provide complete and correct information when using the loadResults API command to load a .tbc file while the global constraints file is set.

DR 1334192 Request to enable the HTML results file to show only column headers when there are no violations reported.

DR 1334198 Request to improve the formatting of DesignChecker’s HTML results file to be able to view the file correctly in Microsoft® Excel®.

DR 1334394 Request to enhance the policySettings API command to support the full path of configured rules.

DR 1334408 Request to support adding justification comments through the policySettings API command.

DR 1336901 Request to fix a deep analysis failure that occurs on analyzing a design containing a VHDL incomplete type.

DR 1340677 Request to enhance the documentation of the projectSettings API command.

SystemVerilog-VHDL Assistant

DR 1316799 Request to fix a crash that occurs on running “Import From Questa” for a specific test case.

DR 1330653 Request to fix an error raised on invoking SystemVerilog-VHDL Assistant 2018.1 for the first time.

DR 1335084 Request to fix a parser error that SystemVerilog-VHDL Assistant raises for a valid SystemVerilog file.

DR 1336553 Request to fix the Go To feature to navigate to the architecture instead of the configuration in case of “for … use configuration”.

DR 1336571 Request to fix the Go To feature to navigate to the correct design unit in case of “for others : … use entity”.

DR 1337156 Request to make the behavior of Go To > Design Unit and Go To > Binding Aspect consistent in a specific test case.

DR 1342973 Request to fix a syntax error that SystemVerilog-VHDL Assistant reports in a package.

DR 1346115 Request to fix an issue in which SystemVerilog-VHDL Assistant does not parse a valid VHDL file.

Register Assistant

The following issues and enhancement requests have been addressed in the Register Assistant 5.1 release:

DR 1147317 Request to fix an incorrect internal signal name that Register Assistant uses in generation when the input contains RTL parameters referencing an undefined block.

DR 1291650 Request to show the About dialog box on Windows.

DR 1298569 Request to fix an issue in which using the VHDL attribute “length” in Field Condition and Field Action generates an incorrect input port named “length”.

DR 1339518 Request to fix an existing Register Assistant example.

DR 1343583 Request to enable multiple reserved fields in the same register to share the same name.

About HDL Designer Series (HDS). HDL Designer Series products cover aspects of the design entry and management process: HDL Pilot for design management; HDL Detective for design analysis; HDL Author for text and graphical editing and documentation; and HDL Designer for complete point tool functionality in a single solution, the company said.

The suite combines technologies of the Mentor Graphics Renoir HDL graphical entry tool with technology acquired from Escalade.

HDL Pilot provides a common cockpit from which all design data can be managed, making it easy to transfer design data within a common reuse environment, the company said. Its interface allows designers to navigate through and manage project data generated in complex Verilog, VHDL, and mixed-language designs processes.

HDL Detective simplifies documentation creation and maintenance at every step of the FPGA, ASIC, and SOC design cycle, featuring a push-button process for reusing legacy or commercial IP designs. Designers can use HDL Detective to visualize the current state of a design and generate documentation for newly developed HDL. This process translates HDL to diagrammatic representations.

HDL Author allows design teams to create complex systems. To accommodate the fullest range of design preferences, HDL Author is available in three flavors for designers using pure HDL source code, graphical representations, or a combination of both.

HDL Author Text features Interface Based Design (IBD') to solve the interconnect creation problem, the company said. IBD is a patent-pending concept in text-based entry that simplifies interconnect creation problems by displaying design interconnect structures in an easy-to-view and compact tabular format. This tabular editing environment allows designers to capture a given level of hierarchy piece by piece, simplifying the creation and documentation process.

HDL Designer is a complete entry and management solution that includes all the point tools of the HDL Designer Series, the ocompany said. It allows companies to standardize on a toolset that can be used to share designs across multiple locations, improving and enhancing communication, design reuse and documentation company-wide, according to the company.

About Mentor Graphics. Mentor Graphics Corporation is a world leader in electronic hardware and software design solutions, providing products, consulting services and award-winning support for the worlds most successful electronic, semiconductor and systems companies. Established in 1981, the company reported revenues in the last fiscal year in excess of $1.15 billion. Corporate headquarters are located at 8005 S.W. Boeckman Road, Wilsonville, Oregon 97070-7777.

Product: Mentor Graphics HDL Designer Series (HDS)

Version: 2018.2 build 19

Supported Architectures: x64

Website Home Page : www.mentor.com

Language: english

System Requirements: PC

Supported Operating Systems: Windows 7even or 10

Size: 832.3 mb

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please