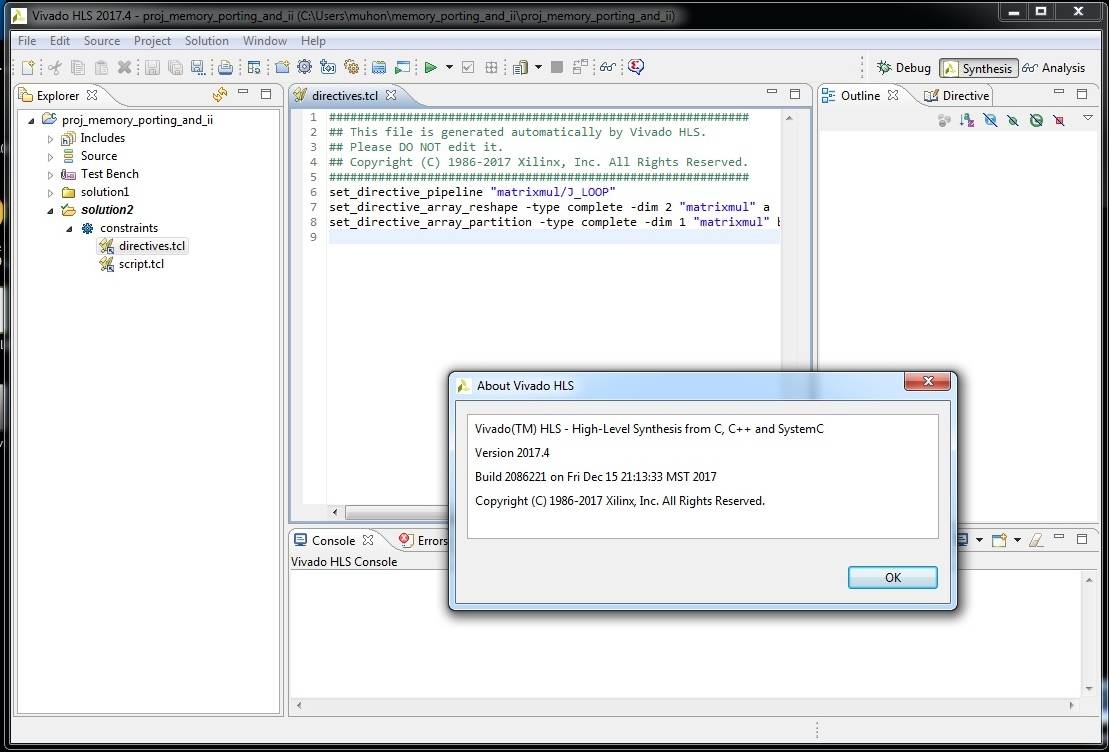

Xilinx Vivado Design Suite HLx Editions 2017.4 | 17.0 Gb

Xilinx has released Xilinx Vivado Design Suite HLx Editions 2017.4. This release introduces Model Composer, a new Model-based Design tool to enable rapid design exploration within the MathWorks Simulink environment and accelerate the path to production on Xilinx All Programmable Devices through automatic code generation.

Release Notes 2017.4 - What's new:

Vivado Design Suite 2017.4 introduces Model Composer, a new Model-based Design tool to enable rapid design exploration within the MathWorks Simulink environment and accelerate the path to production on Xilinx All Programmable Devices through automatic code generation. Model Composer is an add-on tool to all the Vivado editions.

The following Devices and features are also updated in this release.

Device Support

The following devices are in production:

- Zynq UltraScale+ MPSoC:

XCZU4EV/CG/EG (-1, -2)

XCZU19EG (-1L, 2L)

XCZU7EV/CG/EG (-1,-2)

XCZU5EV/CG/EG (-1, 2)

- Kintex UltraScale+:

XCKU5P (-1L, -2L)

XCKU15P (-1L,-2L)

- Artix-7 and Spartan-7

XC7S25 (-1, -2, -1LI)

XC7A25T(-1,-2, -2LE (1.0V))

XC7A12T(-1, 2, -2LE (1.0V))

Vivado Tools

System Generator for DSP

- Supported MATLAB Versions: R2016a, R2016b, R2017a and R2017b.

- Single-port RAM, Dual-port RAM, ROM, FIFO and AXI-FIFO blocks updated to use new Block Memory Generator and FIFO Generator IPs.

- Enhancements to Error Messaging for all high-level System Generator for DSP blocks with AXI interface.

Vivado HLS

- New methodology design rule check section in the GUI to point to potential design enhancements.

- Improved tool messages for DATAFLOW optimizations.

- Optimized math.h functions for fixed arithmetic data types.

Simulation Flows and Verification IP

- Verify UltraScale+ MPSoC PL and PS AXI interactions with the new MPSoC Verification IP.

Model Composer

- High-level of Abstraction: Algorithm-centric bocks and support for vectors and 2D matrices enables frame-based algorithm design that saves you the time and effort to move to an intermediate low-level model for implementation.

- Performance-optimized Block Libraries: Computer Vision(xfOpenCV), Math, and Linear Algebra libraries available as blocks for design and simulation of algorithms within Simulink’s graphical environment.

- Custom User-Imported Blocks: Ability to import HLS synthesizable C/C++ code as custom blocks, providing greater flexibility to design your differentiated algorithms and leverage automatic test bench generation from test cases in simulation.

- Automatic Code Generation: Automatic optimizations steer towards a micro-architecture that meets target performance. You can synthesize your algorithm into 3 Export types: Packaged RTL IP, System Generator for DSP IP and Vivado HLS synthesizable code.

- Supported MATLAB Versions: R2016a, R2016b, R2017a and R2017b.

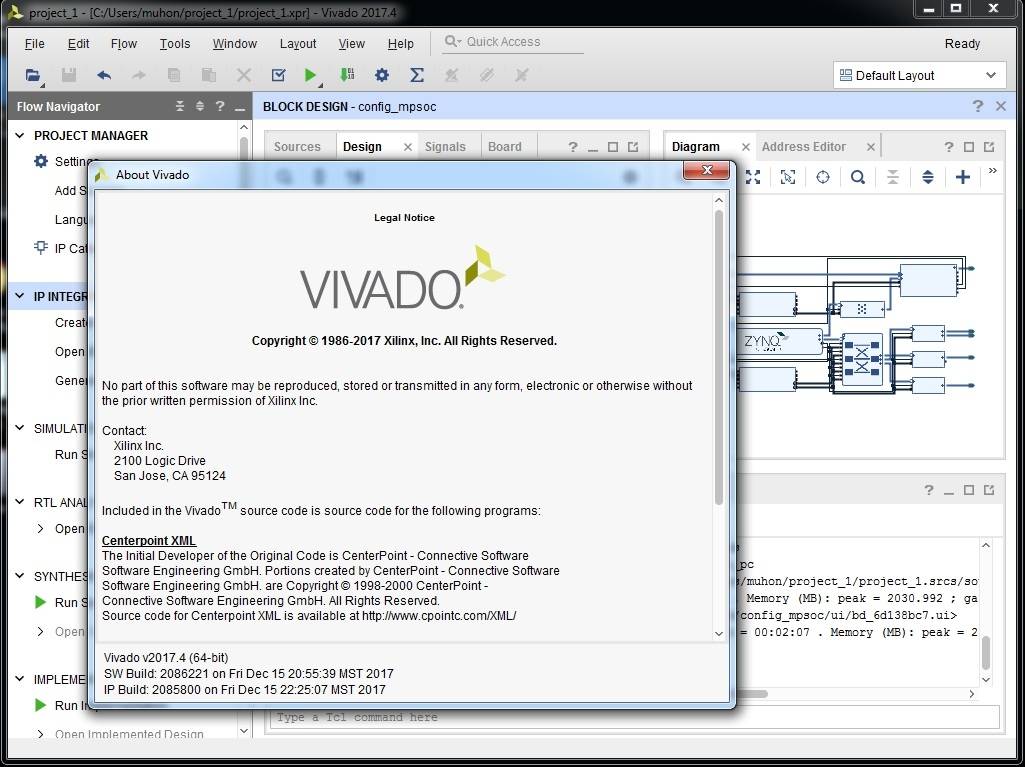

About Xilinx Vivado Design Suite. Vivado Design Suite is a software suite produced by Xilinx for synthesis and analysis of HDL designs, superseding Xilinx ISE with additional features for system on a chip development and high-level synthesis. Vivado represents a ground-up rewrite and re-thinking of the entire design flow (compared to ISE), and has been described by reviewers as "well conceived, tightly integrated, blazing fast, scalable, maintainable, and intuitive".

Unlike ISE which relied on ModelSim for simulation, the Vivado System Edition includes an in-built logic simulator. Vivado also introduces high-level synthesis, with a toolchain that converts C code into programmable logic. Vivado has been described as a "state-of-the-art comprehensive EDA tool with all the latest bells and whistles in terms of data model, integration, algorithms, and performance".

In 2013, Xilinx completed a 1000 person-year development of its Vivado Design Suite, replacing the 15-year old ISE.

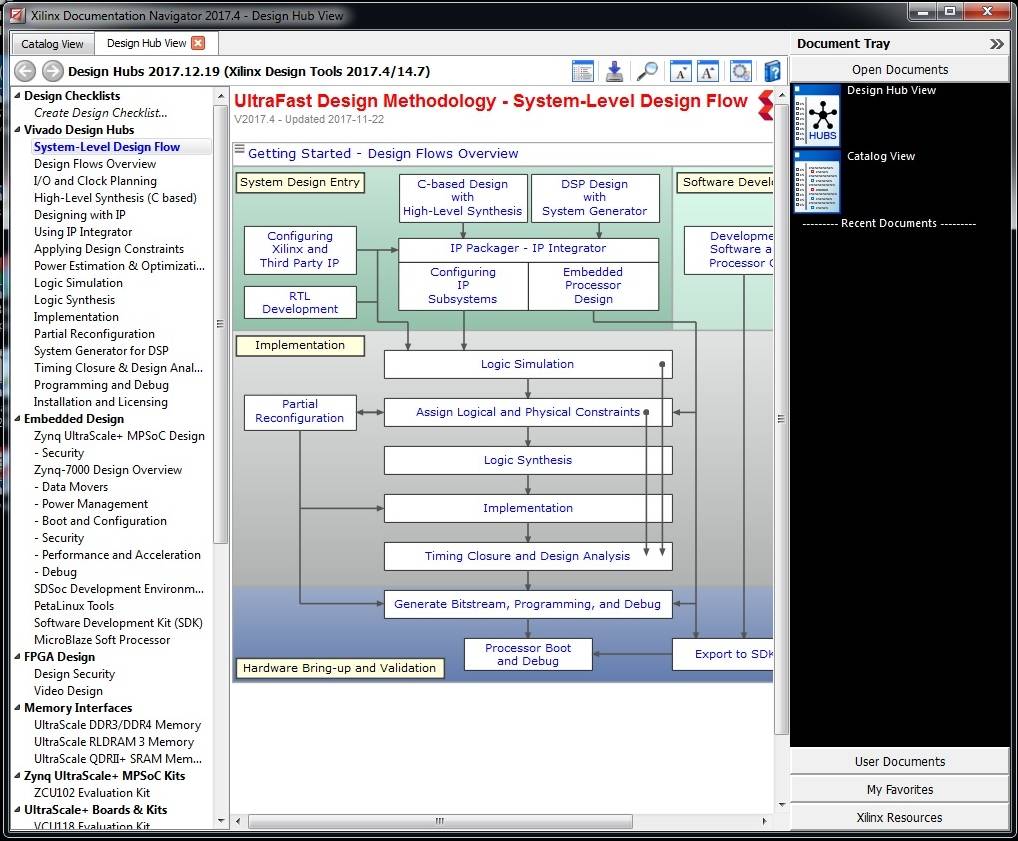

About Xilinx Vivado Design Suite HLx Editions. Vivado Design Suite HLx Editions include Partial Reconfiguration at no additional cost with the Vivado HL Design Edition and HL System Edition. In-warranty users can regenerate their licenses to gain access to this feature. Partial Reconfiguration is available for Vivado WebPACK edition at a reduced price.

The new HLx editions supply design teams with the tools and methodology needed to leverage C-based design and optimized reuse, IP sub-system reuse, integration automation and accelerated design closure. When coupled with the UltraFast High-Level Productivity Design Methodology Guide, this unique combination is proven to accelerate productivity by enabling designers to work at a high level of abstraction while facilitating design reuse.

About Xilinx. Xilinx is the leading provider of All Programmable FPGAs, SoCs, MPSoCs, and 3D ICs. Xilinx uniquely enables applications that are both software defined and hardware optimized – powering industry advancements in Cloud Computing, SDN/NFV, Video/Vision, Industrial IoT, and 5G Wireless.

Product: Xilinx Vivado Design Suite

Version: 2017.4 HLx Editions .ISO

Supported Architectures: x64

Website Home Page : www.xilinx.com

Language: english

System Requirements: PC / Linux

Supported Operating Systems: *

Size: 17.0 Gb

*

Microsoft Windows Support

- Windows 7 SP1 Professional (64bit), English/Japanese.

- Windows 10 Professional Creators Update (64bit), English/Japanese.

Linux Support

- Red Hat Enterprise Workstation/Server 7.2 and 7.3 (64bit)

- Red Hat Enterprise Workstation 6.6, 6.7, 6.8, and 6.9 (64bit)

- SUSE Linux Enterprise 11.4 and 12.2 (64bit)

- Cent OS 7.2 and 7.3 (64bit)

- Cent OS 6.7, 6.8, and 6.9 (64bit)

- Ubuntu Linux 16.04.2 LTS (64bit)

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration and the volume for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration and the volume for the restoration

No mirrors please