Cadence SPB Allegro and OrCAD 17.40.000-2022 HF031 | 7.3 Gb

Cadence Design Systems, Inc. , the leader in global electronic design innovation, has unveiled a new of improvements in hot fix 031 to the Cadence SPB Allegro and OrCAD 17.40 families of products aimed at boosting performance and productivity through improvements features and big fixed issues.

Cadence OrCAD and Allegro: What’s New in 17.40.031-2022 - Date: 08-05-2022

=====================================================================================

CCRID Product ProductLevel2 Title

==============================================================================================

2650304 ADV_PKG_ROUTER OTHER Auto connect fails to connect to existing routes

2649097 ADW LIB_FLOW Mechanical PTF with subtype set to ! does not produce a correctly generated EDM part_table.ptf

2672048 ADW PART_MANAGER Unable to access libraries from Pulse intermittently with no known sequence of reproducible steps

2621627 ALLEGROX FLOORPLANNER System Capture crashes when board is opened in Allegro PCB Editor and viewer

2647514 ALLEGRO_EDITOR COLOR Productize Shape Visibility through Color/Visibility dialog

2531489 ALLEGRO_EDITOR CROSS_SECTION Issue in Cross-section filter: Cannot see Dielectric without enabling Dielectric and Die Stack in Available Filter

2550355 ALLEGRO_EDITOR CROSS_SECTION Stackup/xsection image export has unreadable text

2655430 ALLEGRO_EDITOR DATABASE Replacing the padstack requires manual purge

2660920 ALLEGRO_EDITOR DATABASE axlImportXmlDBRecords() changes the default color settings

2664465 ALLEGRO_EDITOR DATABASE Replaced padstacks are not purged automatically in release 17.4-2019

2649764 ALLEGRO_EDITOR DFM DFM soldermask sliver calculation not considering vias being inside pad for DRC generation

2651702 ALLEGRO_EDITOR DFM DFM Same net uvia hole to uvia hole creates false DRCs if via is mirrored

2628597 ALLEGRO_EDITOR DRC_CONSTR The result of "Filter text

2651680 ALLEGRO_EDITOR GRAPHICS Allegro PCB Editor, release 17.4-2019 Infinite Cursor white ghost text issue: White text box attached to cursor

2660378 ALLEGRO_EDITOR GRAPHICS Release 17.4-2019 GPU plugin opacity issue on assigning color to symbol: Copper feature invisible within shape

2667883 ALLEGRO_EDITOR GRAPHICS GPU: Visibility of filled rectangles are different from shapes

2667953 ALLEGRO_EDITOR GRAPHICS Glitched cursor when configuring "Infinite Cursor"

2649703 ALLEGRO_EDITOR INTERACTIV Replace Via with Structure overlaps routes and corrupts database when structure is on right side of vertical structure

2647087 ALLEGRO_EDITOR IN_DESIGN_ANA Net Name in Vision Control dialog table not reported when a through device is used.

2647821 ALLEGRO_EDITOR IN_DESIGN_ANA Layers enabled in visibility tab are reset after IR drop is re-simulated.

2580540 ALLEGRO_EDITOR MCAD_COLLAB 'idxHolePadstackMapping.txt' file is not considered when "Select All" is selected in IDX Flow Manager Import form

2664925 ALLEGRO_EDITOR MODULES Place > Manual - Module definition crashes the tool

2665480 ALLEGRO_EDITOR MODULES The program crashes when running the Fab Panelization tool command

2660874 ALLEGRO_EDITOR MULTI_USER Error regarding undefined function - axlMUIsMultiUser on using SKILL file

2648344 ALLEGRO_EDITOR OTHER Import Logo needs to be revised such that the bmp can be put on ANY class/subclass a user chooses

2662652 ALLEGRO_EDITOR OTHER Degree circle in dimension will not move with degree.

2489008 ALLEGRO_EDITOR PLACEMENT Symbol text overlaps components on refreshing after rotating a placed module

2615648 ALLEGRO_EDITOR PLACEMENT Ratsnest visibility not same in release 17.4-2019 and release 17.2-2016 of Allegro PCB Editor

2640507 ALLEGRO_EDITOR PLACEMENT Ratsnest not displayed in Place Components Manually in release 17.4-2019

2681593 ALLEGRO_EDITOR PLACEMENT Ratsnet not displayed in Place Components Manually in release 17.4-2019

2681645 ALLEGRO_EDITOR PLACEMENT Ratsnests do not appear when placing components manually

2599650 ALLEGRO_EDITOR PORTING WM_COPYDATA not working in release 17.4-2019

2653527 ALLEGRO_EDITOR PORTING WM_COPYDATA is not working in release 17.4-2019

2666117 ALLEGRO_EDITOR PORTING Allegro PCB Editor does not respond to WM_COPYDATA(SendMessage) messages in release 17.4-2019

2646063 ALLEGRO_EDITOR SHAPE Min Aperture for gap width does not seem to work for the attached board

2647991 ALLEGRO_EDITOR SHAPE Teardrop close to boundary causes incorrect evaluation of Shape

2642367 ALLEGRO_EDITOR TECHFILE Difference report cannot be generated when importing .tcf file

2607638 ALLEGRO_EDITOR UI_FORMS "IDF Out Filter Setup" window small and not resizable

2645229 ALLEGRO_EDITOR UI_FORMS Searching the word 'step' in the User Preferences Editor crashes Allegro PCB Editor

2652396 ALLEGRO_EDITOR UI_FORMS idfout_filter.form enhancement request: Cannot resize

2659362 ALLEGRO_EDITOR UI_FORMS PCB Editor is crashing on searching for "Step" in User Preferences

2668427 ALLEGRO_EDITOR UI_FORMS Searching the word 'step' in the User Preferences Editor crashes Allegro PCB Editor

2658226 ALLEGRO_EDITOR UI_GENERAL Bug in Find panel with OrCAD Sigrity ERC license: Display -> Windows does not display the panel

2629652 APD CROSS_SECTION Cross-section Editor changes material when clicking on material name

2649896 APD DATABASE Redundant cline to dangling Cline

2657279 APD DEGASSING Strange (AREF) shape degassing: Hole created along shape boundary and degassing has opposite tone

2664829 APD DRC_CONSTRAIN Minimum Aperture For Gap Width is not honored

2665732 APD DRC_CONSTRAIN No DRCs reported when CSet is assigned to layer sets

2628970 APD EDIT_ETCH Route > Daisy Chain fails to connect neighboring pins in certain cases

2650356 APD GRAPHICS GPU: Opening design takes up to 4 minutes when GPU is active

2647547 APD REPORTS Stacked Via Report fails with error message regarding incompatible data

2642730 APD WLP WLP: pin replacement fails to have the corresponding pin extension

2650718 APD WLP WLP: ripped up structures unexpectedly come back

2657264 APD WLP Application stops responding on doing Advance Metal Fill with a specific metal fill clearance value

2666773 APD WLP Power Delivery Rail Via Generator generates columns and rows as X-1 vs input values

2662590 CONCEPT_HDL CAEVIEWS Compilation error for Caeviews HDL on Windows in release 17.4-2019

2568360 CONSTRAINT_MGR UI_FORMS Toolbar should report "not fully routed" for unrouted net when hovering over yellow Actual/Margin cells - Rel Prop Delay

2626371 CONSTRAINT_MGR UI_FORMS Double-clicking the column header sorts the column

2027407 ORBITIO GUI Interface popup list not sorted alphabetically in Select Interface form

2656144 ORBITIO GUI System Planner error message not clear when display is not set

2646990 ORBITIO INTEGRITY_IF Bump locations go wrong after push_to_planner without "-reset" option

2650662 ORBITIO IO_FLOORPLAN Check order does not work if a comment is put in TermNumber

2651329 ORBITIO IO_FLOORPLAN Select icon in IO Info Table should redraw main GUI

2653383 ORBITIO IO_FLOORPLAN Check Order should describe correct Integrity-3DIC version instead of OrbitIO version

2641279 ORBITIO OTHER Data in IO Info Table is cleared by create_contacts command

2540463 PCB_LIBRARIAN SYMBOL_EDITOR Zoom Fit is not working in Symbol Editor when opening the table view.

2672315 PCB_LIBRARIAN SYMBOL_EDITOR Pin number and pintext position not following directives on new symbols in new Symbol Editor

2655194 PSPICE ENVIRONMENT Inherit profile is broken if a large dat file is present in source profile

2488221 PSPICE MODELEDITOR Model Editor cannot open history files and displays a crash message though there is no crash

2663981 PSPICE MODELEDITOR PSpice DMI Generic VCVS C/C++ template code does not compile

2351036 PSPICE SIMULATOR Incorrect simulation results when using parameter expressions with curly braces

2527511 PSPICE SIMULATOR Error (ORPSIM-16550) displayed regarding floating point computation failure during matrix solution

2636922 PSPICE SIMULATOR Error message of DEBUG option is incorrect

2570534 PSPICE TI_OUT_OF_CON Encrypted model behaves differently

2671311 PULSE ADHOC Random System Capture Crash resulted in lost data

2663716 PULSE CORE Unexplained Pulse server outage after 99 days uptime

2649745 PULSE LIBDB_PART_UI Typo in the template for Capacitors -> Polarized Capacitor

2630240 PULSE R2PLM-WC PFM fails to publish the BOM and/or variants with 'Publish partially failed' Error.

2547586 PULSE R2PLM If one variant utility fails, all parent variant objects show failure even with successful children

2667227 PULSE R2PLM Wrong item number assigned to variant BOM when publishing PFM

2671661 PULSE R2PLM Variant details are not appearing correctly during Publish to Manufacturing

2654607 PULSE USER_MANAGEME SSO (Identity Provider) Authentication fails for restored Vista backup

2581093 RF_PCB ROUTING Allegro RF PCB 'Add connect' adds only single segment and reports SKILL error on adding RF traces with corners

2648227 RF_PCB SETUP Error reported when doing RF-PCB>Setup

2575729 SIP_LAYOUT DATABASE Netlist error on importing SIP file

2675767 SYSTEM_CAPTURE COMPONENT_BRO System Capture annotates injected properties on adding or replacing components in HotFix 030

2471089 SYSTEM_CAPTURE CONSTRAINT_MA Property defined by user as read only in CM is editable in CM docked

2640904 SYSTEM_CAPTURE EXPORT_PCB Zero pin mechanical components get assigned duplicate reference designators

2644139 SYSTEM_CAPTURE EXPORT_PCB Copy pasting the symbol (part_line_item) does not assign a unique reference designator

2518595 SYSTEM_CAPTURE FIND_REPLACE Changing symbol version of placed part does not update the text associated with the part

2664942 SYSTEM_CAPTURE FIND_REPLACE Relative property position is not retained on switching symbol version in System Capture

2648020 SYSTEM_CAPTURE HSS_SYMBOLEDI DSCS-1 port pin mismatch violation cannot be resolved

2656076 SYSTEM_CAPTURE IFF_IMPORT IFF import in System Capture gives faulty schematic

2513965 SYSTEM_CAPTURE IMPORT_BLOCK DE-HDL callout files not transferred during System Capture conversion

2595410 SYSTEM_CAPTURE IMPORT_BLOCK System Capture CopyAs giving incorrect results

2605425 SYSTEM_CAPTURE IMPORT_BLOCK "File > Copy Project As" does not use the new design name

2658886 SYSTEM_CAPTURE IMPORT_BLOCK TOC symbol coming from DE-HDL not getting detected and deleted

2684108 SYSTEM_CAPTURE IMPORT_BLOCK converting a DE-HDL project creates an empty folder.

2656295 SYSTEM_CAPTURE IMPORT_DEHDL_ Japanese Notes in page border of DE-HDL get garbled in System Capture

2608156 SYSTEM_CAPTURE MENUS_AND_TOO Save and Save As are greyed out in the File menu

2657604 SYSTEM_CAPTURE MENUS_AND_TOO 'Save All' has to be used as 'Save' and 'Save As' are greyed in the File menu

2554984 SYSTEM_CAPTURE NEW_PROJECT Warning detected if relative path is used in PPT directive for referring ptf file

2515523 SYSTEM_CAPTURE NOTES Need to validate Notes input for illegal characters

2627769 SYSTEM_CAPTURE PACKAGER Changing reuse instance name of block with Top changes all instance names

2634086 SYSTEM_CAPTURE PACKAGER System Capture does not give error when two-package symbol is placed three times

2634514 SYSTEM_CAPTURE PART_MANAGER Unable to sync the parts from Part Manager

2466085 SYSTEM_CAPTURE PROPERTY_EDIT System Capture: Cannot add VOLTAGE property to signal

2601899 SYSTEM_CAPTURE PROPERTY_EDIT System Capture differentiates between 0V and 0 V

2654098 SYSTEM_CAPTURE PROPERTY_EDIT Alignment/Superscript/Subscript warning appears when setting default text attributes for properties

2637910 SYSTEM_CAPTURE REPLACE The replace component when executed from the find results does not show selected component information

2585561 SYSTEM_CAPTURE REPORTS ::sdaReports::netToCompList from command line encounters error

2654088 SYSTEM_CAPTURE SMART_PDF Print to SmartPDF treated as change to design for Save

2602467 SYSTEM_CAPTURE SPECIAL SYMBO Special Symbols placing the wrong symbol when selected

2604331 SYSTEM_CAPTURE TABLE Headers are wrapped in autofit tables in System Capture

2659496 SYSTEM_CAPTURE TABLE MMB panning does not work when cursor is inside a table

2662418 SYSTEM_CAPTURE TABLE Allow copying read-only text in System Capture

2522067 SYSTEM_CAPTURE TABLE_OF_CONT TOC color/style is reset on running 'reevaluateTOC'

2501880 SYSTEM_CAPTURE UI The image aspect ratio gets altered even though it is locked

2545967 SYSTEM_CAPTURE UI Properties are moved on toggling visibility

2613795 SYSTEM_CAPTURE UI System Capture window changes display size after running the syscap command.

2640195 SYSTEM_CAPTURE UI Mouse pointer not visible in dark/black theme under certain selections

2653029 SYSTEM_CAPTURE UI Changing the visibility of a property value causes it to change position.

2673056 SYSTEM_CAPTURE UI Tcl API incorrectly interacting with the page navigation widget in HotFix 030

2495455 SYSTEM_CAPTURE WIRING Adding wire into bus shifts the text off the line.

2608920 SYSTEM_CAPTURE WIRING Net names duplicated on copying circuit with visible system generated net names

2673797 SYSTEM_CAPTURE WIRING Unable to delete symbol or connect NC symbol to existing pins

2654698 SYSTEM_CAPTURE WORKSPACE Floating panels have to be reopened every time System Capture is started

2572529 SYSTEM_DESIGN SDE_SUBSYSTEM EXTERNAL_ALLEGRO_BOARD_FOLDER does not resolve ^design_name^

2581309 SYS_RELIABILITY DEVICE_CONFIG Stress Analysis ignores dual diodes in System Capture

2651502 SYS_RELIABILITY DEVICE_CONFIG BAV99 diode is not categorized a diode in stress analysis

2617090 SYS_RELIABILITY ELEC_STRESS_D Red chart bar of Stress Analysis disappears when clicked

2640940 SYS_RELIABILITY SCH_AUDIT_SET Schematic Audit CPM setting in SITE being overwritten by default

2652248 TOPXP ALLEGRO_INTEG View topology error for nets names with the special character "." in Aurora II

2664988 TOPXP CHANNEL_SIMUL Topology Workbench gives incorrect DDR channel simulation results for sinusoidal jitter of 150MHz

2652331 TOPXP SYSTEMSI Topology Workbench sub-circuit cannot read dollar sign

CCRID Product ProductLevel2 Title

==============================================================================================

2650304 ADV_PKG_ROUTER OTHER Auto connect fails to connect to existing routes

2649097 ADW LIB_FLOW Mechanical PTF with subtype set to ! does not produce a correctly generated EDM part_table.ptf

2672048 ADW PART_MANAGER Unable to access libraries from Pulse intermittently with no known sequence of reproducible steps

2621627 ALLEGROX FLOORPLANNER System Capture crashes when board is opened in Allegro PCB Editor and viewer

2647514 ALLEGRO_EDITOR COLOR Productize Shape Visibility through Color/Visibility dialog

2531489 ALLEGRO_EDITOR CROSS_SECTION Issue in Cross-section filter: Cannot see Dielectric without enabling Dielectric and Die Stack in Available Filter

2550355 ALLEGRO_EDITOR CROSS_SECTION Stackup/xsection image export has unreadable text

2655430 ALLEGRO_EDITOR DATABASE Replacing the padstack requires manual purge

2660920 ALLEGRO_EDITOR DATABASE axlImportXmlDBRecords() changes the default color settings

2664465 ALLEGRO_EDITOR DATABASE Replaced padstacks are not purged automatically in release 17.4-2019

2649764 ALLEGRO_EDITOR DFM DFM soldermask sliver calculation not considering vias being inside pad for DRC generation

2651702 ALLEGRO_EDITOR DFM DFM Same net uvia hole to uvia hole creates false DRCs if via is mirrored

2628597 ALLEGRO_EDITOR DRC_CONSTR The result of "Filter text

2651680 ALLEGRO_EDITOR GRAPHICS Allegro PCB Editor, release 17.4-2019 Infinite Cursor white ghost text issue: White text box attached to cursor

2660378 ALLEGRO_EDITOR GRAPHICS Release 17.4-2019 GPU plugin opacity issue on assigning color to symbol: Copper feature invisible within shape

2667883 ALLEGRO_EDITOR GRAPHICS GPU: Visibility of filled rectangles are different from shapes

2667953 ALLEGRO_EDITOR GRAPHICS Glitched cursor when configuring "Infinite Cursor"

2649703 ALLEGRO_EDITOR INTERACTIV Replace Via with Structure overlaps routes and corrupts database when structure is on right side of vertical structure

2647087 ALLEGRO_EDITOR IN_DESIGN_ANA Net Name in Vision Control dialog table not reported when a through device is used.

2647821 ALLEGRO_EDITOR IN_DESIGN_ANA Layers enabled in visibility tab are reset after IR drop is re-simulated.

2580540 ALLEGRO_EDITOR MCAD_COLLAB 'idxHolePadstackMapping.txt' file is not considered when "Select All" is selected in IDX Flow Manager Import form

2664925 ALLEGRO_EDITOR MODULES Place > Manual - Module definition crashes the tool

2665480 ALLEGRO_EDITOR MODULES The program crashes when running the Fab Panelization tool command

2660874 ALLEGRO_EDITOR MULTI_USER Error regarding undefined function - axlMUIsMultiUser on using SKILL file

2648344 ALLEGRO_EDITOR OTHER Import Logo needs to be revised such that the bmp can be put on ANY class/subclass a user chooses

2662652 ALLEGRO_EDITOR OTHER Degree circle in dimension will not move with degree.

2489008 ALLEGRO_EDITOR PLACEMENT Symbol text overlaps components on refreshing after rotating a placed module

2615648 ALLEGRO_EDITOR PLACEMENT Ratsnest visibility not same in release 17.4-2019 and release 17.2-2016 of Allegro PCB Editor

2640507 ALLEGRO_EDITOR PLACEMENT Ratsnest not displayed in Place Components Manually in release 17.4-2019

2681593 ALLEGRO_EDITOR PLACEMENT Ratsnet not displayed in Place Components Manually in release 17.4-2019

2681645 ALLEGRO_EDITOR PLACEMENT Ratsnests do not appear when placing components manually

2599650 ALLEGRO_EDITOR PORTING WM_COPYDATA not working in release 17.4-2019

2653527 ALLEGRO_EDITOR PORTING WM_COPYDATA is not working in release 17.4-2019

2666117 ALLEGRO_EDITOR PORTING Allegro PCB Editor does not respond to WM_COPYDATA(SendMessage) messages in release 17.4-2019

2646063 ALLEGRO_EDITOR SHAPE Min Aperture for gap width does not seem to work for the attached board

2647991 ALLEGRO_EDITOR SHAPE Teardrop close to boundary causes incorrect evaluation of Shape

2642367 ALLEGRO_EDITOR TECHFILE Difference report cannot be generated when importing .tcf file

2607638 ALLEGRO_EDITOR UI_FORMS "IDF Out Filter Setup" window small and not resizable

2645229 ALLEGRO_EDITOR UI_FORMS Searching the word 'step' in the User Preferences Editor crashes Allegro PCB Editor

2652396 ALLEGRO_EDITOR UI_FORMS idfout_filter.form enhancement request: Cannot resize

2659362 ALLEGRO_EDITOR UI_FORMS PCB Editor is crashing on searching for "Step" in User Preferences

2668427 ALLEGRO_EDITOR UI_FORMS Searching the word 'step' in the User Preferences Editor crashes Allegro PCB Editor

2658226 ALLEGRO_EDITOR UI_GENERAL Bug in Find panel with OrCAD Sigrity ERC license: Display -> Windows does not display the panel

2629652 APD CROSS_SECTION Cross-section Editor changes material when clicking on material name

2649896 APD DATABASE Redundant cline to dangling Cline

2657279 APD DEGASSING Strange (AREF) shape degassing: Hole created along shape boundary and degassing has opposite tone

2664829 APD DRC_CONSTRAIN Minimum Aperture For Gap Width is not honored

2665732 APD DRC_CONSTRAIN No DRCs reported when CSet is assigned to layer sets

2628970 APD EDIT_ETCH Route > Daisy Chain fails to connect neighboring pins in certain cases

2650356 APD GRAPHICS GPU: Opening design takes up to 4 minutes when GPU is active

2647547 APD REPORTS Stacked Via Report fails with error message regarding incompatible data

2642730 APD WLP WLP: pin replacement fails to have the corresponding pin extension

2650718 APD WLP WLP: ripped up structures unexpectedly come back

2657264 APD WLP Application stops responding on doing Advance Metal Fill with a specific metal fill clearance value

2666773 APD WLP Power Delivery Rail Via Generator generates columns and rows as X-1 vs input values

2662590 CONCEPT_HDL CAEVIEWS Compilation error for Caeviews HDL on Windows in release 17.4-2019

2568360 CONSTRAINT_MGR UI_FORMS Toolbar should report "not fully routed" for unrouted net when hovering over yellow Actual/Margin cells - Rel Prop Delay

2626371 CONSTRAINT_MGR UI_FORMS Double-clicking the column header sorts the column

2027407 ORBITIO GUI Interface popup list not sorted alphabetically in Select Interface form

2656144 ORBITIO GUI System Planner error message not clear when display is not set

2646990 ORBITIO INTEGRITY_IF Bump locations go wrong after push_to_planner without "-reset" option

2650662 ORBITIO IO_FLOORPLAN Check order does not work if a comment is put in TermNumber

2651329 ORBITIO IO_FLOORPLAN Select icon in IO Info Table should redraw main GUI

2653383 ORBITIO IO_FLOORPLAN Check Order should describe correct Integrity-3DIC version instead of OrbitIO version

2641279 ORBITIO OTHER Data in IO Info Table is cleared by create_contacts command

2540463 PCB_LIBRARIAN SYMBOL_EDITOR Zoom Fit is not working in Symbol Editor when opening the table view.

2672315 PCB_LIBRARIAN SYMBOL_EDITOR Pin number and pintext position not following directives on new symbols in new Symbol Editor

2655194 PSPICE ENVIRONMENT Inherit profile is broken if a large dat file is present in source profile

2488221 PSPICE MODELEDITOR Model Editor cannot open history files and displays a crash message though there is no crash

2663981 PSPICE MODELEDITOR PSpice DMI Generic VCVS C/C++ template code does not compile

2351036 PSPICE SIMULATOR Incorrect simulation results when using parameter expressions with curly braces

2527511 PSPICE SIMULATOR Error (ORPSIM-16550) displayed regarding floating point computation failure during matrix solution

2636922 PSPICE SIMULATOR Error message of DEBUG option is incorrect

2570534 PSPICE TI_OUT_OF_CON Encrypted model behaves differently

2671311 PULSE ADHOC Random System Capture Crash resulted in lost data

2663716 PULSE CORE Unexplained Pulse server outage after 99 days uptime

2649745 PULSE LIBDB_PART_UI Typo in the template for Capacitors -> Polarized Capacitor

2630240 PULSE R2PLM-WC PFM fails to publish the BOM and/or variants with 'Publish partially failed' Error.

2547586 PULSE R2PLM If one variant utility fails, all parent variant objects show failure even with successful children

2667227 PULSE R2PLM Wrong item number assigned to variant BOM when publishing PFM

2671661 PULSE R2PLM Variant details are not appearing correctly during Publish to Manufacturing

2654607 PULSE USER_MANAGEME SSO (Identity Provider) Authentication fails for restored Vista backup

2581093 RF_PCB ROUTING Allegro RF PCB 'Add connect' adds only single segment and reports SKILL error on adding RF traces with corners

2648227 RF_PCB SETUP Error reported when doing RF-PCB>Setup

2575729 SIP_LAYOUT DATABASE Netlist error on importing SIP file

2675767 SYSTEM_CAPTURE COMPONENT_BRO System Capture annotates injected properties on adding or replacing components in HotFix 030

2471089 SYSTEM_CAPTURE CONSTRAINT_MA Property defined by user as read only in CM is editable in CM docked

2640904 SYSTEM_CAPTURE EXPORT_PCB Zero pin mechanical components get assigned duplicate reference designators

2644139 SYSTEM_CAPTURE EXPORT_PCB Copy pasting the symbol (part_line_item) does not assign a unique reference designator

2518595 SYSTEM_CAPTURE FIND_REPLACE Changing symbol version of placed part does not update the text associated with the part

2664942 SYSTEM_CAPTURE FIND_REPLACE Relative property position is not retained on switching symbol version in System Capture

2648020 SYSTEM_CAPTURE HSS_SYMBOLEDI DSCS-1 port pin mismatch violation cannot be resolved

2656076 SYSTEM_CAPTURE IFF_IMPORT IFF import in System Capture gives faulty schematic

2513965 SYSTEM_CAPTURE IMPORT_BLOCK DE-HDL callout files not transferred during System Capture conversion

2595410 SYSTEM_CAPTURE IMPORT_BLOCK System Capture CopyAs giving incorrect results

2605425 SYSTEM_CAPTURE IMPORT_BLOCK "File > Copy Project As" does not use the new design name

2658886 SYSTEM_CAPTURE IMPORT_BLOCK TOC symbol coming from DE-HDL not getting detected and deleted

2684108 SYSTEM_CAPTURE IMPORT_BLOCK converting a DE-HDL project creates an empty folder.

2656295 SYSTEM_CAPTURE IMPORT_DEHDL_ Japanese Notes in page border of DE-HDL get garbled in System Capture

2608156 SYSTEM_CAPTURE MENUS_AND_TOO Save and Save As are greyed out in the File menu

2657604 SYSTEM_CAPTURE MENUS_AND_TOO 'Save All' has to be used as 'Save' and 'Save As' are greyed in the File menu

2554984 SYSTEM_CAPTURE NEW_PROJECT Warning detected if relative path is used in PPT directive for referring ptf file

2515523 SYSTEM_CAPTURE NOTES Need to validate Notes input for illegal characters

2627769 SYSTEM_CAPTURE PACKAGER Changing reuse instance name of block with Top changes all instance names

2634086 SYSTEM_CAPTURE PACKAGER System Capture does not give error when two-package symbol is placed three times

2634514 SYSTEM_CAPTURE PART_MANAGER Unable to sync the parts from Part Manager

2466085 SYSTEM_CAPTURE PROPERTY_EDIT System Capture: Cannot add VOLTAGE property to signal

2601899 SYSTEM_CAPTURE PROPERTY_EDIT System Capture differentiates between 0V and 0 V

2654098 SYSTEM_CAPTURE PROPERTY_EDIT Alignment/Superscript/Subscript warning appears when setting default text attributes for properties

2637910 SYSTEM_CAPTURE REPLACE The replace component when executed from the find results does not show selected component information

2585561 SYSTEM_CAPTURE REPORTS ::sdaReports::netToCompList from command line encounters error

2654088 SYSTEM_CAPTURE SMART_PDF Print to SmartPDF treated as change to design for Save

2602467 SYSTEM_CAPTURE SPECIAL SYMBO Special Symbols placing the wrong symbol when selected

2604331 SYSTEM_CAPTURE TABLE Headers are wrapped in autofit tables in System Capture

2659496 SYSTEM_CAPTURE TABLE MMB panning does not work when cursor is inside a table

2662418 SYSTEM_CAPTURE TABLE Allow copying read-only text in System Capture

2522067 SYSTEM_CAPTURE TABLE_OF_CONT TOC color/style is reset on running 'reevaluateTOC'

2501880 SYSTEM_CAPTURE UI The image aspect ratio gets altered even though it is locked

2545967 SYSTEM_CAPTURE UI Properties are moved on toggling visibility

2613795 SYSTEM_CAPTURE UI System Capture window changes display size after running the syscap command.

2640195 SYSTEM_CAPTURE UI Mouse pointer not visible in dark/black theme under certain selections

2653029 SYSTEM_CAPTURE UI Changing the visibility of a property value causes it to change position.

2673056 SYSTEM_CAPTURE UI Tcl API incorrectly interacting with the page navigation widget in HotFix 030

2495455 SYSTEM_CAPTURE WIRING Adding wire into bus shifts the text off the line.

2608920 SYSTEM_CAPTURE WIRING Net names duplicated on copying circuit with visible system generated net names

2673797 SYSTEM_CAPTURE WIRING Unable to delete symbol or connect NC symbol to existing pins

2654698 SYSTEM_CAPTURE WORKSPACE Floating panels have to be reopened every time System Capture is started

2572529 SYSTEM_DESIGN SDE_SUBSYSTEM EXTERNAL_ALLEGRO_BOARD_FOLDER does not resolve ^design_name^

2581309 SYS_RELIABILITY DEVICE_CONFIG Stress Analysis ignores dual diodes in System Capture

2651502 SYS_RELIABILITY DEVICE_CONFIG BAV99 diode is not categorized a diode in stress analysis

2617090 SYS_RELIABILITY ELEC_STRESS_D Red chart bar of Stress Analysis disappears when clicked

2640940 SYS_RELIABILITY SCH_AUDIT_SET Schematic Audit CPM setting in SITE being overwritten by default

2652248 TOPXP ALLEGRO_INTEG View topology error for nets names with the special character "." in Aurora II

2664988 TOPXP CHANNEL_SIMUL Topology Workbench gives incorrect DDR channel simulation results for sinusoidal jitter of 150MHz

2652331 TOPXP SYSTEMSI Topology Workbench sub-circuit cannot read dollar sign

Cadence Allegro PCB Design helps bring your innovative and bleeding-edge designs to life. The constraint-driven environment provides real-time visual feedback and ensures the functionality and manufacturability of your PCBs while allowing you to keep designing.

Cadence OrCAD is a driving force in the PCB design industry. In order to help desingers keep up with the constant pace of change Cadence has been accelerating the pace of innovation delivering a stream of updates and product enhancements to users. OrCAD provides insight into industry-first capabilities made available to customers such as real-time design, DesignTrue DFM, constraint manager, in-design analysis, and more.

Cadence OrCAD and Allegro 17.4-2019 is a sleeker and more modern version of the OrCAD and Allegro release, with enhanced usability and a slew of new productivity- enhancing features. You get more intuitive and easy- to- use flows that enable optimized schematic- to- board- to- manufacturing transitions. So, whether you design schematics, work with physical layouts, manage or create libraries and parts, or administer ECAD processes, there are features in this release that will benefit you.

Mar 31, 2022 · The Cadence released HotFix 028 (QIR4, indicated as 2022 in the application splash screens) for OrCAD and Allegro.

Tutorial OrCAD and Cadence Allegro PCB Editor | 2022 | Step by Step | For Beginners

After this tutorial you will know how to start designing your own boards in Cadence OrCAD and Allegro 17.4 . For everyone who would like to learn Allegro Design Entry CIS and Allegro PCB Editor and also for everyone who has never ever designed any boards, but would like to learn how to do it. Enjoy!

Cadence enables global electronic design innovation and plays an essential role in the creation of today’s integrated circuits and electronics. Customers use Cadence software, hardware, IP and services to design and verify advanced semiconductors, consumer electronics, networking and telecommunications equipment, and computer systems. The company is headquartered in San Jose, Calif., with sales offices, design centers and research facilities around the world to serve the global electronics industry.

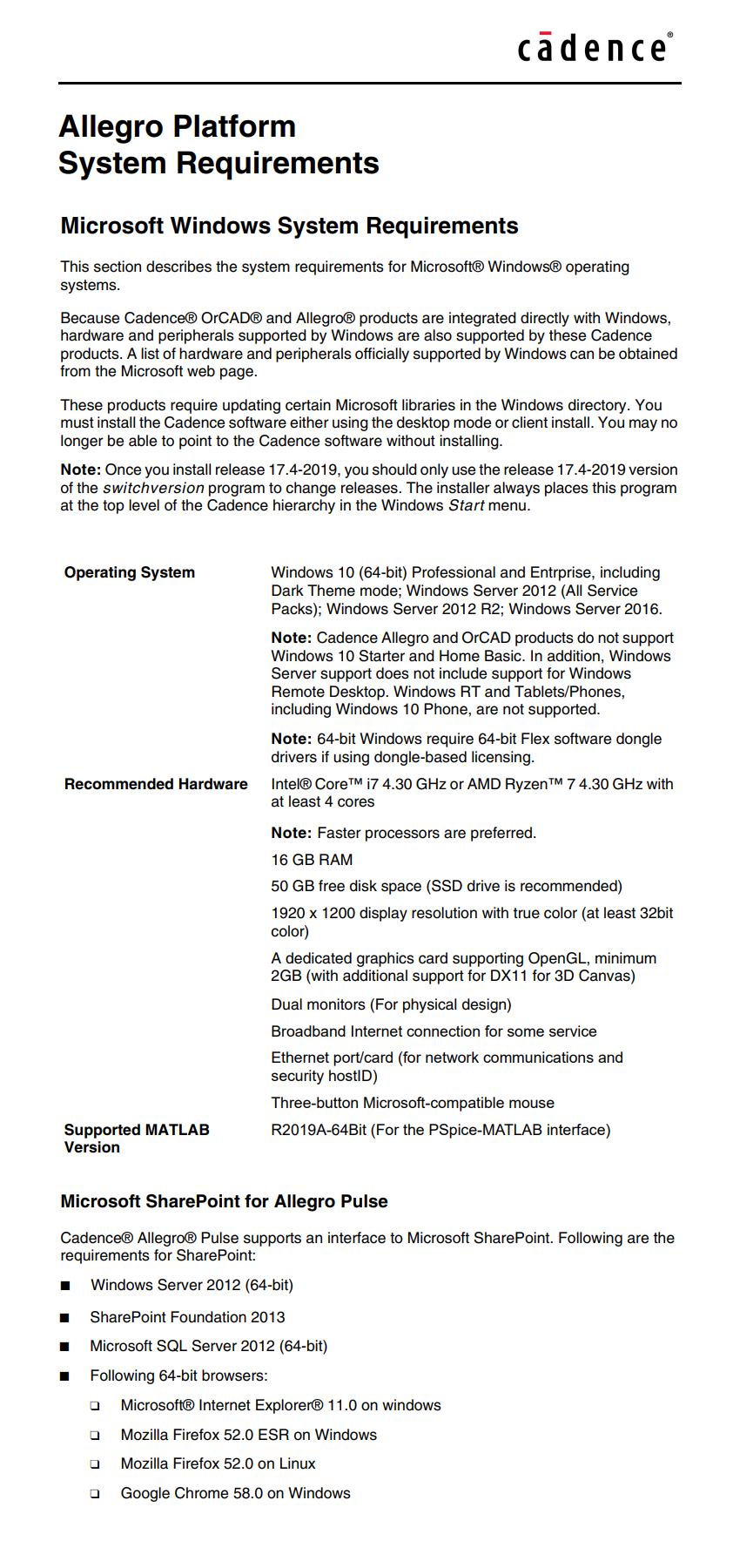

Product: Cadence SPB Allegro and OrCAD

Version: 17.40.031-2022 Hotfix Only

Supported Architectures: x64

Website Home Page : www.cadence.com

Languages Supported: english

System Requirements: Windows *

Software Prerequisites: Cadence SPB Allegro and OrCAD 17.40.000-2019 and above

Size: 7.3 Gb

Cadence SPB Allegro and OrCAD 17.40.000-2019

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please