Asic Flow & Digital Design And Verification Using Verilog

Published 11/2024

MP4 | Video: h264, 1920x1080 | Audio: AAC, 44.1 KHz

Language: English | Size: 8.87 GB | Duration: 15h 58m

Published 11/2024

MP4 | Video: h264, 1920x1080 | Audio: AAC, 44.1 KHz

Language: English | Size: 8.87 GB | Duration: 15h 58m

ASIC Flow, Verilog Language, Digital Fundamentals, Combinational circuits, Sequential circuits, APB Protocol

What you'll learn

ASIC Flow

Digital Fundamentals

Verilog constructs for design

Verilog constructs for verification

Memory design and verification

APB protocol learning

Requirements

Basics of Electronics

Linux commands

Description

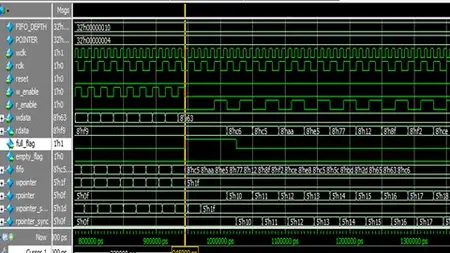

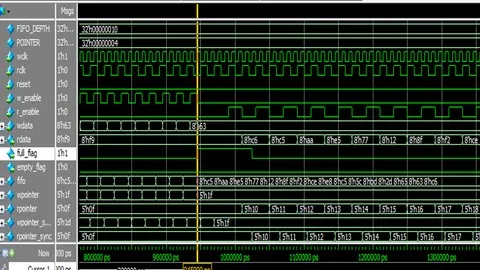

The course basically for beginners to expert level in VLSI. The course covers in details about ASIC Flow, Verilog Language, Digital Fundamentals, Combinational circuits, Sequential circuits, APB Protocol. It has 9 videos each more than 1 hr, with theory explanation and the hands on program execution. Cadence Xcelium simulator used for Verilog program execution in linux Environment. The programs are edited in vi editor.The following are the course topics: Session 1: ASIC Flow - Architecture, Design, RTL coding, Verification, DFT overviewSession 2: Synthesis, Static Timing Analysis, Physical Design, FPGA Emulation overview, Digital fundamentalsSession 3: Hardware modeling using VerilogSession 4: Verilog Program Structure Session 5 : Verilog Language constructsSession 6: Combinational circuit design and verification using VerilogSession 7: Sequential circuit design and verification using VerilogSession 8: Timing and Event schedulingSession 9: Projects : Memory design, FIFO and codes and simulationsThis course is very good for those wants to do internship, want to learn and start career in VLSI. This helps for acquiring domain knowledge in VLSI and seek job in this industry. These basic concepts and language helps to attend interviews.The course is designed and delivered by an ASIC Design and Verification Expert worked more than 2 decades in the Semiconductor Industry

Overview

Section 1: Introduction

Lecture 1 ASIC Flow - Architecture to DFT

Lecture 2 ASIC Flow - Synthesis to GDS II

Lecture 3 Hardware modeling using Verilog

Lecture 4 Verilog Program Structure

Lecture 5 Verilog Language constructs

Lecture 6 Combinational Circuit design and Verification using Verilog

Lecture 7 Sequential Circuit design and Verification using Verilog

Lecture 8 Timing and Event Scheduling

Lecture 9 Projects and Simulations

Lecture 10 Lab and Project Assignment

For BE/BTech/MTech ECE/EEE students - who want to do Internship,ECE/EEE Engineers seeking career in VLSI industry