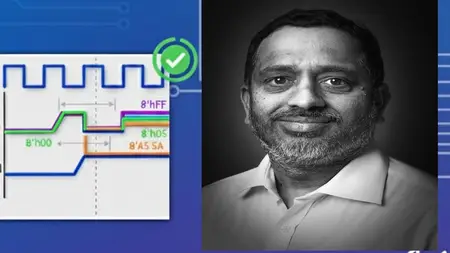

The Complete Guide to SystemVerilog Assertions (SVA)

Published 11/2025

Duration: 4h | .MP4 1920x1080 30 fps(r) | AAC, 44100 Hz, 2ch | 1.72 GB

Genre: eLearning | Language: English

Published 11/2025

Duration: 4h | .MP4 1920x1080 30 fps(r) | AAC, 44100 Hz, 2ch | 1.72 GB

Genre: eLearning | Language: English

Learn SVA coding, ABV methodology, and verification best practices with hands-on examples

What you'll learn

- Transform Your Verification Skills—Master SystemVerilog Assertions with Confidence! Understand SVA syntax, operators, and sequences to model design behavior.

- Write SystemVerilog Assertions to verify combinational and sequential logic in RTL designs with practical examples.

- Integrate assertions into simulation environments to enhance coverage, detect functional violations, and improve overall design quality.

- Apply SVA to check corner cases, enforce protocol compliance, and validate temporal relationships in digital designs.

Requirements

- Basic digital design. Good exposure to Verilog (and/or VHDL) for RTL design. No exposure to SystemVerilog, OOP, UVM needed.

Description

Unlock the Power of SystemVerilog Assertions (SVA) for ABV Mastery

Are you ready to take yourSystemVerilog testbench skillsto the next level? Whether you’re a first-time engineer or an experienced verification professional, this course will guide you from thebasics of SystemVerilog Assertions (SVA)to becoming an expert inAssertion-Based Verification (ABV). You’ll learncoding best practices, hands-on verification techniques, and how to write assertions that areboth effective and maintainable.

This is not just another SVA course — it’s apractical, real-world training experience. We emphasizecoding guidelines throughout, show you how to applyABV methodology, and provide hands-on exercises using theopen-source SVALint tool, so you can enforce high-quality assertion coding in your own projects.

What You’ll Learn

By the end of this course, you will be able to:

Writeimmediate and concurrent assertionsthat validate RTL designs effectively.

Understand and implementsequences, properties, and layered assertion architecture.

ApplyABV methodologyto real-world designs, from specification to verification.

UseSVALintto check assertion coding quality and enforce best practices.

Recognizerecurring patterns in design behaviorand implement reusable assertions.

Integrate assertions into yourUVM verification environmentusing bind files.

Graspscheduling semantics— a unique, industry-rare topic — to fully appreciate assertion behavior.

Followcoding guidelinesfor clarity, maintainability, and efficiency.

Understand the difference betweenformal, hybrid, and simulation-based verificationand when to apply each.

Build confidence in reviewing RTL with assertions and designingcorner-case tests.

Course Structure

This course is divided into10 structured sessionsthat take you step by step:

Introduction to ABV & SVA Basics– Learn why assertions are critical, their effectiveness, and how ABV fits into modern verification.

Sequences & Properties– Understand the building blocks of assertions, including Boolean expressions and temporal behavior.

Layered Architecture of SVA– Explore Boolean, temporal, and verification layers and how they provide flexibility in verification.

Assertion Planning– Learn how to create anassertion planbased on specs, interfaces, and common design patterns.

Writing Properties– Master property operators, implication, abort conditions, and advanced expression techniques.

Sequences & Delay Operators– Handle real-life timing requirements, delay operators, and how to capture contiguous and sparse patterns.

Repetition & Pattern Matching– Use SVA repetition operators to model recurring design patterns efficiently.

Integration with RTL & Bind Files– Attach assertions to your design cleanly and effectively using bind files.

Real-World Examples & Debugging– Apply assertions to practical designs, review corner cases, and enforce quality with SVALint.

Scheduling Semantics (Advanced, Unique Topic)– Understand how scheduling affects assertions, a topic rarely covered in other courses.

By the end of these sessions, you’ll have bothpractical skillsandtheoretical knowledgeto implement ABV confidently in any SystemVerilog environment.

Unique Features of This Course

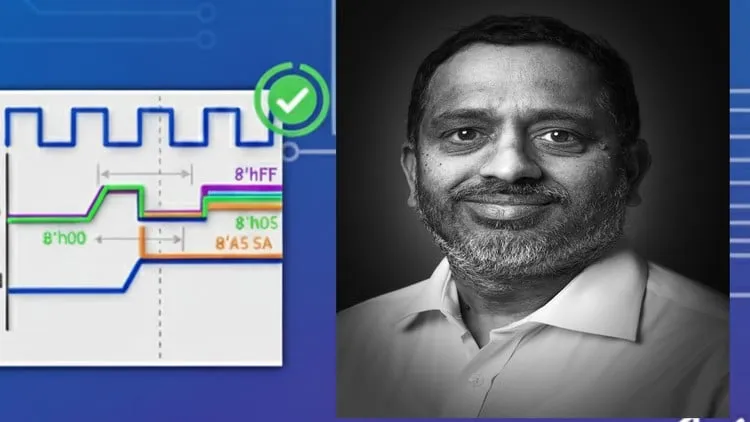

Instructor Expertise:Co-authored several books on SVA and ABV, pioneering assertion-based verification since 2003. Learn from someone with decades ofindustry and academic experience.

Hands-On Learning:Exercises and examples usingopen-source SVALint, allowing you toenforce coding standardsand write high-quality assertions.

Coding Guidelines Throughout:Every lesson emphasizesbest practices, so students developclean, maintainable, and scalable assertions.

Real-World Design Patterns:Focused onrecurring signal patterns, edge cases, and scenarios you’ll actually face in RTL verification projects.

Advanced Content:Thescheduling semantics sessiongives you insight that almost no other course provides.

Who This Course is For

This course is designed for:

First-time engineerslearning SystemVerilog assertions for the first time.

Experienced verification engineerswho want toupgrade their ABV skillsand enforce coding quality.

Designers and RTL engineerswho want to learn how assertions can helpcatch bugs early.

Anyone looking to understandABV methodology,coding guidelines, andtool-assisted verification.

Requirements

Basic knowledge ofSystemVerilogor experience with atestbench environment.

Familiarity withRTL design conceptsis helpful but not mandatory.

Access to acomputer for hands-on practice. The course includes all code examples andSVALint setup instructions.

Why You Should Take This Course

Learnfrom an industry pioneerwith decades of ABV experience.

Gainpractical skills and hands-on exercisesthat you can immediately apply at work.

Buildquality enforcement habitsusing coding guidelines and tools.

Understandadvanced conceptslike scheduling semantics, giving you an edge over other engineers.

Complete afull ABV learning journeyfrom sequences and properties to real-world verification and debugging.

By the end of this course, you won’t just knowwhat SVA is— you’ll knowhow to use it effectively, write maintainable assertions, andverify RTL like a pro.

Who this course is for:

- If you’re eager to learn how to write, understand, and apply SystemVerilog Assertions, this course is for you!

- Verification Engineers: Professionals looking to enhance their skills by mastering SystemVerilog Assertions to verify complex designs efficiently.

- Design Engineers: RTL designers aiming to integrate assertions into their workflows to ensure robust and error-free designs.

- Project Managers and Leads: Leaders seeking a high-level understanding of SVA to better manage design and verification projects.

- Students and Enthusiasts: Aspiring engineers and learners passionate about digital design who wish to strengthen their verification fundamentals.

More Info