VSD - Static Timing Analysis - II

Duration: 4h 1m | .MP4 1280x720, 25 fps(r) | AAC, 48000 Hz, 2ch | 589 MB

Genre: eLearning | Language: English

Duration: 4h 1m | .MP4 1280x720, 25 fps(r) | AAC, 48000 Hz, 2ch | 589 MB

Genre: eLearning | Language: English

VLSI - Analyse your chip timing for free

What you'll learn

Students will be able to do a real full chip static timing analysis with $0 spent, as designs and tools used in this course are opensource

Students will be able to appreciate power of opensource EDA tools, like Opentimer used in this course, and help in contributing towards the development of this tool

Requirements

Static Timing analysis - part 1 course needs to be fully completed to start this course. No exceptions

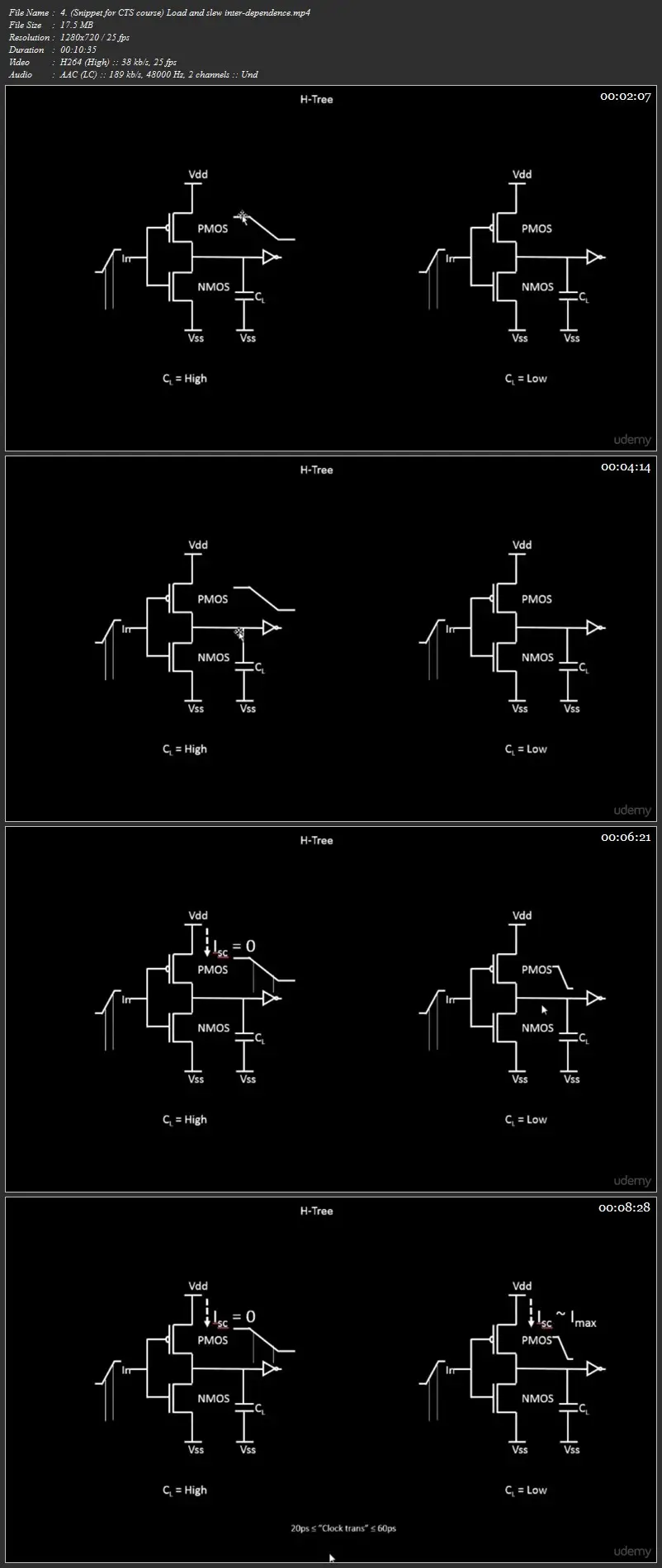

Knowledge of physical design flow and clock tree synthesis will be helpful

Description

In static timing analysis - part 1 course, we introduced you to basic and essential timing checks, like cppr, gba, pba, etc. In this course, we are focusing on application of these concepts on real chip using opensource sta tool called 'Opentimer'. There is an amount of homework needed to make this tool work, but you know what, looking and feeling the power of this opensource tool, you will find the effort is worth taking

Why its worth? Because, you can now analyze your chip at $0 right from your home. Isn't that FREEdom that we have been looking for? In my advanced courses, including this one, the prime focus is on how to analyze complex chips like USB controller or DDR using Opentimer.

Opentimer has been developed by Tsung-Wei Huang and Prof. Martin D. F. Wong in the University of Illinios at Urbana-Champaign (UIUC), IL, USA. It supports important features like PBA, CPPR, block based analysis, and many more.

I am using this tool in this course for explaining the concepts from STA-part 1 and also for some interface analysis that we will be looking in this course.

So, hope you enjoy learning this course in the same way we enjoyed making them.

Who this course is for:

Anyone who has completed static timing analysis - part 1 course

Anyone (with 100% static timing analysis - part 1 course completed) who has basic knowledge on flipflops, gates and digital logic

More Info