Verilog Hdl: Vlsi Hardware Design Comprehensive Masterclass

Last updated 10/2022

MP4 | Video: h264, 1280x720 | Audio: AAC, 44.1 KHz

Language: English | Size: 2.48 GB | Duration: 12h 37m

Last updated 10/2022

MP4 | Video: h264, 1280x720 | Audio: AAC, 44.1 KHz

Language: English | Size: 2.48 GB | Duration: 12h 37m

From an expert with 15+ years experience. Core Design principles for VLSI, Soc, Processor and FPGA. VHDL alternative.

What you'll learn

Unlimited instructor support !

Application Specific Integrated Circuit (ASIC) design flow and its related fundamentals

Learn more than enough to start designing real life circuits using HDL

Have a clear understanding of how to and how not to write a piece of HDL code

The close relationship between hardware and code

From basics to key principles for design engineers

A detailed discussion on every bit of code and hardware

Requirements

Mandatory: A passion to learn and practice regularly and systematically

Basics of Digital Logic Design

Fundamentals of VLSI

Optional: Any coding experience shall help although not necessary

Computer architecture

Description

A job oriented exhaustive course on logic design for hardware using the Verilog Hardware Description Language. Unique, tested and proven structured style and approach followed.Thoughtful blend of theory and practice for your learning.Unlimited support with the instructor.Understand all the intricate details in thinking and understanding hardware design.Principles are reinforced with multiple examples.Good coding guidelines and bad examples to avoid.After completing the course, you can confidently write synthesizable code for complex hardware design.Thorough discussion of every hardware component design.Detailed explanation of the relationship between code and digital hardware units.Freely download 100+ code examples and test benches used in the course.Access to all the materials and the future upgrades.Loads to quizzes and assignments to check your understanding.Work through the lessons at your own pace.

Overview

Section 1: Introduction

Lecture 1 Introduction

Lecture 2 Course coverage

Lecture 3 Review of VLSI concepts

Lecture 4 Quick CMOS basics (added as per request)

Lecture 5 What is VLSI?

Lecture 6 Review of terms

Lecture 7 Minimum feature size

Lecture 8 Why Integration?

Lecture 9 Broad areas in VLSI

Lecture 10 VLSI Design Styles - Full Custom

Lecture 11 VLSI Design Styles - Semi Custom

Lecture 12 VLSI Design Styles - FPGA

Lecture 13 VLSI Design Styles - Gate Array

Lecture 14 VLSI Design Styles - Comparison

Lecture 15 Full custom vs Semi custom

Lecture 16 ASIC vs FPGA

Lecture 17 ASIC Design Flow - Part 1

Lecture 18 ASIC Design Flow - Part 2

Lecture 19 ASIC Design Flow - Design Specs

Lecture 20 ASIC Design Flow - Architecturing

Lecture 21 ASIC Design Flow - RTL coding

Lecture 22 ASIC Design Flow - Verification

Lecture 23 ASIC Design Flow - Synthesis

Lecture 24 ASIC Design Flow - Design for Testability

Lecture 25 ASIC Design Flow - Timing Analysis

Lecture 26 ASIC Design Flow - Floorplanning, Placement & Routing

Lecture 27 ASIC Design Flow - Formal Verification

Lecture 28 ASIC Design Flow - Power Estimation

Lecture 29 ASIC Design Flow - Fabrication

Lecture 30 ASIC Design Flow - Packaging

Section 2: Verilog Basics

Lecture 31 Verilog Design Styles

Lecture 32 My First Dataflow Style Design

Lecture 33 My First Behavioral Style Design

Lecture 34 My First Structural Style Design

Lecture 35 1-bit Full Adder (Sturctural-1)

Lecture 36 1-bit Full Adder (Sturctural-2)

Lecture 37 1-bit Full Adder (Sturctural-3)

Lecture 38 1-bit Full Adder (Dataflow)

Lecture 39 1-bit Full Adder (Behavioral)

Lecture 40 My first Test Bench

Section 3: Designing Combinational Logic

Lecture 41 4 Valued Logic

Lecture 42 Data Types

Lecture 43 Number Representation

Lecture 44 Bit and Bus

Lecture 45 Naming Conventions

Lecture 46 Operators - Bitwise

Lecture 47 Operators - Arithmetic

Lecture 48 Operators - Logical

Lecture 49 Operators - Relational

Lecture 50 Operators - Reduction

Lecture 51 Operators - Shift

Lecture 52 Operators - Concatenation

Lecture 53 Operators - Repetition

Lecture 54 Operators - Conditional

Lecture 55 Output Resolution Table

Lecture 56 4-bit Full Adder (Structural)

Lecture 57 4-bit Full Adder (Dataflow)

Lecture 58 4-bit Full Adder (Behavioral)

Lecture 59 4-bit Full Adder Test Bench

Lecture 60 2:1 Multiplexer (Dataflow)

Lecture 61 2:1 Multiplexer (Behavioral)

Lecture 62 4:1 Multiplexer (Dataflow1)

Lecture 63 4:1 Multiplexer (Dataflow2)

Lecture 64 4:1 Multiplexer (Dataflow3)

Lecture 65 4:1 Multiplexer (Behavioral)

Lecture 66 2 X 4 Decoder (Dataflow)

Lecture 67 2 X 4 Decoder (Behavioral)

Lecture 68 3 X 8 Decoder (Dataflow)

Lecture 69 4 X 2 Encoder (Dataflow)

Lecture 70 4 X 2 Encoder (Behavioral)

Lecture 71 4 X 2 Priority Encoder (Behavioral)

Lecture 72 4 X 2 Priority Encoder (Dataflow)

Lecture 73 4-bit Comparator (Dataflow 1)

Lecture 74 4-bit Comparator (Dataflow 2)

Lecture 75 4-bit Comparator (Behavioral)

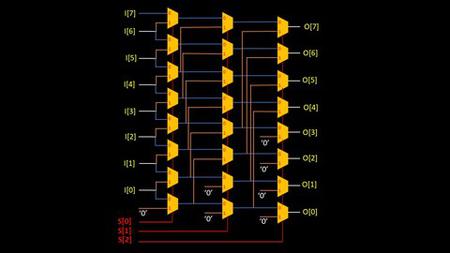

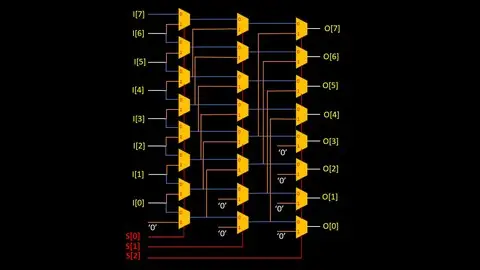

Lecture 76 8-bit Barrel Shifter (Combinational Left & Right)

Lecture 77 Designing Arithmetic & Logic Unit (ALU)

Section 4: Designing Sequential Logic

Lecture 78 Clock, D-Latch and a D-Flip Flop

Lecture 79 D-Flip Flop vs D-Latch

Lecture 80 D-Latch (Dataflow)

Lecture 81 D-Latch (Behavioral)

Lecture 82 D-Latch with Asynchronous Reset (Behavioral)

Lecture 83 D-Flip Flop (Basic)

Lecture 84 Postitive Edge Triggered D-Flip Flop with Asynchronous Active High Reset

Lecture 85 Negative Edge Triggered D-Flip Flop with Asynchronous Active High Reset

Lecture 86 Postitive Edge Triggered D-Flip Flop with Asynchronous Active Low Reset

Lecture 87 Postitive Edge Triggered D-Flip Flop with Asynchronous Active High Set

Lecture 88 Synchronous D-Flip Flop with Active High Reset

Lecture 89 Synchronous D-Flip Flop with Active Low Reset

Lecture 90 Synchronous D-Flip Flop with Reset and Set

Lecture 91 Synchronous and Asynchronous Reset Design

Lecture 92 8-bit Twin Register Set

Lecture 93 Designing a 5-bit Left to Right Shift Register

Lecture 94 Designing a 5-bit Universal Shift Register

Lecture 95 Designing a basic counter

Lecture 96 Writing a Test Bench for a Counter

Lecture 97 Designing an Up Counter with Load Option

Lecture 98 Designing an Up or Down Counter

Lecture 99 Designing a Modulus Counter

Lecture 100 Designing a Range Up Counter

Lecture 101 Designing a Range Up or Down Counter with Load Option

Lecture 102 Designing a Clock Frequency Divider (Divide by 2)

Lecture 103 Designing a Clock Frequency Divider (Divide by 4)

Lecture 104 Designing a Clock Frequency Divider (Divide by 3)

Lecture 105 Designing a Single Clock First In First Out (FIFO)

Lecture 106 Designing a Dual Clock First In First Out (FIFO)

Section 5: Designing Memories

Lecture 107 Memory Array Options and Definitions

Lecture 108 Single Port Ram - v1

Lecture 109 Single Port Ram - v2

Lecture 110 Single Port Ram - v3

Lecture 111 Single Port Ram - v4

Lecture 112 Dual Port Ram - v1

Lecture 113 Dual Port Ram - v2

Lecture 114 True Dual Port Ram - v1

Lecture 115 True Dual Port Ram - v2

Section 6: Designing Finite State Machines

Lecture 116 Mealy vs Moore Machine

Lecture 117 Mealy - 101 Non-Overlapping Sequence Detector

Lecture 118 Mealy - 011 Non-Overlapping Sequence Detector

Lecture 119 Mealy - 000 Non-Overlapping Sequence Detector

Lecture 120 Mealy - 0101 Non-Overlapping Sequence Detector

Lecture 121 Mealy - 11011 Non-Overlapping Sequence Detector

Lecture 122 Mealy - 101 Overlapping Sequence Detector

Lecture 123 Mealy - 011 Overlapping Sequence Detector

Lecture 124 Mealy - 000 Overlapping Sequence Detector

Lecture 125 Mealy - 0101 Overlapping Sequence Detector

Lecture 126 Mealy - 11011 Overlapping Sequence Detector

Lecture 127 Designing a Mealy Machine - Sequence Detector

Lecture 128 Moore - 101 Non-Overlapping Sequence Detector

Lecture 129 Moore - 010 Non-Overlapping Sequence Detector

Lecture 130 Moore - 0101 Non-Overlapping Sequence Detector

Lecture 131 Moore - 101 Overlapping Sequence Detector

Lecture 132 Moore - 010 Overlapping Sequence Detector

Lecture 133 Moore - 0101 Overlapping Sequence Detector

Lecture 134 Designing a Moore Machine - Sequence Detector

Lecture 135 Designing a Machine to Pick a Series of Coloured Balls and a Vending Machine

A beginner or an intermediate - eager to grasp and understand Hardware Design concepts with HDL,Anyone aspiring to build a career in VLSI Circuit Design,If you are in the industry and would like to sharpen your skills and clarify your understanding